You also want an ePaper? Increase the reach of your titles

YUMPU automatically turns print PDFs into web optimized ePapers that Google loves.

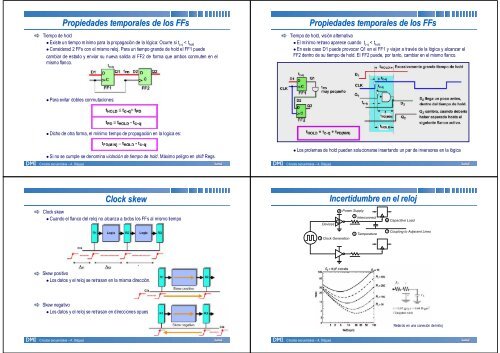

Tiempo de hold<br />

DMI C ircuitos sec uenciales – A. Diéguez<br />

Propiedades temporales de los FFs<br />

Existe un tiempo m ínimo para la propagación de la lógica: Ocurre si t c-q < t hold<br />

Considerad 2 FFs con el mismo reloj. Para un tiempo grande de hold el FF1 puede<br />

cambiar de estado y enviar su nueva salida al FF2 de forma que ambos conmuten en el<br />

mismo flanco.<br />

Para evitar dobles conmutaciones:<br />

Dicho de otra forma, el mínimo tiempo de propagación en la logica es:<br />

Si no se cumple se denomina violación de tiempo de hold. Máximo peligro en shift Regs.<br />

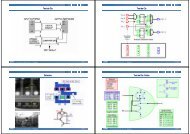

Clock skew<br />

DMI C ircuitos sec uenciales – A. Diéguez<br />

Clock skew<br />

Cuando el flanco del reloj no alcanza a todos los FFs al mismo tiempo<br />

Skew positivo<br />

Los datos y el reloj se retrasan en la misma dirección.<br />

Skew negativo<br />

Los datos y el reloj se retrasan en direcciones opuestas<br />

DMI C ircuitos sec uenciales – A. Diéguez<br />

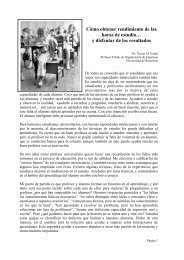

Propiedades temporales de los FFs<br />

Tiempo de hold, visión alternativa<br />

El mínimo retraso aparece cuando t c-q < t hold<br />

En este caso D1 puede provocar Q1 en el FF1 y viajar a través de la lógica y alcanzar el<br />

FF2 dentro de su tiempo de hold. El FF2 puede, por tanto, cambiar en el mismo flanco.<br />

Los prolemas de hold pueden solucionarse insertando un par de inversores en la lógica<br />

DMI C ircuitos sec uenciales – A. Diéguez<br />

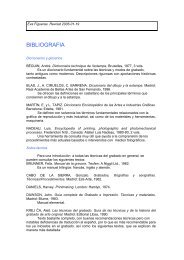

Incertidumbre en el reloj<br />

4 Power Supply<br />

3 Interconnect<br />

2<br />

Devices<br />

1 Clock Generation<br />

5 Temperature<br />

6 Capacitive Load<br />

7 Coupling to Adjacent Lines<br />

Retar do en una conex ión del reloj