You also want an ePaper? Increase the reach of your titles

YUMPU automatically turns print PDFs into web optimized ePapers that Google loves.

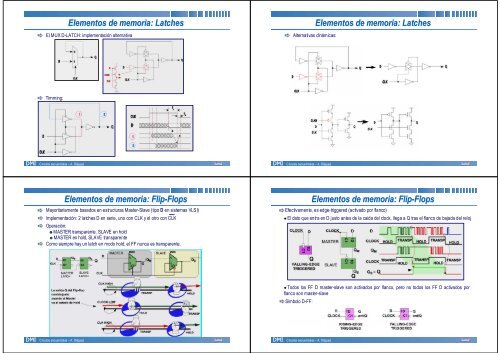

DMI C ircuitos sec uenciales – A. Diéguez<br />

Elementos de memoria: <strong>Latches</strong><br />

El MUX D-LATCH: implementación alternativa<br />

Timming:<br />

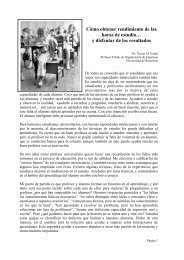

DMI C ircuitos sec uenciales – A. Diéguez<br />

Elementos de memoria: Flip-Flops<br />

Flip Flops<br />

Mayoritariamente basados en estructuras Master-Slave (tipo D en sistemas VLSI)<br />

Implementación: 2 latches D en serie, uno con CLK y el otro con CLK<br />

Operación:<br />

MASTER transparente, SLAVE en hold<br />

MASTER en hold, SLAVE transparente<br />

Como siempre hay un latch en modo hold, el FF nunca es transparente.<br />

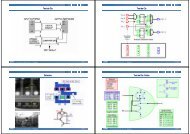

DMI C ircuitos sec uenciales – A. Diéguez<br />

Elementos de memoria: <strong>Latches</strong><br />

Alternativas dinámicas:<br />

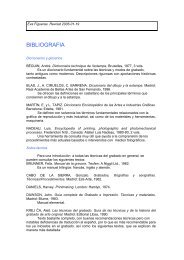

DMI C ircuitos sec uenciales – A. Diéguez<br />

Elementos de memoria: Flip-Flops<br />

Flip Flops<br />

Efectivamente, es edge-triggered (activado por flanco)<br />

El dato que entra en D justo antes de la caida del clock, llega a Q tras el flanco de bajada del reloj<br />

Todos los FF D master-slave son activados por flanco, pero no todos los FF D activados por<br />

flanco son master-slave<br />

Símbolo D-FF: