PLL - PHASE LOOP LOCKED - Lazos Enganchados en Fase

PLL - PHASE LOOP LOCKED - Lazos Enganchados en Fase

PLL - PHASE LOOP LOCKED - Lazos Enganchados en Fase

Create successful ePaper yourself

Turn your PDF publications into a flip-book with our unique Google optimized e-Paper software.

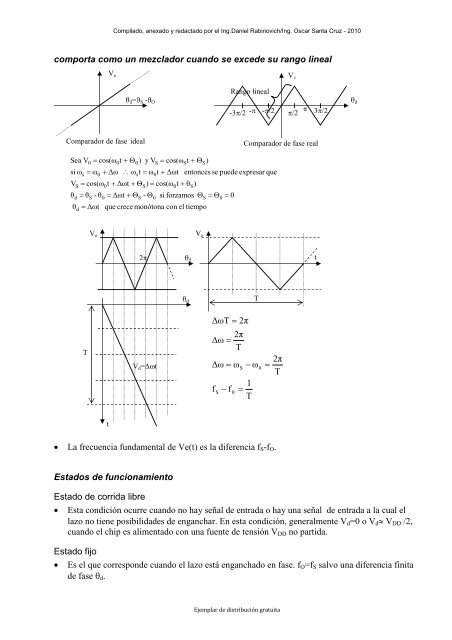

Compilado, anexado y redactado por el Ing.Daniel Rabinovich/Ing. Oscar Santa Cruz - 2010comporta como un mezclador cuando se excede su rango linealV eV e d = S - ORango lineal-3/2 --/2 /2 3/2 dComparador de fase idealComparador de fase realSea V cos(ω t si ω ωV cos(ω t Δωt Θ ) cos(ω t θ )θθSdds0 θS0- θ Δω ω t ω t Δωt0000s Δωt ) y V cos(ω t )SS- si forzamos Δωt que crece monótona con el tiempo0S00S<strong>en</strong>tonces se puede expresar queSSS 0 0V eV e2 dt dTTV d =tΔωT 2πΔω Δω ωfS f2πT0S ω1T02πTt La frecu<strong>en</strong>cia fundam<strong>en</strong>tal de Ve(t) es la difer<strong>en</strong>cia f S -f O .Estados de funcionami<strong>en</strong>toEstado de corrida libreEsta condición ocurre cuando no hay señal de <strong>en</strong>trada o hay una señal de <strong>en</strong>trada a la cual ellazo no ti<strong>en</strong>e posibilidades de <strong>en</strong>ganchar. En esta condición, g<strong>en</strong>eralm<strong>en</strong>te V d =0 o V d V DD /2,cuando el chip es alim<strong>en</strong>tado con una fu<strong>en</strong>te de t<strong>en</strong>sión V DD no partida.Estado fijoEs el que corresponde cuando el lazo está <strong>en</strong>ganchado <strong>en</strong> fase. f O =f S salvo una difer<strong>en</strong>cia finitade fase d .Ejemplar de distribución gratuita