PLL - PHASE LOOP LOCKED - Lazos Enganchados en Fase

PLL - PHASE LOOP LOCKED - Lazos Enganchados en Fase

PLL - PHASE LOOP LOCKED - Lazos Enganchados en Fase

Create successful ePaper yourself

Turn your PDF publications into a flip-book with our unique Google optimized e-Paper software.

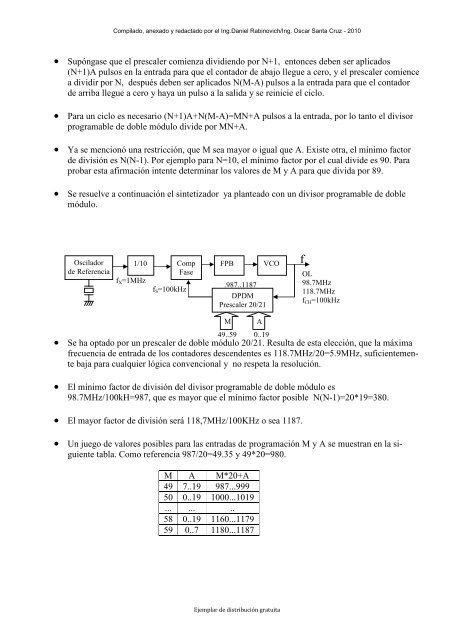

Compilado, anexado y redactado por el Ing.Daniel Rabinovich/Ing. Oscar Santa Cruz - 2010Supóngase que el prescaler comi<strong>en</strong>za dividi<strong>en</strong>do por N+1, <strong>en</strong>tonces deb<strong>en</strong> ser aplicados(N+1)A pulsos <strong>en</strong> la <strong>en</strong>trada para que el contador de abajo llegue a cero, y el prescaler comi<strong>en</strong>cea dividir por N, después deb<strong>en</strong> ser aplicados N(M-A) pulsos a la <strong>en</strong>trada para que el contadorde arriba llegue a cero y haya un pulso a la salida y se reinicie el ciclo.Para un ciclo es necesario (N+1)A+N(M-A)=MN+A pulsos a la <strong>en</strong>trada, por lo tanto el divisorprogramable de doble módulo divide por MN+A.Ya se m<strong>en</strong>cionó una restricción, que M sea mayor o igual que A. Existe otra, el mínimo factorde división es N(N-1). Por ejemplo para N=10, el mínimo factor por el cual divide es 90. Paraprobar esta afirmación int<strong>en</strong>te determinar los valores de M y A para que divida por 89.Se resuelve a continuación el sintetizador ya planteado con un divisor programable de doblemódulo.Osciladorde Refer<strong>en</strong>cia1/10f X =1MHzComp<strong>Fase</strong>f S =100kHzFPB.987..1187DPDMPrescaler 20/21VCOfOL98.7MHz118.7MHzf CH =100kHzM49..59 0..19Se ha optado por un prescaler de doble módulo 20/21. Resulta de esta elección, que la máximafrecu<strong>en</strong>cia de <strong>en</strong>trada de los contadores desc<strong>en</strong>d<strong>en</strong>tes es 118.7MHz/20=5.9MHz, sufici<strong>en</strong>tem<strong>en</strong>tebaja para cualquier lógica conv<strong>en</strong>cional y no respeta la resolución.El mínimo factor de división del divisor programable de doble módulo es98.7MHz/100kH=987, que es mayor que el mínimo factor posible N(N-1)=20*19=380.A El mayor factor de división será 118,7MHz/100KHz o sea 1187.Un juego de valores posibles para las <strong>en</strong>tradas de programación M y A se muestran <strong>en</strong> la sigui<strong>en</strong>tetabla. Como refer<strong>en</strong>cia 987/20=49.35 y 49*20=980.M A M*20+A49 7..19 987...99950 0..19 1000...1019... ... ..58 0..19 1160...117959 0..7 1180...1187Ejemplar de distribución gratuita