下载 - Xilinx

下载 - Xilinx

下载 - Xilinx

Create successful ePaper yourself

Turn your PDF publications into a flip-book with our unique Google optimized e-Paper software.

FPGA 技术是一种强大且高度灵活的 PID 控制器实<br />

现方法。由于 FPGA 器件拥有大量的并行资源,<br />

可为同步运算提供多个比例积分微分(PID)实例。<br />

此外,FPGA 还能够在不影响此前设计的其它 PID 的性能的<br />

情况下,根据应用需求,灵活添加更多 PID 环路。如果在新<br />

型赛灵思 Zynq -7000 All Programmable soC 的可编程逻<br />

辑(或架构)中实现 PID,可以获得更多新的优势,因为功能<br />

强大的板上 ARM ® Cortex 双 A9 核处理系统可以直接利用<br />

FPGA 的功能。<br />

但是,FPGA 器件一般要求使用 VHDL 或 Verilog 等寄存<br />

器传输级(RTL)设计语言,这可能与控制工程师的知识背景<br />

存在一定的差距,会妨碍 FPGA 技术的使用。为消除这种差距,<br />

赛灵思新推出 Vivado 高层次综合(HLs)设计工具。这种工<br />

具能够将 C、C++ 或 system C 设计规范转换为 RTL 实现方案,<br />

以便综合到赛灵思 FPGA 中。这种转换只需要对常见的 C 或<br />

C++ 代码稍作调整,因此不会造成严重的知识脱节。<br />

另外,近年来电气驱动器和机器人也正在设法进军联网控<br />

制系统的范畴,这类联网系统在配备有通信信道的环路中使用<br />

PID。在这类应用中,FPGA 实现的确定性和速度占巨大优势。<br />

0 0<br />

w(n)<br />

<br />

但是由于还是需要与软件通信协议栈互动,系统架构师和控制<br />

工程师往往牺牲性能来换取全软件实现。庆幸的是,Vivado 提供<br />

了一种更简单、更通用的实现方法,可避开这种取舍。Vivado 只需<br />

通过把 C 或 C++ 代码重新映射到 Zynq-7000 All Programmable<br />

soC 器件的 FPGA 架构上,就可以显著改善已开发出的联网<br />

控制系统的性能。<br />

一种无所不在的器件<br />

+<br />

+<br />

<br />

e(n)<br />

PID(z)<br />

PID<br />

<br />

基本上所有自然和人为的控制系统均采用 PID 或其变体<br />

up<br />

u<br />

lo<br />

Saturation<br />

<br />

A s k F A E - x<br />

PI(比例积分)或 PD(比例微分)来反馈。大型工厂使用成<br />

千上万的 PID 控制器来监控其化学或物理工艺。在汽车和运<br />

输系统中,PID 用于控制和保持发动机速度,确保平稳制动和<br />

控制众多转向功能;在电机中,PID 用于控制电机的电流和力<br />

矩;而在机器人中,PID 则用于驱动和稳定机器人的手臂或腿<br />

部的轨迹。PID 无处不在,就连医疗系统中也有其身影,例如<br />

用于控制 I 类糖尿患者的人工胰腺,模仿天然胰岛素分泌特征。<br />

实际上生物系统自身也使用反馈来控制刺激反应,比如说视网<br />

膜系统适应光照的过程。<br />

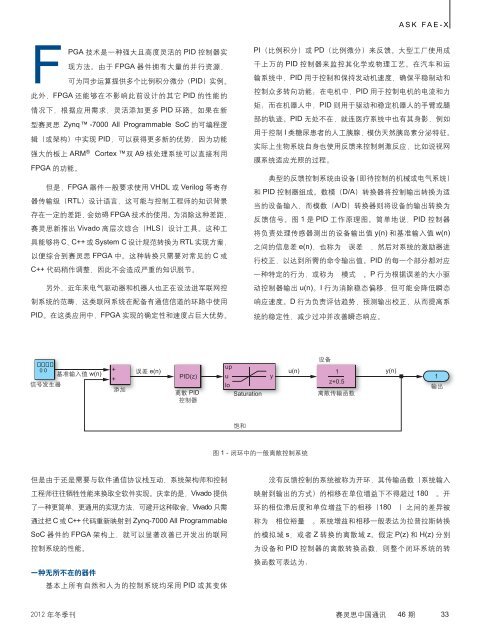

典型的反馈控制系统由设备(即待控制的机械或电气系统)<br />

和 PID 控制器组成。数模(D/A)转换器将控制输出转换为适<br />

当的设备输入,而模数(A/D)转换器则将设备的输出转换为<br />

反馈信号。图 1 是 PID 工作原理图。简单地说,PID 控制器<br />

将负责处理传感器测出的设备输出值 y(n) 和基准输入值 w(n)<br />

之间的信息差 e(n),也称为“误差”,然后对系统的激励器进<br />

行校正,以达到所需的命令输出值。PID 的每一个部分都对应<br />

一种特定的行为,或称为“模式”。P 行为根据误差的大小驱<br />

动控制器输出 u(n)。I 行为消除稳态偏移,但可能会降低瞬态<br />

响应速度。D 行为负责评估趋势,预测输出校正,从而提高系<br />

统的稳定性,减少过冲并改善瞬态响应。<br />

没有反馈控制的系统被称为开环,其传输函数(系统输入<br />

映射到输出的方式)的相移在单位增益下不得超过 180°。开<br />

环的相位滞后度和单位增益下的相移(180°)之间的差异被<br />

称为“相位裕量”。系统增益和相移一般表达为拉普拉斯转换<br />

的模拟域 s,或者 Z 转换的离散域 z。假定 P(z) 和 H(z) 分别<br />

为设备和 PID 控制器的离散转换函数,则整个闭环系统的转<br />

换函数可表达为:<br />

2012 年冬季刊 赛灵思中国通讯 46 期 33<br />

y<br />

u(n)<br />

图 1 - 闭环中的一般离散控制系统<br />

<br />

1<br />

z+0.5<br />

<br />

y(n)<br />

1