下载 - Xilinx

下载 - Xilinx

下载 - Xilinx

Create successful ePaper yourself

Turn your PDF publications into a flip-book with our unique Google optimized e-Paper software.

条件下观察并调试特定节点的电路的行为。您可将观察到的采<br />

样数据写入 VCD 文件并将其关联到 RTL。<br />

第四步:渐进性修复错误 (incremental fix)。一旦找到了错误<br />

所在,就可以通过分级、渐进式流程在 RTL 或约束中渐进地<br />

进行修复。<br />

时序和功能性错误的可视检查<br />

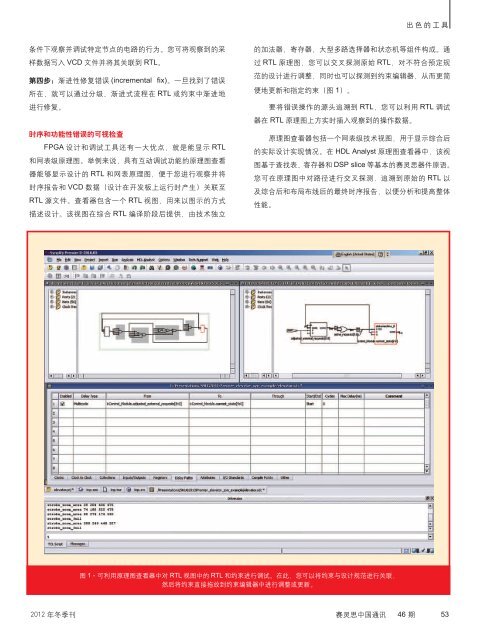

FPGA 设计和调试工具还有一大优点,就是能显示 RTL<br />

和网表级原理图。举例来说,具有互动调试功能的原理图查看<br />

器能够显示设计的 RTL 和网表原理图,便于您进行观察并将<br />

时序报告和 VCD 数据(设计在开发板上运行时产生)关联至<br />

RTL 源文件。查看器包含一个 RTL 视图,用来以图示的方式<br />

描述设计。该视图在综合 RTL 编译阶段后提供,由技术独立<br />

出 色 的 工 具<br />

的加法器、寄存器、大型多路选择器和状态机等组件构成。通<br />

过 RTL 原理图,您可以交叉探测原始 RTL,对不符合预定规<br />

范的设计进行调整,同时也可以探测到约束编辑器,从而更简<br />

便地更新和指定约束(图 1)。<br />

要将错误操作的源头追溯到 RTL,您可以利用 RTL 调试<br />

器在 RTL 原理图上方实时插入观察到的操作数据。<br />

原理图查看器包括一个网表级技术视图,用于显示综合后<br />

的实际设计实现情况。在 HDL Analyst 原理图查看器中,该视<br />

图基于查找表、寄存器和 DSP slice 等基本的赛灵思器件原语。<br />

您可在原理图中对路径进行交叉探测,追溯到原始的 RTL 以<br />

及综合后和布局布线后的最终时序报告,以便分析和提高整体<br />

性能。<br />

图 1 - 可利用原理图查看器中对 RTL 视图中的 RTL 和约束进行调试。在此,您可以将约束与设计规范进行关联,<br />

然后将约束直接拖放到约束编辑器中进行调整或更新。<br />

2012 年冬季刊 赛灵思中国通讯 46 期 53