下载 - Xilinx

下载 - Xilinx

下载 - Xilinx

You also want an ePaper? Increase the reach of your titles

YUMPU automatically turns print PDFs into web optimized ePapers that Google loves.

A s k F A E - x<br />

pid_addsub = Y1 + Y2;<br />

tmp = pid_addsub + pid_mult;<br />

tmp = (tmp > max_limU) ?<br />

max_limU : tmp;<br />

U = (tmp < min_limU) ?<br />

min_limU : tmp;<br />

// PID effective<br />

// output signal<br />

dout[0] = U;<br />

// test the PID error<br />

// signal as output<br />

dout[1] = E;<br />

// update internal states<br />

// for the next iteration<br />

prev_X1 = X1;<br />

prev_Y1 = Y1;<br />

prev_INT= INT;<br />

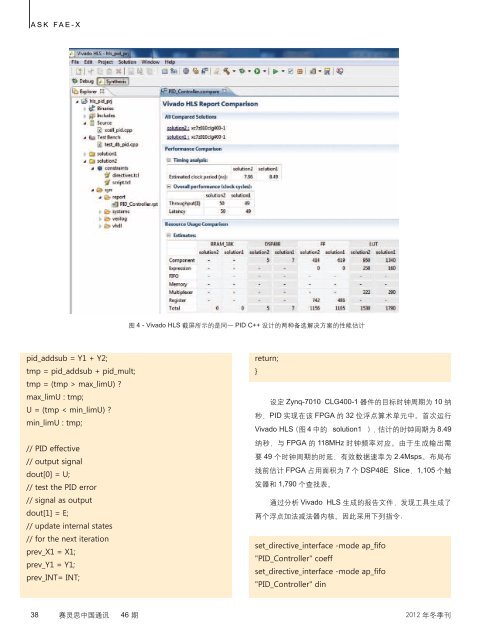

图 4 - Vivado HLs 截屏所示的是同一 PID C++ 设计的两种备选解决方案的性能估计<br />

return;<br />

}<br />

设定 Zynq-7010 CLG400-1 器件的目标时钟周期为 10 纳<br />

秒,PID 实现在该 FPGA 的 32 位浮点算术单元中。首次运行<br />

Vivado HLs(图 4 中的“solution1”),估计的时钟周期为 8.49<br />

纳秒,与 FPGA 的 118MHz 时钟频率对应。由于生成输出需<br />

要 49 个时钟周期的时延,有效数据速率为 2.4Msps。布局布<br />

线前估计 FPGA 占用面积为 7 个 DsP48E slice,1,105 个触<br />

发器和 1,790 个查找表。<br />

通过分析 Vivado HLs 生成的报告文件,发现工具生成了<br />

两个浮点加法减法器内核。因此采用下列指令:<br />

set_directive_interface -mode ap_fifo<br />

"PID_Controller" coeff<br />

set_directive_interface -mode ap_fifo<br />

"PID_Controller" din<br />

38 赛灵思中国通讯 46 期 2012 年冬季刊