下载 - Xilinx

下载 - Xilinx

下载 - Xilinx

Create successful ePaper yourself

Turn your PDF publications into a flip-book with our unique Google optimized e-Paper software.

A s k F A E - x<br />

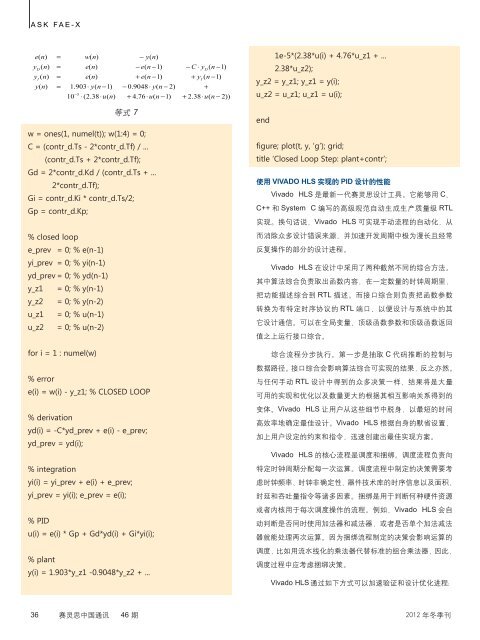

等式 7<br />

w = ones(1, numel(t)); w(1:4) = 0;<br />

C = (contr_d.Ts - 2*contr_d.Tf) / ...<br />

(contr_d.Ts + 2*contr_d.Tf);<br />

Gd = 2*contr_d.Kd / (contr_d.Ts + ...<br />

2*contr_d.Tf);<br />

Gi = contr_d.Ki * contr_d.Ts/2;<br />

Gp = contr_d.Kp;<br />

% closed loop<br />

e_prev = 0; % e(n-1)<br />

yi_prev = 0; % yi(n-1)<br />

yd_prev = 0; % yd(n-1)<br />

y_z1 = 0; % y(n-1)<br />

y_z2 = 0; % y(n-2)<br />

u_z1 = 0; % u(n-1)<br />

u_z2 = 0; % u(n-2)<br />

for i = 1 : numel(w)<br />

% error<br />

e(i) = w(i) - y_z1; % CLOSED LOOP<br />

% derivation<br />

yd(i) = -C*yd_prev + e(i) - e_prev;<br />

yd_prev = yd(i);<br />

% integration<br />

yi(i) = yi_prev + e(i) + e_prev;<br />

yi_prev = yi(i); e_prev = e(i);<br />

% PID<br />

u(i) = e(i) * Gp + Gd*yd(i) + Gi*yi(i);<br />

% plant<br />

y(i) = 1.903*y_z1 -0.9048*y_z2 + ...<br />

1e-5*(2.38*u(i) + 4.76*u_z1 + ...<br />

2.38*u_z2);<br />

y_z2 = y_z1; y_z1 = y(i);<br />

u_z2 = u_z1; u_z1 = u(i);<br />

36 赛灵思中国通讯 46 期 2012 年冬季刊<br />

end<br />

figure; plot(t, y, ‘g’); grid;<br />

title ‘Closed Loop Step: plant+contr’;<br />

使用 VIVADO HLS 实现的 PID 设计的性能<br />

Vivado HLs 是最新一代赛灵思设计工具。它能够用 C、<br />

C++ 和 system C 编写的高级规范自动生成生产质量级 RTL<br />

实现。换句话说,Vivado HLs 可实现手动流程的自动化,从<br />

而消除众多设计错误来源,并加速开发周期中极为漫长且经常<br />

反复操作的部分的设计进程。<br />

Vivado HLs 在设计中采用了两种截然不同的综合方法。<br />

其中算法综合负责取出函数内容,在一定数量的时钟周期里,<br />

把功能描述综合到 RTL 描述。而接口综合则负责把函数参数<br />

转换为有特定时序协议的 RTL 端口,以便设计与系统中的其<br />

它设计通信。可以在全局变量、顶级函数参数和顶级函数返回<br />

值之上运行接口综合。<br />

综合流程分步执行。第一步是抽取 C 代码推断的控制与<br />

数据路径。接口综合会影响算法综合可实现的结果,反之亦然。<br />

与任何手动 RTL 设计中得到的众多决策一样,结果将是大量<br />

可用的实现和优化以及数量更大的根据其相互影响关系得到的<br />

变体。Vivado HLs 让用户从这些细节中脱身,以最短的时间<br />

高效率地确定最佳设计。Vivado HLs 根据自身的默省设置,<br />

加上用户设定的约束和指令,迅速创建出最佳实现方案。<br />

Vivado HLs 的核心流程是调度和捆绑。调度流程负责向<br />

特定时钟周期分配每一次运算。调度流程中制定的决策需要考<br />

虑时钟频率、时钟非确定性、器件技术库的时序信息以及面积、<br />

时延和吞吐量指令等诸多因素。捆绑是用于判断何种硬件资源<br />

或者内核用于每次调度操作的流程。例如,Vivado HLs 会自<br />

动判断是否同时使用加法器和减法器,或者是否单个加法减法<br />

器就能处理两次运算。因为捆绑流程制定的决策会影响运算的<br />

调度,比如用流水线化的乘法器代替标准的组合乘法器,因此,<br />

调度过程中应考虑捆绑决策。<br />

Vivado HLs 通过如下方式可以加速验证和设计优化进程: