Zoznam použitých symbolov a skratiek - Žilinská univerzita

Zoznam použitých symbolov a skratiek - Žilinská univerzita

Zoznam použitých symbolov a skratiek - Žilinská univerzita

You also want an ePaper? Increase the reach of your titles

YUMPU automatically turns print PDFs into web optimized ePapers that Google loves.

DIPLOMOVÁ PRÁCA List č. 1<br />

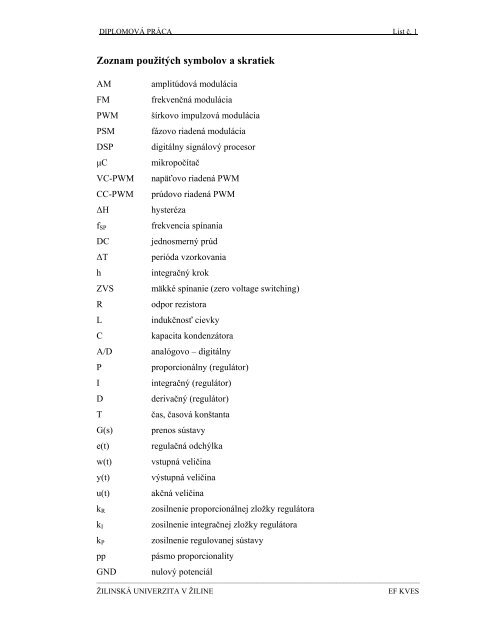

<strong>Zoznam</strong> použitých <strong>symbolov</strong> a <strong>skratiek</strong><br />

AM<br />

FM<br />

PWM<br />

PSM<br />

DSP<br />

μC<br />

VC-PWM<br />

CC-PWM<br />

ΔH<br />

f SP<br />

DC<br />

ΔT<br />

h<br />

ZVS<br />

R<br />

L<br />

C<br />

A/D<br />

P<br />

I<br />

D<br />

T<br />

G(s)<br />

e(t)<br />

w(t)<br />

y(t)<br />

u(t)<br />

k R<br />

k I<br />

k P<br />

pp<br />

amplitúdová modulácia<br />

frekvenčná modulácia<br />

šírkovo impulzová modulácia<br />

fázovo riadená modulácia<br />

digitálny signálový procesor<br />

mikropočítač<br />

napäťovo riadená PWM<br />

prúdovo riadená PWM<br />

hysteréza<br />

frekvencia spínania<br />

jednosmerný prúd<br />

perióda vzorkovania<br />

integračný krok<br />

mäkké spínanie (zero voltage switching)<br />

odpor rezistora<br />

indukčnosť cievky<br />

kapacita kondenzátora<br />

analógovo – digitálny<br />

proporcionálny (regulátor)<br />

integračný (regulátor)<br />

derivačný (regulátor)<br />

čas, časová konštanta<br />

prenos sústavy<br />

regulačná odchýlka<br />

vstupná veličina<br />

výstupná veličina<br />

akčná veličina<br />

zosilnenie proporcionálnej zložky regulátora<br />

zosilnenie integračnej zložky regulátora<br />

zosilnenie regulovanej sústavy<br />

pásmo proporcionality<br />

GND nulový potenciál<br />

–––––––––––––––––––––––––––––––––––––––––––––––––––––––––––––––––––––––––––––––––––––<br />

ŽILINSKÁ UNIVERZITA V ŽILINE<br />

EF KVES

DIPLOMOVÁ PRÁCA List č. 2<br />

V CC<br />

U DC<br />

I/O<br />

LSB<br />

MSB<br />

napájacie napätie<br />

jednosmerné napätie<br />

vstupno – výstupný<br />

najmenej významný bit (Less Significant Bit)<br />

najviac významný bit (Most Significant Bit)<br />

H vysoká úroveň (logická 1)<br />

L nízka úroveň (logická 0)<br />

–––––––––––––––––––––––––––––––––––––––––––––––––––––––––––––––––––––––––––––––––––––<br />

ŽILINSKÁ UNIVERZITA V ŽILINE<br />

EF KVES

DIPLOMOVÁ PRÁCA List č. 3<br />

ÚVOD<br />

Témou mojej diplomovej práce je návrh riadenia pre zvárací invertor s použitím<br />

mikropočítača Atmel AVR. Mikropočítače AVR sú veľmi rozšírené, majú jednoduché<br />

ovládanie a sú nasadzované na jednoduchšie aplikácie.<br />

V súčasnej dobe sa v oblasti zváracích zdrojov dostali do popredia zdroje<br />

s DC/DC meničmi a vysokofrekvenčnými transformátormi. Pri použití rezonančných<br />

meničov sa kladie veľký dôraz na riadenie meniča a to najmä pri chode naprázdno<br />

a dynamických zmenách parametrov záťaže, pretože pri rezonančnom meniči je dôležité<br />

nielen presné navrhnutie silových prvkov, ale aj veľmi presné a dynamické riadenie.<br />

Preto je veľmi dôležité navrhnúť správny spôsob riadenia ktoré bude vyhovovať danej<br />

topológií a zároveň bude realizovateľné pomocou softwarových prostriedkov<br />

a prídavných obvodov ktoré nám ponúka mikropočítač AVR. Cieľom mojej diplomovej<br />

práce je navrhnúť takéto riadenie a vytvoriť funkčnú vzorku, ktorú bude možné<br />

otestovať v reálnej aplikácii.<br />

Vo svojej diplomovej práci sa zameriam na 3 oblasti návrhu – výber vhodného<br />

typu PWM pre riadenie a spôsoby výpočtu regulátorov, výpočet stavového modelu a<br />

nakoniec samotné naprogramovanie a spôsob pripojenia mikropočítača k meniču.<br />

V 1. časti opíšem typy PWM používané pre riadenie výkonových<br />

polovodičových systémov a vyberiem vhodný typ pre riadenie meniča pre oblúkové<br />

zváranie. V 2. časti sa zameriam na opis systému (meniča) v stavovom priestore<br />

pomocou diferenciálnych rovníc. V ďalšej časti ukážem jeden zo spôsobov návrhu<br />

regulátorov, ak poznáme prechodovú charakteristiku systému, zároveň vypočítam<br />

konštanty regulátorov, ktoré použijem v riadiacom programe. Pripojenie mikropočítača<br />

k meniču a ostatných prvkov ktoré sú potrebné pre riadenie je riešené v časti 4.<br />

V poslednej časti sa zameriam na opis samotného programu a spôsob jeho realizácie pre<br />

mikropočítač ATmega 16.<br />

–––––––––––––––––––––––––––––––––––––––––––––––––––––––––––––––––––––––––––––––––––––<br />

ŽILINSKÁ UNIVERZITA V ŽILINE<br />

EF KVES

DIPLOMOVÁ PRÁCA List č. 4<br />

1.POUŽÍVANÉ TYPY PWM PRE RIADENIE VPS<br />

1.1 Princíp PWM<br />

V elektrotechnickej praxi sa používajú rôzne druhy modulácií.<br />

V telekomunikačnej technike je to najmä amplitúdová AM a frekvenčná FM modulácia.<br />

Vo výkonovej elektronike je základným druhom šírkovo impulzná modulácia<br />

ŠIM, alebo PWM (Pulse Width Modulation). PWM modulácia má viac druhov, podľa<br />

toho ktorú veličinu riadime a akým spôsobom je PWM generovaná.<br />

Obr.1.1: Princíp PWM a priebehy, normálny obdĺžnikový priebeh<br />

Pretože tento systém sa používa aj pri riadení meničov pre oblúkové zváranie,<br />

priblížime si niektoré druhy PWM modulácie a pozrieme sa na spôsob akým sa<br />

jednotlivé druhy PWM modulácie vytvárajú. Povedané v skratke, PWM je cesta ako<br />

digitálne modulovať analógový signál..<br />

Signál PWM je stále digitálny, pretože v každom časovom okamihu je na<br />

výstupe buď nulové alebo plné jednosmerné napätie. Napäťový analógový signál je<br />

tvorený opakovanou sériou obdĺžnikových impulzov.<br />

–––––––––––––––––––––––––––––––––––––––––––––––––––––––––––––––––––––––––––––––––––––<br />

ŽILINSKÁ UNIVERZITA V ŽILINE<br />

EF KVES

DIPLOMOVÁ PRÁCA List č. 5<br />

10%<br />

U<br />

50%<br />

t<br />

90%<br />

t<br />

t<br />

Obr.1.2: Signály PWM pre rôzne pracovné cykly<br />

Obrázok 1.2 znázorňuje tri rôzne PWM signály. Prvý je pre 10% striedy, čo<br />

znamená, že signál je na výstupe počas 10% periódy a počas 90% periódy je signál<br />

vypnutý. Ďalšie dva priebehy ukazujú 50% a 90% striedy. Tieto tri výstupy PWM<br />

modulujú 3 rôzne hodnoty ľubovoľného analógového signálu. Ak napríklad je<br />

analógový vstup 9V a strieda je 10%, výsledok je ten istý ako by sme mali analógový<br />

signál hodnoty 0,9V.<br />

Jedna z výhod PWM je to, že signál zostáva digitálny počas celej trasy z DSP<br />

alebo μC až do riadeného systému. Nie je potrebná žiadna konverzia z digitálnej do<br />

analógovej formy.<br />

Poruchový signál môže ovplyvniť výstupný digitálny signál PWM len vtedy ak<br />

je dostatočne silný na zmenu log. 1 na log. 0 alebo naopak. Pri použití PWM vo<br />

výkonovej el. takýto stav nastane len veľmi zriedkavo, preto sa PWM s výhodou<br />

používa na riadenie statických výkonových meničov.<br />

–––––––––––––––––––––––––––––––––––––––––––––––––––––––––––––––––––––––––––––––––––––<br />

ŽILINSKÁ UNIVERZITA V ŽILINE<br />

EF KVES

DIPLOMOVÁ PRÁCA List č. 6<br />

1.2 Druhy PWM modulácie<br />

1. napäťová VC-PWM (Voltage Controlled PWM)<br />

2. prúdová CC-PWM (Current Controlled PWM)<br />

3. kombinovaná VC+CC PWM<br />

4. fázovo riadená PWM - PSM (Phase Shift Modulation)<br />

1. Napäťová PWM (VC-PWM) sa podľa spôsobu vytvárania impulzov delí na:<br />

a) Softwarovú<br />

b) Hardwarovú<br />

Softwarová napäťová PWM – ako sám názov hovorí je vytváraná programovými<br />

prostriedkami a to buď pomocou DSP, alebo mikropočítačmi (μC).<br />

Hardwarová napäťová PWM – je vytváraná pomocou komparátorov<br />

a generátora pílového priebehu, teda hardwarovými prostriedkami.<br />

V oboch uvedených prípadoch sa jedná o tzv. komparačnú metódu, čo znamená,<br />

že modulovaný analógový signál je porovnávaný s referenčným signálom, najčastejšie<br />

pílového priebehu.<br />

2. Prúdová PWM (CC-PWM) – základom je regulačná slučka prúdu - môže byť:<br />

a) S konštantnou hysterézou<br />

b) S konštantnou frekvenciou spínania – tzv. delta modulácia<br />

c) S dvoma hysteréznymi pásmami<br />

Prúdová PWM s konštantnou hysterézou (ΔH% = konšt. f sp ≠konšt.) –<br />

regulovaná veličina sa pohybuje v určitom hysteréznom pásme okolo žiadanej hodnoty.<br />

Percentuálna hodnota hysterézy je stále rovnaká, z čoho vyplýva, že pri menších<br />

zaťaženiach musíme mať frekvenciu spínania, vyššiu aby sme dodržali percentuálnu<br />

hodnotu hysterézy.<br />

Prúdová PWM s konštantnou frekvenciou spínania (ΔH% ≠ konšt. f sp = konšt.) -<br />

je to komparačná metóda, je vhodná pre μC. Frekvencia vzorkovania je v každom<br />

okamihu rovnaká.<br />

–––––––––––––––––––––––––––––––––––––––––––––––––––––––––––––––––––––––––––––––––––––<br />

ŽILINSKÁ UNIVERZITA V ŽILINE<br />

EF KVES

DIPLOMOVÁ PRÁCA List č. 7<br />

Prúdová PWM s dvoma hyst. pásmami – využíva sa v el. pohonoch pri riadení<br />

4Q meniča.<br />

3. Kombinovaná PWM – použitie v el. pohonoch, regulácia je robená cez prúdovú<br />

slučku, pretože napätie nie je spojité a teda sa nedá komparovať.<br />

4. Fázovo riadená PWM – je to osobitný druh, používaný najmä vo výkonovej<br />

elektronike. Rozdiel oproti ostatným spôsobom je ten, že sa nemení šírka<br />

impulzu, ale vzájomné posunutie dvoch kanálov PWM.<br />

1.3 Spôsoby generovania PWM<br />

V tejto časti opíšem druhy PWM, ktoré sa používajú vo výkonovej elektronike<br />

najmä na riadenie DC/DC meničov a vysvetlím ich princíp. Vo všetkých prípadoch sa<br />

jedná o komparačnú metódu PWM.<br />

1.3.1 Hardwarová PWM<br />

Povedzme si teraz trochu bližšie o tom ako sa PWM generuje. Najjednoduchšia<br />

forma generovania PWM s pevnou frekvenciou spínania f sp , je porovnávanie signálu<br />

ktorý chceme previesť na postupnosť impulzov so signálom ktorý má ostré hrany,<br />

napríklad pílový alebo trojuholníkový priebeh. Tento princíp sa dá aplikovať použitím<br />

komparátora na generovanie PWM, kde výstupné napätie komparátora je log. 1 vtedy,<br />

keď na negatívnom vstupe (-) je hodnota napätia nižšia ako na vstupe označenom<br />

znamienkom +.<br />

Modulovaný<br />

signál<br />

Nosný<br />

signál<br />

Komparátor<br />

Šírkovo impulzová<br />

modulácia<br />

Obr.1.3: Princíp generovania PWM pomocou komparátora<br />

–––––––––––––––––––––––––––––––––––––––––––––––––––––––––––––––––––––––––––––––––––––<br />

ŽILINSKÁ UNIVERZITA V ŽILINE<br />

EF KVES

DIPLOMOVÁ PRÁCA List č. 8<br />

Ako už bolo uvedené, na generovanie PWM sa nemusí používať len<br />

trojuholníkový priebeh (obr.1.3.). Použitie pílového priebehu je znázornené na obrázku<br />

1.4:<br />

Nábežná<br />

hrana<br />

Dobežná<br />

hrana<br />

Obr.1.4: Generovanie PWM pomocou pílového priebehu<br />

Schéma znázornená na obr.1.4 ukazuje generovanie hrany (nábežnej aj<br />

dobežnej) v okamihu rovnakej okamžitej hodnoty sínusového priebehu a pílového<br />

priebehu. Tento spôsob sa ľahko vytvorí pomocou analógových súčiastok, ale spôsobuje<br />

nepresnosti a posunutie okamihu generovania hrán ak je v sínusovom signále čo i len<br />

malý šum. Väčšina modulátorov je dnes tvorená digitálne, avšak tam môže nastať<br />

problém s výpočtom a presným prevedením modulačného a nosného signálu.<br />

1.3.2 Digitálne riadenie – Softwarová PWM<br />

Veľké množstvo mikropočítačov a DSP procesorov obsahuje jednotky pre<br />

generovanie PWM priamo na čipe. Napríklad mikropočítač firmy Atmel AVR ATmega<br />

16 obsahuje na čipe 3 čítače/časovače, ktoré môžu slúžiť ako PWM modulátory. Tieto<br />

čítače/časovače vytvárajú postupnosť impulzov PWM modulácie komparačnou<br />

metódou. Pre spustenie PWM je potrebné :<br />

• Nastaviť periódu v čítači/časovači<br />

• Spustiť časovač<br />

• Zadať hodnotu do porovnávacieho registra<br />

Aj keď rôzne čipy s PWM modulátormi sa programujú rozdielne, základný postup je<br />

u všetkých rovnaký.<br />

–––––––––––––––––––––––––––––––––––––––––––––––––––––––––––––––––––––––––––––––––––––<br />

ŽILINSKÁ UNIVERZITA V ŽILINE<br />

EF KVES

DIPLOMOVÁ PRÁCA List č. 9<br />

1.3.3 Princíp softwarovej PWM – komparačná metóda<br />

Princíp softwarovej PWM je znázornený na obrázku 1.6. V čase t 1 sa zosníma<br />

hodnota analógového signálu, podobne aj v čase t 2 . Z týchto dvoch hodnôt sa urobí<br />

stredná hodnota, ktorá sa vynásobí intervalom vzorkovania, teda hodnotou ΔT. Tým<br />

dostaneme plochu, ktorú daný analógový signál zaberal od času t 1 po čas t 2 . Presnosť<br />

týchto dvoch hodnôt je závislá na počte bitov s ktorými je prevodník schopný pracovať<br />

– čím viac bitov, tým presnejšia hodnota. Ďalej je presnosť výpočtu plochy závislá aj na<br />

druhu použitej metódy výpočtu, pretože sa jedná o výpočet integrálu (integrál = plocha).<br />

Mnou popísaná metóda sa nazýva obdĺžniková, ale použiť sa môže aj lichobežníková<br />

metóda, ktorá je presnejšia. Ja som zvolil obdĺžnikovú metódu kvôli jednoduchosti<br />

výpočtu, pričom presnosť je pre našu aplikáciu dostatočná. Pri veľmi vysokom počte<br />

bitov, však stúpa doba prevodu, preto je potrebné voliť prevodník s parametrami, ktoré<br />

najlepšie vyhovujú danej aplikácii. Od hodnoty ΔT nám závisí dynamika celého<br />

systému. Pri veľmi nízkej hodnote ΔT stúpa skreslenie kvôli šumu, avšak toto je možné<br />

eliminovať použitím filtra. Základom tohto druhu modulácie je rovnosť plôch ktoré<br />

zaberá analógový signál a signál PWM generovaný mikropočítačom, tak ako je to vidno<br />

na obrázku. Pretože hodnota výstupného napätia môže byť len 0 alebo U DC , je zmena<br />

strednej hodnoty výstupného signálu dosiahnutá zmenou doby zopnutia t sp .<br />

U DC<br />

t sp<br />

s 1<br />

s 2<br />

Analógový signál<br />

t 1 t 2<br />

ΔT<br />

t<br />

Obr.1.6: Princíp softwarovej PWM, obdĺžniková metóda<br />

Vyššie opísané spôsoby predstavujú tzv. jednoduchú PWM, kde sa na základe<br />

požiadavky mení šírka generovaného impulzu . Takáto PWM sa používa na riadenie<br />

„klasických“ konštrukcíí meničov ako sú napríklad znižovací alebo zvyšovací menič.<br />

Pre riadenie mostových mäkko spínaných rezonančných meničov nie je možné<br />

použitie jednoduchej PWM a preto sa používa iný spôsob širkovo-impulzovej<br />

–––––––––––––––––––––––––––––––––––––––––––––––––––––––––––––––––––––––––––––––––––––<br />

ŽILINSKÁ UNIVERZITA V ŽILINE<br />

EF KVES

DIPLOMOVÁ PRÁCA List č. 10<br />

modulácie, ktorý sa nazýva PHASE SHIFT MODULATION (PSM) čo znamená fázovo<br />

riadenú šírkovo impulzovú moduláciu. Princíp PSM si vysvetlíme na príklade meniča<br />

ktorý je použitý v zváracom invertore a jedná sa o plnomostový mäkko spínaný<br />

rezonančný menič.<br />

1.4 Fázovo riadená – PWM (Phase Shift Modulation - PSM)<br />

Tento druh PWM sa používa na riadenie rezonančných DC/DC meničov – je to<br />

jediný spôsob akým sa dá rezonančný DC/DC menič riadiť. Keďže v zváracom<br />

invertore, pre ktorý bude toto riadenie slúžiť bude použitý práve rezonančný DC/DC<br />

menič priblížime si tento spôsob PWM trochu bližšie. Základnou črtou tohoto typu<br />

modulácie je to, že sa nemení šírka impulzu, ani perióda signálu, ale sa mení doba počas<br />

ktorej sú dva signály PSM v rovnakom stave (log.1 alebo log.0). Z uvedeného vyplýva,<br />

že pre riadenie pomocou PSM potrebujeme minimálne dva kanály riadiacich impulzov,<br />

pretože sa mení posuv signálu jedného kanála vzhľadom na druhý. Inak povedané podľa<br />

úrovne záťaže sa mení doba zopnutia jednotlivých dvojíc tranzistorov.<br />

Rovnako ako jednoduchú PWM aj PSM môžeme generovať dvomi spôsobmi<br />

hardwarovo, alebo softwarovo pomocou DSP alebo μC. Hardwarovo sa PSM modulácia<br />

vytvára podobne ako klasická PWM, pričom na vytvorenie fázovo posunutej PWM<br />

modulácie sa pridajú niektoré pomocné klopné obvody. Jedná sa o klopné obvody, ktoré<br />

sú schopné reagovať na dobežnú hranu signálu a tým vytvoriť z klasickej PWM<br />

moduláciu typu PSM.<br />

Spôsob vytvorenia PSM pomocou softwarových prostriedkov má rovnaký<br />

princíp, ale nie sú použité klopné obvody, celý proces sa odohráva v pamäti μC. Do μC<br />

vstupuje len nameraná hodnota výstupného prúdu alebo napätia.<br />

V mojej práci použijem spôsob ktorý obsahuje oba spôsoby, keď regulátory<br />

a PWM modulácia budú realizované v mikropočítači ATmega16 a PSM modulácia<br />

bude vytvorená pomocou vonkajších klopných obvodov. Takýto spôsob som zvolil<br />

preto, aby som ušetril výpočtový čas mikropočítača.<br />

Na obrázku 1.7 je znázornená topológia mäkko spínaného DC/DC meniča, pre<br />

ktorý urobím návrh riadiaceho obvodu:<br />

–––––––––––––––––––––––––––––––––––––––––––––––––––––––––––––––––––––––––––––––––––––<br />

ŽILINSKÁ UNIVERZITA V ŽILINE<br />

EF KVES

DIPLOMOVÁ PRÁCA List č. 11<br />

T A<br />

D A<br />

C A<br />

T C<br />

D C<br />

C C<br />

U 1<br />

Tr<br />

D2<br />

L R<br />

D 1<br />

L o<br />

C o<br />

U o<br />

T B<br />

D B<br />

C B<br />

T D<br />

D D<br />

C D<br />

Obr.1.7:Topológia mäkko spínaného DC/DC meniča<br />

ZVS rezonančný menič má dva pracovné intervaly pri ktorých sa prenáša výkon<br />

z primárnej časti na sekundárnu časť.[2] Je to vtedy, keď sú zopnuté dva tranzistory<br />

ktoré sú v schéme umiestnené diagonálne – buď ľavý horný s pravým spodným, alebo<br />

pravý horný s ľavým spodným a tieto dvojice spínajú v protifáze tzn., raz je zopnutá<br />

jedna dvojica a raz druhá.<br />

T A<br />

D A<br />

C A<br />

T C<br />

D C<br />

C C<br />

U 1<br />

Tr<br />

D2<br />

L R<br />

D 1<br />

L o<br />

C o<br />

U o<br />

T B<br />

D B<br />

C B<br />

T D<br />

D D<br />

C D<br />

Obr.1.8: Prenos energie na výstup<br />

Na obrázku 1.8 sú to dvojice T A - T D a T B - T C . ZVS rezonančný menič má ešte<br />

ďalšie intervaly pomocou ktorých sa dosahuje mäkké spínanie. Jeden z týchto<br />

intervalov sa nazýva clamped freewheeling interval [2] – nulový interval, pri tomto<br />

intervale spína dvojica tranzistorov ktorá je vedľa seba, teda horné dva, alebo spodné<br />

–––––––––––––––––––––––––––––––––––––––––––––––––––––––––––––––––––––––––––––––––––––<br />

ŽILINSKÁ UNIVERZITA V ŽILINE<br />

EF KVES

DIPLOMOVÁ PRÁCA List č. 12<br />

dva, pričom sa neprenáša energia z primárnej časti na sekundárnu. Pomocou PSM<br />

modulácie môžeme meniť dobu trvania jednotlivých intervalov a tým riadiť tok energie<br />

meniča. Ak je na výstupe plná záťaž uplatňuje sa len prvý interval. Čím sa záťaž<br />

zmenšuje tým viac sa uplatňuje nulový (freewheeling) interval.<br />

T A<br />

D A<br />

C A<br />

T C<br />

D C<br />

C C<br />

U 1<br />

Tr<br />

D2<br />

L R<br />

D 1<br />

L o<br />

C o<br />

U o<br />

T B<br />

D B<br />

C B<br />

T D<br />

D D<br />

C D<br />

Obr.1.8: Freewheeling interval<br />

Úlohou riadenia pomocou PSM v aplikácii pre tento menič je na základe<br />

fázového posuvu spínacích impulzov pre tranzistory meniť dobu trvania týchto dvoch<br />

vyššie popísaných intervalov.<br />

PSM A<br />

PSM B<br />

Preluka A-B<br />

PSM C<br />

PSM D<br />

Preluka C-D<br />

Obr.1.9: Riadiace impulzy a spôsob spínania tranzistorov pri normálnom zaťažení<br />

Ako vidno z obrázku , posunom fázy zopnutia dvoch tranzistorov , dosiahneme<br />

zmenu trvania daných dvoch intervalov. Teoreticky, ak by sme mali ideálny menič<br />

v stave naprázdno by spínali dvojice tranzistorov T A – T C (T B – T D ). V reálnej aplikácii<br />

aj pri minimálnej záťaži existuje interval prenosu energie, keď je energia rezonančnej<br />

indukčnosti využívaná na vybíjanie vnutorných kapacít tranzistorov.<br />

–––––––––––––––––––––––––––––––––––––––––––––––––––––––––––––––––––––––––––––––––––––<br />

ŽILINSKÁ UNIVERZITA V ŽILINE<br />

EF KVES

DIPLOMOVÁ PRÁCA List č. 13<br />

2. VYTVORENIE STAVOVÉHO MODELU PRE<br />

ZVOLENÚ TOPOLÓGIU MENIČA<br />

2.1 Stavový model systému<br />

Stavový model systému, môžeme chápať ako opis jeho vnútorného správania.<br />

Stav spojitého systému x (t)<br />

v ľubovoľnom časovom okamihu t je jednoznačne určený<br />

stavom systému v čase t = t(0)<br />

, a hodnotami vektora budiacich veličín u (t)<br />

medzi<br />

týmito dvoma časovými intervalmi [1]:<br />

[ ( t0),<br />

u(<br />

)]<br />

x ( t)<br />

= X x t<br />

(2.1)<br />

Tento opis môžeme vytvoriť pomocou sústavy n-diferenciálnych rovníc 1.rádu,<br />

alebo jednou diferenciálnou rovnicou n-tého rádu.[1] Sústavu n-diferenciálnych rovníc<br />

1.rádu môžeme zapísať v tvare:<br />

x′ t)<br />

f ( x , x ,..., x , u , u ,..., u , ) , (2.2)<br />

i<br />

( =<br />

i 1 2 r 1 2 s<br />

t<br />

kde uh<br />

- budiace veličiny (akčné), x<br />

i<br />

- stavové veličiny, i = 1,2,...,r; h = 1,2,...,s.<br />

Stavové veličiny nemusia byť nutne merateľné. Merateľné môžu byť vstupné<br />

a výstupné veličiny a tie umožňujú určenie stavových veličín.[1] Naopak, môže nastať<br />

aj taký prípad, kde výstupné veličiny sú kombináciou vektorov stavových veličín.<br />

Pre lineárny systém môžeme podľa [1] rovnice (2.2) a (2.3) napísať v tvare:<br />

x′ ( t)<br />

= A(<br />

t)<br />

⋅ x(<br />

t)<br />

+ B(<br />

t)<br />

⋅ u(<br />

t)<br />

x ( t 0<br />

) = x(0)<br />

(2.3)<br />

y( t)<br />

= C(<br />

t)<br />

⋅ x(<br />

t)<br />

+ D(<br />

t)<br />

⋅ u(<br />

t)<br />

(2.4)<br />

Význam jednotlivých vektorov a matíc je nasledovný:<br />

x(t)<br />

- vektor stavových premenných,<br />

u(t)<br />

- vektor budiacich(vstupných veličín,<br />

A - matica systému,<br />

B - budiaca matica,<br />

C –výstupná matica,<br />

D – matica prevodu.<br />

Tento tvar stavového modelu opisuje spojitý systém.<br />

Pre stacionárny systém, t.j. systém ktorého matice A,B,C,D sú v čase<br />

konštantné, platia rovnice:<br />

–––––––––––––––––––––––––––––––––––––––––––––––––––––––––––––––––––––––––––––––––––––<br />

ŽILINSKÁ UNIVERZITA V ŽILINE<br />

EF KVES

DIPLOMOVÁ PRÁCA List č. 14<br />

1. spojitý systém:<br />

x′ ( t)<br />

= A ⋅ x(<br />

t)<br />

+ B ⋅ u(<br />

t)<br />

- stavová rovnica (2.5)<br />

kde t – je spojitý čas t ∈ 0,∞)<br />

2. diskrétny systém:<br />

x [( k + 1) ΔT<br />

] = F ⋅ x(<br />

kΔT<br />

) + G ⋅u(<br />

kΔT<br />

) - stavová rovnica (2.6)<br />

kde kΔT – diskrétny čas, k ∈ 0,∞)<br />

ΔT – perióda vzorkovania<br />

Keďže výkonový polovodičový menič obsahuje polovodičové spínacie prvky,<br />

jedná sa o nelineárny systém.. Z tohoto dôvodu je potrebné urobiť linearizáciu systému.<br />

Linearizácia polovodičového systému sa robí počas jednotlivých pracovných<br />

intervalov a to tak, že celý pracovný cyklus systému (meniča), sa rozdelí na čiastočné,<br />

periodicky sa opakujúce intervaly a systém sa bude javiť ako elektrický obvod ktorý<br />

periodicky mení svoju štruktúru. Počas každého subintervalu sa štruktúra obvodu<br />

nemení, a teda je možné použiť rovnicu (2.5), ktorá opisuje lineárny stacionárny systém<br />

Pre zjednodušenie riešenia sa do úvahy môžu zobrať nasledujúce podmienky:<br />

• Polovodičové prvky s nulovým odporom v priepustnom smere<br />

a s nekonečným odporom v závernom smere<br />

• Konštantná budiaca funkcia na danom intervale<br />

• Okamžitá zmena vodivosti polovodičových súčiastok<br />

2.2 Rozdelenie pracovného cyklu meniča na intervaly<br />

Pri vytváraní modelu plnomostového mäkko spínaného rezonančného DC/DC<br />

meniča som bral do úvahy vyššie uvedené podmienky. Model som vytvoril<br />

v simulačnom programe MATLAB konkrétne pomocou príkazov v M-File. Spôsob<br />

vytvárania stavového modelu je nasledovný:<br />

Jeden pracovný cyklus meniča si rozdelíme na čiastkové intervaly počas ktorých<br />

sa topológia meniča nemení. Každý z týchto intervalov predstavuje jeden obvod, ktorý<br />

môžeme opísať pomocou diferenciálnych rovníc, z ktorých sa urobí model v stavovom<br />

priestore. Keďže každý čiastkový obvod je vlastne jednoduché zapojenie prvkov R-L-C<br />

výpočet sa značne zjednoduší.Postupnosťou týchto modelov v čase dostaneme stavový<br />

model meniča počas celého pracovného cyklu.<br />

–––––––––––––––––––––––––––––––––––––––––––––––––––––––––––––––––––––––––––––––––––––<br />

ŽILINSKÁ UNIVERZITA V ŽILINE<br />

EF KVES

DIPLOMOVÁ PRÁCA List č. 15<br />

Na nasledujúcich obrázkoch sú schémy zjednodušených obvodov počas<br />

jednotlivých pracovných intervalov meniča :<br />

T A<br />

T A<br />

CC<br />

U 1<br />

Tr<br />

D2<br />

L R<br />

D 1<br />

L o<br />

C o<br />

U o<br />

U 1<br />

Tr<br />

D 2<br />

L R<br />

D 1<br />

L o<br />

C o<br />

U<br />

T D<br />

T D<br />

Obr.2.1: Interval 1 – prenos energie<br />

Obr.2.2: Interval 2 - preluka<br />

T A<br />

T C<br />

D C<br />

C o<br />

L R<br />

D2<br />

D 1<br />

T B<br />

T D<br />

D D<br />

L o<br />

U o<br />

Obr.2.3: Interval 3 – nulový interval<br />

–––––––––––––––––––––––––––––––––––––––––––––––––––––––––––––––––––––––––––––––––––––<br />

ŽILINSKÁ UNIVERZITA V ŽILINE<br />

EF KVES

DIPLOMOVÁ PRÁCA List č. 16<br />

C A<br />

T C<br />

D C<br />

T C<br />

U 1<br />

Tr<br />

D2<br />

L R<br />

D 1<br />

L o<br />

C o<br />

U o<br />

U 1<br />

Tr<br />

D2<br />

L R<br />

D 1<br />

L o<br />

C o<br />

U o<br />

C D<br />

T B<br />

Obr.2.4: Interval 4 - preluka<br />

Obr.2.5: Interval 5 – prenos energie<br />

Pri vytváraní modelu som sa zameral len intervaly 1,3,5, pretože intervaly 2 až 4<br />

spotrebujú max. 10% z energie rezonančnej indukčnosti a teda ich môžeme<br />

z energetického hľadiska zanedbať. Intervaly 1 a 5 sú z topologického hľadiska jeden<br />

rovnaký obvod, ktorý striedavo pripájame na napätie rôznej polarity.<br />

Pre každý interval som zostrojil náhradný obvod, v ktorom vystupoval model<br />

transformátora. Všetky prvky na sekundárnej strane sú prepočítané na primárnu stranu<br />

pomocou prevodu. Pretože zdrojom energie v rezonančnom meniči je rezonančná<br />

(rozptylová) indukčnosť, namiesto magnetizačnej indukčnosti, som zvolil odpor, ktorý<br />

má takú veľkosť, aby ním pretekajúci prúd sa rovnal magnetizačnému prúdu. V ďalších<br />

kapitolách sú ukázané náhradné obvody a ich opis pomocou diferenciálnych rovníc.<br />

2.2.1 Interval 1 a 5 – prenos energie<br />

Topológia tohoto intervalu je zobrazená na obr.2.1 a 2.5. Ak urobíme náhradnú<br />

schému transformátora, pri akceptovaní zjednodušujúcich podmienok uvedených<br />

v predchádzajúcej kapitole a na jeho primárnu a sekundárnu stranu pripojíme prvky tak<br />

ako sú na obr.2.1 a 2.5, dostaneme náhradný obvod, ktorý je na obr.2.6.<br />

–––––––––––––––––––––––––––––––––––––––––––––––––––––––––––––––––––––––––––––––––––––<br />

ŽILINSKÁ UNIVERZITA V ŽILINE<br />

EF KVES

DIPLOMOVÁ PRÁCA List č. 17<br />

L R<br />

L´o<br />

R 1 R´2<br />

U 1<br />

i p<br />

i m<br />

i´Lo<br />

R m<br />

U´o<br />

C´o<br />

R´o<br />

Obr.2.6. Náhradný obvod pre intervaly 1 a 5<br />

Veličiny, ktoré sú prepočítané na primárnu stranu sú označené čiarkou.<br />

Z obrázku vidíme, že v náhradnom obvode máme tri stavové veličiny: prúdy<br />

i , i′<br />

p<br />

Lo<br />

a napätie<br />

u′<br />

Co<br />

. Ostatné prúdy alebo napätia v obvode sa dajú vypočítať kombináciou<br />

týchto troch stavových veličín. Odpory R , R ′<br />

1 2<br />

predstavujú parazitné odpory na<br />

primárnej a sekundárnej strane. Parazitný odpor kondenzátora<br />

v zaťažovacom odpore<br />

C′<br />

o<br />

je zahrnutý<br />

R′ o<br />

. Pri opise daného obvodu využijeme znalosť 1. a 2.<br />

Kirchhoffovho zákona a Ohmov zákon.<br />

Diferenciálne rovnice opisujúce náhradný obvod budú mať tvar diferenciálnych<br />

rovníc s konštantnými koeficientami. Ich počet sa rovná počtu stavových premenných,<br />

teda budeme mať celkovo tri diferenciálne rovnice. Hľadané rovnice sú:<br />

di<br />

dt<br />

p<br />

di′<br />

Lo<br />

dt<br />

du′<br />

dt<br />

1<br />

= ⋅<br />

L<br />

co<br />

r<br />

1<br />

= ⋅<br />

L′<br />

o<br />

1<br />

= ⋅ ( i′<br />

C′<br />

o<br />

[ − ( R + R ) ⋅ i + R ⋅i′<br />

+ U ]<br />

1<br />

[ R ⋅ i + ( −R<br />

− R′<br />

) ⋅i′<br />

− u′<br />

]<br />

m<br />

Lo<br />

p<br />

1<br />

− ⋅u′<br />

R′<br />

o<br />

m<br />

p<br />

m<br />

Co<br />

)<br />

m<br />

2<br />

Lo<br />

Lo<br />

1<br />

Co<br />

(2.7)<br />

Z diferenciálnych rovníc ktoré opisujú daný interval činnosti si podľa rovnice (2.5)<br />

vytvoríme matice, ktoré opisujú spojitý systém. Matice A a B sú v čase konštantné, čo<br />

vyplýva z toho, že počas daného intervalu sa topológia obvodu nemení. Maticový tvar:<br />

⎛ 1<br />

⎜−<br />

⎛ i ⎞ ⎜ Lr<br />

p<br />

⎜ ⎟ ⎜<br />

d⎜<br />

i′<br />

Lo ⎟ = ⎜<br />

⎜ ⎟ ⎜<br />

⎝u′<br />

Co ⎠ ⎜<br />

⎜<br />

⎝<br />

( R<br />

1<br />

Rm<br />

L′<br />

o<br />

0<br />

+ R<br />

m<br />

)<br />

R<br />

m<br />

Lr<br />

− R − ′<br />

m<br />

Ro<br />

L′<br />

o<br />

1<br />

C′<br />

o<br />

⎞<br />

0 ⎟<br />

⎟ ⎛ i<br />

p<br />

−1<br />

⎟ ⎜<br />

⎟ ⋅⎜<br />

i′<br />

Lo<br />

L′<br />

o ⎟ ⎜<br />

⎝ ′<br />

−1<br />

uCo<br />

⎟<br />

C′<br />

⋅ R′<br />

⎟<br />

o o ⎠<br />

⎛ 1<br />

⎞<br />

⎜<br />

⎟ ⎜ Lr<br />

⎟ + ⎜ 0<br />

⎟ ⎜<br />

⎠ ⎜<br />

0<br />

⎝<br />

⎞<br />

⎟<br />

⎛U<br />

⎟ ⎜<br />

⎟ ⋅ ⎜ 0<br />

⎟ ⎜<br />

⎟ ⎝ 0<br />

⎠<br />

⎞<br />

⎟<br />

⎟<br />

⎟<br />

⎠<br />

1<br />

(2.8)<br />

–––––––––––––––––––––––––––––––––––––––––––––––––––––––––––––––––––––––––––––––––––––<br />

ŽILINSKÁ UNIVERZITA V ŽILINE<br />

EF KVES

DIPLOMOVÁ PRÁCA List č. 18<br />

2.2.2 Interval 3 – nulový interval (freewheeling)<br />

Počas intervalu 3 sa energia z primárneho vinutia transformátora na sekundárne<br />

neprenáša, primárny prúd sa uzatvára cez rezonančnú cievku a zopnuté tranzistory T A a<br />

T C . Na sekundárnej strane sa prúd záťažou uzavrie cez vinutie transformátora a cez<br />

tlmivku. Výstupný prúd počas tohto intervalu klesá. Pretože primárne vinutie<br />

transformátora spolu s rezonančnou cievkou je vlastne vyskratované, počas tohto<br />

intervalu je menič odpojený zo siete. Náhradný obvod je na obr.2.7:<br />

R 1<br />

L R<br />

L´o<br />

i´o<br />

i´p<br />

i´Lo<br />

u´Co<br />

C´o<br />

R´o<br />

Obr.2.7: Náhradný obvod pre nulový interval<br />

Prvky v náhradnom obvode majú rovnaké označenie ako v predchádzajúcom prípade.<br />

V tomto intervale je do odporu<br />

ale aj tlmivky L′<br />

o<br />

.<br />

R′<br />

o<br />

zahrnutý nielen parazitný odpor kondenzátora C′<br />

o<br />

,<br />

Stavové veličiny sú aj v tomto prípade tri, teda počet diferenciálnych rovníc je<br />

rovnaký ako v prvom prípade. Ich tvar je:<br />

dip<br />

dt<br />

di′<br />

dt<br />

Lo<br />

du′<br />

dt<br />

co<br />

− R<br />

=<br />

L<br />

r<br />

1<br />

o<br />

1<br />

= ⋅(<br />

−i′<br />

C′<br />

o<br />

⋅i<br />

p<br />

− R′<br />

o<br />

= ⋅i′<br />

L′<br />

Lo<br />

Lo<br />

1<br />

+ ⋅u′<br />

R′<br />

o<br />

Co<br />

z nich vyplývajúci maticový tvar:<br />

)<br />

(2.9)<br />

⎛ − R1<br />

⎜<br />

⎛ i ⎞ ⎜ Lr<br />

p<br />

⎜ ⎟ ⎜<br />

d⎜<br />

i′<br />

Lo ⎟ = ⎜ 0<br />

⎜ ⎟ ⎜<br />

⎝u′<br />

Co ⎠ ⎜<br />

⎜<br />

0<br />

⎝<br />

0<br />

− R′<br />

o<br />

L′<br />

o<br />

−1<br />

C′<br />

0<br />

⎞<br />

0 ⎟<br />

⎟ ⎛ i<br />

p ⎞<br />

⎟ ⎜ ⎟<br />

0 ⎟ ⋅⎜<br />

i′<br />

Lo ⎟<br />

⎟ ⎜ ⎟<br />

⎝ ′<br />

1<br />

uCo<br />

⎟ ⎠<br />

( R′<br />

⋅ ′ ⎟<br />

o<br />

Co<br />

) ⎠<br />

(2.10)<br />

–––––––––––––––––––––––––––––––––––––––––––––––––––––––––––––––––––––––––––––––––––––<br />

ŽILINSKÁ UNIVERZITA V ŽILINE<br />

EF KVES

DIPLOMOVÁ PRÁCA List č. 19<br />

Maticové tvary pre oba intervaly činnosti opisujú správanie sa spojitého<br />

systému. Avšak v mojom prípade budú dané rovnice simulované na počítače a rovnako<br />

riadiaci obvod bude mať určitú dobu vzorkovania, potrebujeme matice ktoré budú mať<br />

diskrétny tvar podľa rovnice (2.6). Spôsobov vytvorenia matíc so spojitého pre<br />

diskrétny je viacero, ja som použil nepriamu Eulerovu transformáciu.<br />

2.3 Nepriama Eulerova transformácia<br />

Nepriama Eulerova transformácia je metóda pomocou ktorej transformujeme<br />

stavové matice pre spojitý systém, na matice pre diskrétny systém. Transformované<br />

matice systému sú použité pri modelovaní meniča v simulačnom programe Matlab. Táto<br />

metóda sa vyznačuje tým, že je absolútne stabilná. Výpočet vychádza z rovnice (2.5)<br />

a výsledkom je rovnica (2.6).Postup je nasledovný:<br />

x′ ( t)<br />

= A ⋅ x(<br />

t)<br />

+ B ⋅u(<br />

t)<br />

(2.5)<br />

x(<br />

h)<br />

− x(0)<br />

= A ⋅ x(<br />

h)<br />

+ B ⋅u(0)<br />

h<br />

(2.11)<br />

x( h ) − h ⋅ A ⋅ x(<br />

h)<br />

= x(0)<br />

+ h ⋅ B ⋅u(0)<br />

(2.12)<br />

[ 1 − ⋅ A] ⋅ x( h)<br />

= x(0)<br />

+ h ⋅ B ⋅u(0)<br />

h (2.13)<br />

−1<br />

−1<br />

[ 1 − h ⋅ A] ⋅ x(0)<br />

+ [ 1 − h ⋅ A] ⋅ h ⋅ B ⋅ u(0)<br />

x(<br />

h ) =<br />

(2.14)<br />

−1<br />

kde [ 1 − h ⋅ A] = F a [ 1 − h ⋅ A] ⋅ h ⋅ B = G<br />

−1<br />

(2.15)<br />

výsledná maticová rovnica bude mať tvar:<br />

x( h)<br />

= F ⋅ x(<br />

h −1)<br />

+ G ⋅u(<br />

h)<br />

(2.16)<br />

Rovnice (2.6) a (2.16) sú rovnaké, len v rovnici (2.16) je namiesto doby vzorkovania<br />

kΔ T použitý integračný krok h (krok výpočtu) s ktorým pracuje simulačný program.<br />

2.4 Simulácia stavového modelu v prostredí Matlab<br />

Pre simuláciu stavového modelu meniča som použil simulačný program<br />

MATLAB 6.5. V simulácii je zahrnutý nielen model meniča, ale aj model riadiaceho<br />

obvodu, rovnako aj doba vzorkovania. Výpočet diskrétnych matíc metódou nepriamej<br />

Eulerovej transformácie, je riešený odkazom na podprogram.<br />

–––––––––––––––––––––––––––––––––––––––––––––––––––––––––––––––––––––––––––––––––––––<br />

ŽILINSKÁ UNIVERZITA V ŽILINE<br />

EF KVES

DIPLOMOVÁ PRÁCA List č. 20<br />

Simulácia má dve časti:<br />

1. Nasimulovanie rozbehu meniča do zaťažovacieho odporu<br />

2. Pripojenie meniča naprázdno Jadro programu je pre obe časti rovnaké a skladá<br />

sa z viacero blokov. V nasledujúcej časti podrobnejšie opíšem funkiu<br />

jednotlivých častí:<br />

1. blokom programu je blok kde sa definujú počiatočné podmienky a parametre<br />

simulácie. Rovnako sa v tejto časti definujú aj premenné potrebné pre simuláciu.<br />

Ďalšou časťou programu je časť v ktorej sú zapísané stavové matice a spôsob<br />

výpočtu stavových premenných. Výpis z programu z časti pre výpočet priebehov<br />

stavových veličín:<br />

if (ip==0) & (im==0) & (iLop==0) & (uCop==0) - počiatočné podmienky<br />

X=[ip; iLop; uCop];<br />

- matica stavových premenných<br />

A=[-(R1+Rm)/Lr Rm/Lr 0; - matica systému<br />

Rm/Loutp (-Rm-R2p)/Loutp -1/Loutp;<br />

0 1/Cop -1/(Cop*Rop);];<br />

B=zeros(size(A));<br />

- budiaca matica<br />

B(1,1)=1/Lr;<br />

U=[Uv; 0; 0;];<br />

%vypocty<br />

[F1,G1]=INDIRECT_EULER(A,B,dT); - transformácia matíc<br />

i=i+1;<br />

X=F1*X + G1*U; - výpočet podľa rovnice (2.6)<br />

fprintf(fin,'%10.5g %8.3f %8.3f %8.3f\n',t,X(1),X(2),X(3)); - zápis výsledkov<br />

clear A,B;<br />

- zmazanie matíc<br />

end<br />

Riadok X=F1*X + G1*U; je prepísaná rovnica (2.12) pomocou ktorej<br />

dostaneme výsledné priebehy pre stavové veličiny. Pretože je v simulácii zahrnutý<br />

integračný krok h a zároveň aj vzorkovanie, nebudú výsledné priebehy veličín spojité,<br />

ale bude to postupnosť diskrétnych hodnôt s krokom h.<br />

Simulácia riadiaceho obvodu sa skladá z implementácie doby vzorkovania A/D<br />

prevodníka, zo simulácie regulačného obvodu, komparátora a zo simulácie obvodov<br />

slúžiacich na vytvorenie PSM - fázovo-posunutej PWM. Simulácia vzorkovania A/D<br />

prevodníka má nasledovný tvar:<br />

–––––––––––––––––––––––––––––––––––––––––––––––––––––––––––––––––––––––––––––––––––––<br />

ŽILINSKÁ UNIVERZITA V ŽILINE<br />

EF KVES

DIPLOMOVÁ PRÁCA List č. 21<br />

%vzorkovanie - simulacia A/D prevodnika<br />

tv=tv+1;<br />

- počítadlo<br />

if tv==(n*160) - ak čas výpočtu sa rovná n-násobku doby vzorkovania<br />

iLopm=iLop; - do premennej, ktorá predstavuje nameranú hodnotu,<br />

- sa vloží okamžitá hodnota stavovej premennej<br />

n=n+1; - a násobok sa zvýši o 1<br />

end<br />

Doba vzorkovania prevodníka je 62,5kHz = 16μs, keďže krok výpočtu simulácie je<br />

−5<br />

1,6.10<br />

0,1μs tak násobok ktorý zodpovedá vzorkovaniu frekvenciou 62,5Hz je: = 160<br />

−7<br />

1.10<br />

Regulátory sú nasimulované rovnakým spôsobom akým budú realizované<br />

v pamäti mikropočítača AVR v programovej slučke. V simulácii je použitý aj<br />

antiwindup. Výpis z programu:<br />

%regulatory<br />

Eu=(iLrefp-iLopm);<br />

- výpočet regulačnej odchýlky<br />

Int_C=Int_C0+dT*Eu; - výpočet integrálu v integračnej zložke<br />

w=Kp*Eu+(Ki-aw0)*Int_C; - výpočet akčnej veličiny<br />

aw1=w;<br />

- uloženie hodnoty akčnej veličiny pred obm.<br />

if (w

DIPLOMOVÁ PRÁCA List č. 22<br />

% fazovy shift obvod JK<br />

if k==0 & h==0 & c==0 d=0; end<br />

if k==5 & d==0 h=1; end<br />

if k==0 & h==1 d=1; end<br />

if k==5 & d==1 c=1; end<br />

if k==0 & c==1 d=0; end<br />

if k==5 & c==1 h=0; end<br />

if k==0 & h==0 & c==1 d=1;c=0; end<br />

% d-A q2-B q3-D q4-C spinaci cyklus (A-D)=pos (B-C)=neg<br />

Opis tohto bloku príkazov by bol pomerne zložitý, lepšie nám jeho funkciu priblíži<br />

obrázok 2.8:<br />

PWM<br />

40%<br />

PSM<br />

PWM<br />

80%<br />

PSM<br />

Obr.2.8: Reakcia simulovaného klopného obvodu na dobežnú hranu signálu PWM<br />

Pri simulovaní funkcie klopných obvodov JK, je treba mať na zreteli že pri<br />

uvedenom režime činnosti je frekvencia na výstupe obvodu polovičná oproti frekvencii<br />

PWM modulácie. Preto aj pri skutočnom riadiacom obvode platí že f PWM =2* f PSM .<br />

Výsledná simulácia sa skladá z nasimulovania rozbehu meniča naprázdno<br />

a následne jeho pripojenie na záťaž. Priebehy stavových veličín sú na obrázku 2.9.<br />

Detailné priebehy primárneho prúdu sú zobrazené na obr. 2.10. Charakteristiky<br />

potrebné pre identifikáciu prenosovej funkcie, použitej neskôr pre návrh regulátorov sú<br />

ukázané v nasledujúcej kapitole.<br />

–––––––––––––––––––––––––––––––––––––––––––––––––––––––––––––––––––––––––––––––––––––<br />

ŽILINSKÁ UNIVERZITA V ŽILINE<br />

EF KVES

DIPLOMOVÁ PRÁCA List č. 23<br />

i Lo (t)<br />

u Co (t)<br />

i p (t)<br />

u Co (t)<br />

Obr.2.9: Priebehy stavových veličín simulovaného modelu<br />

20<br />

15<br />

i P (t)<br />

10<br />

5<br />

U,I [V,A]<br />

0<br />

-5<br />

-10<br />

-15<br />

-20<br />

1.51 1.52 1.53 1.54 1.55 1.56 1.57 1.58 1.59 1.<br />

t [s]<br />

x 10 -3<br />

Obr.2.10: Detail primárneho prúdu<br />

–––––––––––––––––––––––––––––––––––––––––––––––––––––––––––––––––––––––––––––––––––––<br />

ŽILINSKÁ UNIVERZITA V ŽILINE<br />

EF KVES

DIPLOMOVÁ PRÁCA List č. 24<br />

3.SPÔSOBY NÁVRHU REGULÁTOROV<br />

Samotný menič bez riadiacich obvodov ktoré regulujú jeho tok energie, je pre<br />

praktické aplikácie nepoužiteľný. Preto je treba veľkú pozornosť venovať návrhu<br />

riadenia, ktoré je schopné reagovať na zmenu záťaže. Pri ručnom zváraní sa mení<br />

hlavne dĺžka oblúka, čo má za následok zmenu odporu oblúka a tým aj zmenu<br />

zváracieho prúdu. Preto je potrebné aby riadiaci obvod bol schopný udržať prúd na<br />

konštantnej hodnote a to aj pri zmene dĺžky oblúka. Ďalej je potrebné aby riadiaci<br />

obvod reguloval tok energie meniča aj pri skrate(zapaľovaní oblúka) a pri stave<br />

naprázdno.<br />

3.1 Regulátory<br />

Regulátorom sa nazýva zariadenie v regulačnom obvode, pomocou ktorého sa<br />

uskutočňuje proces automatickej regulácie. Do regulátora zahrňujeme všetky členy<br />

regulačného obvodu. Podstatou činnosti regulátorov je vyhodnotenie regulačnej<br />

odchýlky :<br />

e( t)<br />

= w(<br />

t)<br />

− y(<br />

t)<br />

(3.1)<br />

ako vstupného signálu a v spracovaní tejto odchýlky podľa zákona riadenia, ktorý je<br />

vlastný použitému regulátoru a vo vytvorení výstupného signálu – akčnej veličiny,<br />

s tým cieľom, aby odchýlka e (t)<br />

bola úplne eliminovaná, alebo bola čo najmenšia. [1]<br />

Podľa priebehu výstupnej veličiny môžeme regulátory rozdeliť na spojité<br />

a diskrétne. V spojitých regulátoroch sú všetky veličiny v čase spojité, v diskrétnych je<br />

jedna alebo viac veličín nespojitých.<br />

Obr.3.2: Zjednodušená bloková schéma regulátora<br />

3.1.1 Dynamické vlastnosti regulátorov<br />

Pri rozbore dynamických vlastností regulátorov podľa [1] sa obmedzíme na<br />

dynamické vlastnosti hlavného člena (obr.3.2), kde môžeme správanie sa<br />

kombinovaného regulátora popísať pomocou integro-diferenciálnej rovnice:<br />

–––––––––––––––––––––––––––––––––––––––––––––––––––––––––––––––––––––––––––––––––––––<br />

ŽILINSKÁ UNIVERZITA V ŽILINE<br />

EF KVES

DIPLOMOVÁ PRÁCA List č. 25<br />

T<br />

h<br />

h<br />

u<br />

t<br />

( h)<br />

(<br />

1<br />

0<br />

h−1<br />

( h−1)<br />

2<br />

de(<br />

t)<br />

t)<br />

+ Th<br />

u ( t)<br />

T u′′<br />

( t)<br />

T u′<br />

−1<br />

+<br />

2<br />

+<br />

1<br />

( t)<br />

+ u(<br />

t)<br />

= r0e(<br />

t)<br />

+ r−<br />

1∫<br />

e(<br />

τ ) dτ<br />

+ r (3.2)<br />

dt<br />

kde r e(<br />

) je proporcionálna zložka regulátora,<br />

0<br />

t<br />

t<br />

1∫<br />

r− e(<br />

τ ) dτ - integračná zložka regulátora,<br />

0<br />

de(<br />

t)<br />

r1 - derivačná zložka regulátora,<br />

dt<br />

h ( h)<br />

h−1<br />

h−1<br />

2<br />

Th u t)<br />

+ Th<br />

u ( t)<br />

+ T u′′<br />

( t)<br />

+ T u′<br />

−<br />

( t)<br />

- spomaľujúce členy regulátora.<br />

(<br />

1<br />

2<br />

1<br />

Rovnica (3.2) popisuje správanie proporcionálne – integračno – derivačného regulátora<br />

so spomaľujúcimi (zotrvačnými) členmi, alebo inak povedané skutočného PID<br />

regulátora. Ak časové konštanty zotrvačných členov v rovnici (3.2) položíme rovné nule<br />

( T = , T 0,...<br />

), dostaneme pohybovú rovnicu ideálneho PID regulátora:<br />

1<br />

0 2<br />

=<br />

t<br />

de(<br />

t)<br />

u( t)<br />

= r0 e(<br />

t)<br />

+ r−<br />

1∫<br />

e(<br />

τ ) dτ<br />

+ r1<br />

(3.3)<br />

dt<br />

0<br />

Ak urobíme Laplaceovu transformáciu rovnice (3.3), za predpokladu nulových<br />

počiatočných podmienok, môžeme ju upraviť na prenos ideálneho PID regulátora:<br />

U ( s)<br />

1<br />

GR ( s)<br />

= = r0 (1 + + TDs)<br />

(3.4)<br />

E(<br />

s)<br />

T s<br />

kde r<br />

0<br />

je proporcionálna konštanta regulátora,<br />

r<br />

−1<br />

- integračná konštanta regulátora,<br />

r<br />

1<br />

- derivaćná konštanta regulátora,<br />

r<br />

0<br />

= k R<br />

- zosilnenie analógového regulátora,<br />

I<br />

T I<br />

0<br />

- integračná časová konštanta regulátora,<br />

−1<br />

= r<br />

r<br />

r<br />

r<br />

1<br />

T D<br />

= - derivačná časová konštanta regulátora,<br />

0<br />

teraz podľa toho ktorú z konštánt r0 , r− 1,<br />

r1<br />

položíme rovné nule, dostaneme základné<br />

druhy regulátorov: P regulátor, I regulátor, derivačná zložka sa samostatne použiť nedá<br />

a kombinované druhy regulátorov PD regulátor, PI regulátor, PID regulátor.<br />

–––––––––––––––––––––––––––––––––––––––––––––––––––––––––––––––––––––––––––––––––––––<br />

ŽILINSKÁ UNIVERZITA V ŽILINE<br />

EF KVES

DIPLOMOVÁ PRÁCA List č. 26<br />

3.2 Nastavovateľné parametre regulátorov<br />

Vo vzťahoch (3.3 a 3.4) sme použili konštanty regulátorov r0 , r− 1,<br />

r1<br />

a časové<br />

konštanty regulátorov<br />

T , T<br />

I<br />

D<br />

. V skutočných regulátoroch sa stretávame s parametrami,<br />

pomocou ktorých môžeme určiť vplyv jednotlivých zložiek regulátora:<br />

pp [%] – pásmo proporcionality,<br />

T I<br />

0<br />

[s] – integračná časová konštanta,<br />

−1<br />

= r<br />

r<br />

r<br />

r<br />

1<br />

T D<br />

= [s] – derivačná časová konštanta.<br />

0<br />

Vysvetlíme si ich interpretáciu a praktický význam podľa [1]:<br />

Pásmo proporcionality – pp [%]<br />

kde<br />

1<br />

pp [%] = ⋅100, (3.5)<br />

r<br />

0<br />

r<br />

0<br />

= k<br />

R<br />

je zosilnenie regulátora (proporcionálna konštanta sa rovná zosilneniu<br />

regulátora). Pásmo proporcionality určuje o akú hodnotu, vyjadrenú v percentách, sa<br />

musí zmeniť vstupný signál regulátora, aby sa akčný člen prestavil z jednej okrajovej<br />

polohy do druhej (zmenil polohu z 0 na 100% alebo opačne).<br />

Ak pri riadení meniča požadujem zvlnenie výstupného prúdu napr. v rozmedzí<br />

+- 10% pri 100A, tak celková zmena bude 20A a teda 20% z čoho vyplýva, že pásmo<br />

proporcionality bude mať hodnotu pp = 20%. Zosilnenie P regulátora podľa rovnice<br />

(3.5) bude:<br />

1 100<br />

r<br />

0<br />

= ⋅100<br />

= = 5 ak požadujem zvlnenie iba +-5%, tak zosilnenie P<br />

pp 20<br />

regulátora bude 10 (tieto hodnoty sú len orientačné, nejedná sa o mnou použité<br />

parametre regulátora, skutočné parametre budú v rozmedzí týchto dvoch hodnôt).<br />

Z vyššie uvedeného vidíme, že pri zmenšujúcom sa pásme proporcionality sa<br />

zväčšuje zosilnenie.<br />

Integračná časová konštanta<br />

0<br />

T I<br />

[s] (3.6)<br />

= r<br />

r<br />

−1<br />

–––––––––––––––––––––––––––––––––––––––––––––––––––––––––––––––––––––––––––––––––––––<br />

ŽILINSKÁ UNIVERZITA V ŽILINE<br />

EF KVES

DIPLOMOVÁ PRÁCA List č. 27<br />

Túto konštantu môžeme určiť z prechodovej charakteristiky PI regulátora, tj pre<br />

vstupný signál rovný jednotkovému skoku. Integračná časová konštanta je čas, ktorý by<br />

potreboval čistý I regulátor, aby prestavil akčný člen (výstupný signál) do polohy, ktorú<br />

dosiahne PI regulátor v čase t = 0 vplyvom proporcionálnej zložky .<br />

Derivačná časová konštanta<br />

r<br />

r<br />

1<br />

T D<br />

= [s] (3.7)<br />

0<br />

Derivačná časová konštanta je čas, ktorý by potreboval čistý P regulátor, aby<br />

prestavil akčný člen do polohy ktorú dosiahne PD regulátor v čase t = 0 vplyvom svojej<br />

derivačnej zložky.<br />

3.3 Charakteristika činnosti spojitých regulátorov<br />

Vlastnosti a činnosti jednotlivých typov regulátorov sú podľa [1]<br />

charakterizované nasledovne:<br />

1. P regulátor – v uzatvorenom regulačnom obvode pracuje s trvalou regulačnou<br />

odchýlkou. Má dobré stabilizačné vlastnosti.<br />

2. I regulátor – v uzatvorenom regulačnom obvode pracuje len s prechodnou<br />

regulačnou odchýlkou. Regulačný pochod sa ustáli vtedy, ak sa regulačná<br />

odchýlka rovná nule.<br />

3. D člen – nie je schopný samostatne pracovať ako regulátor, pretože vstupným<br />

signálom je derivácia regulačnej odchýlky a nevie nič o veľkosti regulačnej<br />

odchýlky. Povoľuje akúkoľvek veľkosť ustálenej reg. odchýlky. Ako súčasť<br />

v kombinovanom regulátore zlepšuje stabilizačné vlastnosti regulačného<br />

obvodu.<br />

4. PI regulátor – odstraňuje trvalú regulačnú odchýlku, ktorú by sme mali pri<br />

použití P regulátora. Zlepšuje stabilizačné vlastnosti vzhľadom na použitie<br />

samostatného I regulátora. V počiatku regulačného pochodu prevláda<br />

proporcionálna zložka, s rastúcim časom prevláda vplyv integračnej zložky<br />

5. PD regulátor – zlepšuje stabilizačné vlastnosti vzhľadom na P regulátor. Je teda<br />

možné pracovať s vyšším zosilnením. V počiatkoch regulačného pochodu<br />

prevláda vplyv derivačnej zložky, s narastajúcim časom prevláda vplyv<br />

proporcionálnej zložky; regulátor pracuje s prechodným zvýšeným zosilnením.<br />

–––––––––––––––––––––––––––––––––––––––––––––––––––––––––––––––––––––––––––––––––––––<br />

ŽILINSKÁ UNIVERZITA V ŽILINE<br />

EF KVES

DIPLOMOVÁ PRÁCA List č. 28<br />

6. PID regulátor – v uzatvorenom regulačnom obvode odstraňuje vplyvom I zložky<br />

trvalú regulačnú odchýlku a vplyvom D zložky zlepšuje stabilizačné vlastnosti<br />

regulačného obvodu. V počiatku prechodového deja prevláda derivačná zložka,<br />

s narastajúcim časom prevláda integračná zložka regulátora.<br />

3.4 Voľba štruktúry regulátora k danej regulovanej sústave<br />

Dokonalý regulátor so širokými možnosťami nastavenia jednotlivých<br />

parametrov síce zaručí kvalitný regulaćný pochod, avšak je veľmi nákladný a vyžaduje<br />

zložité nastavovanie na to, aby bol plne využitý. Na druhej strane jednoduchý regulátor<br />

sa ľahko nastaví, ale nemusí splniť všetky požiadavky riadenia[1]. Z uvedeného<br />

vyplýva, že voľba typu regulátora je určená vlastnosťami regulovanej sústavy.<br />

V [1] je uvedený nasledovný prehľad pre voľbu štruktúry regulátora pre<br />

jednotlivé typy regulovaných sústav:<br />

I – regulátor je použiteľný pre reguláciu proporcionálnych sústav 1.rádu,<br />

s malou časovou konštantou, bez dopravného oneskorenia, pri pomalých a malých<br />

zmenách zaťaženia,<br />

P – regulátor, sa používa pre reguláciu proporcionálnych aj integračných sústav<br />

1. rádu, so strednou časovou konštantou, s menším dopravným oneskorením, pri malých<br />

zmenách zaťaženia, zanecháva trvalú regulačnú odchýlku pri regulácii<br />

proporcionálnych sústav,<br />

PI – regulátor, využíva sa na reguláciu proporcionálnych aj integračných sústav<br />

1. alebo vyšších rádov, s ľubovoľnými časovými konštantami, s ľubovoľným<br />

dopravným oneskorením, pri veľkých a pomalých zmenách záťaže,<br />

PD – regulátor, je vhodný na reguláciu proporcionálnych aj integračných sústav<br />

so zotrvačnosťou vyššieho rádu so strednými časovými konštantami, s veľkým<br />

dopravným oneskorením, pri malých zmenách záťaže, zanecháva trvalú regulačnú<br />

odchýlku,<br />

PID – regulátor, je určený na reguláciu proporcionálnych aj integračných sústav<br />

vyššieho rádu, s ľubovoľnými časovými konštantami a s dlhším dopravným<br />

oneskorením, pri veľkých a rýchlych zmenách záťaže.<br />

Všeobecne možno povedať, že pre väčšinu regulovaných sústav sa používajú P<br />

alebo PI regulátory a pre zložitejšie sústavy je vhodný PID regulátor. Čisto integračný<br />

–––––––––––––––––––––––––––––––––––––––––––––––––––––––––––––––––––––––––––––––––––––<br />

ŽILINSKÁ UNIVERZITA V ŽILINE<br />

EF KVES

DIPLOMOVÁ PRÁCA List č. 29<br />

regulátor sa využíva veľmi málo. Pri rozhodovaní o tom či použiť P alebo PI regulátor<br />

sa berie do úvahy to, či je prípustná trvalá regulačná odchýlka.<br />

0.4<br />

0.35<br />

0.3<br />

h S<br />

0.247<br />

Io [A]<br />

0.2<br />

K P<br />

t 0,33<br />

0.15<br />

0.105<br />

t 0,7<br />

0.05<br />

0<br />

0.0760.245 0.4 0.6 0.8 1 1.2 1.4 1.6 1.8 2<br />

t [s]<br />

x 10 -3<br />

Obr.3.6: Odozva meniča na jednotkový skok<br />

Pri riešení problému aký regulátor zvoliť pre menič pre zváranie elektrickým<br />

oblúkom, som vychádzal z prechodovej charakteristiky modelu meniča (obr. 3.6).<br />

Z obrázku vidíme, že ide o proporcionálnu sústavu 1. rádu, s takmer nulovým<br />

dopravným oneskorením. Ďalej som bral do úvahy typ záťaže, kde sa jedná o záťaž<br />

ktorá sa vzhľadom na časovú konštantu meniča mení pomaly, avšak jej zmena je veľká.<br />

Z uvedeného vyplýva, že najvhodnejším typom regulátora je typ PI. Typ P nie je<br />

možné použiť z toho dôvodu, že nie je prípustná trvalá regulačná odchýlka.<br />

3.5 Nastavenie regulátorov<br />

3.5.1 Identifikácia parametrov sústavy<br />

V tejto časti si ukážeme niektoré metódy identifikácie parametrov<br />

proporcionálnych sústav na základe ich prechodových charakteristík. Jedná sa<br />

o experimentálne metódy bez odvodenia rovníc a vzťahov.<br />

–––––––––––––––––––––––––––––––––––––––––––––––––––––––––––––––––––––––––––––––––––––<br />

ŽILINSKÁ UNIVERZITA V ŽILINE<br />

EF KVES

DIPLOMOVÁ PRÁCA List č. 30<br />

Obr.3.7: Prechodová charakteristika proporcionálnej sústavy<br />

Pretože prechodová charakteristika meniča, ktorý som modeloval, má tvar podľa<br />

obr.3.7, môžem použit identifikáciu parametrov systému pomocou doby nábehu a doby<br />

prieťahu. Tieto dve hodnoty nám vytýči dotyčnica ktorá vedie inflexným bodom na<br />

charakteristike. Potom možno pre prenos proporcionálnej sústavy 1.rádu napísať:<br />

G<br />

Kp<br />

−Tu<br />

s<br />

S<br />

( s)<br />

= e<br />

(3.8)<br />

Tns<br />

+ 1<br />

Koeficient prenosu (zosilnenie) K p pre proporcionálne sústavy pre jednotkovú skokovú<br />

zmenu akčnej veličiny, je daný ustáleným stavom na prechodovej charakteristike [1]<br />

Kp = h s<br />

(∞)<br />

(3.9)<br />

Aproximácia prechodovej charakteristiky pomocou doby T u a T n je veľmi<br />

nepresná. Oveľa presnejšia je aproximácia náhradným prenosom<br />

G ( s)<br />

S<br />

K<br />

p −Td1s<br />

= e<br />

(3.10)<br />

T1 s + 1<br />

v ktorom časovú konštantu T 1 a dopravné oneskorenie T d1 získame na základe vzťahov<br />

[Vítečková 1998]<br />

T = ,245( t − ), (3.11)<br />

1<br />

1<br />

0,7<br />

t0,<br />

33<br />

T d 1<br />

1,498t<br />

0,33<br />

− 0, 498t<br />

0,7<br />

= , (3.12)<br />

kde doby t<br />

0, 33<br />

a t<br />

0, 7<br />

sú odčítané z prechodovej charakteristiky sústavy (meniča), tak ako<br />

je to zobrazené na obrázku 3.6.<br />

–––––––––––––––––––––––––––––––––––––––––––––––––––––––––––––––––––––––––––––––––––––<br />

ŽILINSKÁ UNIVERZITA V ŽILINE<br />

EF KVES

DIPLOMOVÁ PRÁCA List č. 31<br />

Z dôvodu, že simulačný jazyk Matlab umožňuje veľmi presne zobraziť oba<br />

vyššie uvedené časy zvolil som práve túto metódu identifikácie prenosu meniča, ktorá<br />

dáva prenosovú funkciu v tvare:<br />

0,35<br />

G S<br />

( s)<br />

= (3.13)<br />

3<br />

0,21.10<br />

− s + 1<br />

3.6 Metódy výpočtu spojitých a diskrétnych regulátorov na základe<br />

znalosti matematického modelu (prenosovej funkcie)<br />

V tejto časti opíšem dve metódy na návrh regulátorov ak poznáme prenosovú<br />

funkciu sústavy. Ide o metódu požadovaného modelu a metódu AVO (absolut value<br />

optimum) Návrh regulátorov bude riešený pre stav pri zaťažení meniča, pretože pri<br />

stave naprázdno menič spína rovnako ako pri plnom výkone, čo je spôsobené<br />

charakteristikou meniča.<br />

3.6.1 Návrh regulátorov metódou požadovaného modelu<br />

Metóda požadovaného modelu umožňuje ľahké nastavenie regulátorov pre<br />

základné druhy regulovaných sústav s dopravným oneskorením aj bez neho. Metóda<br />

umožňuje určiť vhodný typ regulátora a nastaviť ho tak aby bola dosiahnutá nulová<br />

regulačná odchýlka pri relatívnom prekmite od 0 do 50% pri skokovej zmene polohy<br />

žiadanej veličiny alebo poruchovej veličiny pôsobiacej na výstupe regulovanej<br />

sústavy.[1]<br />

Pretože v prípade meniča pre zváranie sa jedná o proporcionálnu sústavu bez<br />

dopravného oneskorenia (vzhľadom na časovú konštantu obvodu), bude mať<br />

požadovaný prenos riadenia podľa [1] tvar:<br />

1<br />

GW ( s)<br />

= , (3.14)<br />

T s + 1<br />

W<br />

kde T W je požadovaná časová konštanta regulačného obvodu.<br />

Časovú konštantu T W treba voliť s ohľadom na obmedzenie akčnej veličiny,<br />

maximálne zosilnenie regulátora a vzhľadom na časovú konštantu regulovanej sústavy.<br />

–––––––––––––––––––––––––––––––––––––––––––––––––––––––––––––––––––––––––––––––––––––<br />

ŽILINSKÁ UNIVERZITA V ŽILINE<br />

EF KVES

DIPLOMOVÁ PRÁCA List č. 32<br />

Pre prípad mnou navrhovaných regulátorov som zvolil časovú konštantu<br />

−3<br />

regulačného obvodu T W<br />

= 1.10 s s uvažovaním vyššie uvedených<br />

obmedzení.(viď.obr.3.6).<br />

Potom pre regulovanú sústavu 1.rádu s prenosom v tvare<br />

Kp<br />

G S<br />

( s)<br />

=<br />

(3.15)<br />

T s 1<br />

1<br />

+<br />

s použitím PI regulátora dostávame pre hodnotu integračnej časovej konštanty:<br />

T i<br />

= T 1<br />

, (3.16)<br />

a pre proporcionálnu zložku regulátora:<br />

k<br />

T<br />

i<br />

R<br />

= , (3.17)<br />

K<br />

p<br />

⋅TW<br />

kde<br />

k<br />

R<br />

je zosilnenie proporcionálnej zložky,<br />

K p<br />

je prenos regulovanej sústavy<br />

v ustálenom stave a T<br />

W<br />

je zvolená časová konštanta regulačného obvodu.<br />

Výsledné konštanty vypočítané metódou požadovaného modelu pre menič<br />

0,35<br />

s prenosom G S<br />

( s)<br />

= majú hodnoty:<br />

3<br />

0,21.10<br />

− s + 1<br />

K<br />

i<br />

1 1<br />

= = = 4762<br />

T T<br />

i<br />

1<br />

K<br />

R<br />

−<br />

0,21.10<br />

0,35⋅1.10<br />

3<br />

=<br />

−3<br />

= 0,6<br />

3.6.2 Návrh regulátorov metódou AVO – absolut value optimum<br />

Táto metóda sa spôsob návrhu regulátorov podobá metóde požadovaného<br />

modelu. Pri tejto metóde sa snažíme upraviť tvar prenosovej funkcie na otvorenej<br />

slučke (obr.3.8) na tvar definovaný metódou AVO:<br />

1<br />

G OPEN<br />

( s)<br />

= , (3.18)<br />

2. T ε<br />

(1 + sT ε<br />

)<br />

kde T<br />

ε<br />

je časová konštanta, pomocou ktorej definujeme, za aký čas má regulačný obvod<br />

dosiahnuť ustálenú hodnotu. V tomto prípade je to polovica časovek konštanty<br />

uzavretého riadiaceho obvodu.<br />

–––––––––––––––––––––––––––––––––––––––––––––––––––––––––––––––––––––––––––––––––––––<br />

ŽILINSKÁ UNIVERZITA V ŽILINE<br />

EF KVES

DIPLOMOVÁ PRÁCA List č. 33<br />

u<br />

y<br />

Obr.3.8: Bloková schéma uzavretého riadiaceho obvodu<br />

Prenosovú funkciu otvoreného obvodu získame ako súčin prenosovej funkcie<br />

regulátora a prenosovej funkcie regulovanej sústavy:<br />

k<br />

R<br />

k<br />

P<br />

k<br />

R<br />

(1 + sTi<br />

) k<br />

P<br />

GOPEN<br />

( s)<br />

= GPI<br />

( s)<br />

⋅ G(<br />

s)<br />

= ⋅ = ⋅<br />

(3.19)<br />

(1 + T s)<br />

( sT + 1) T s (1 + T )<br />

i<br />

1 i<br />

1s<br />

k<br />

R<br />

ak T i<br />

= T1<br />

po vydelení dostaneme GOPEN<br />

( s)<br />

= ⋅ k<br />

P<br />

, (3.20)<br />

T s<br />

i<br />

k<br />

ak pre integračnú časovú konštantu platí: T<br />

i<br />

=<br />

k<br />

R<br />

I<br />

, potom môžeme napísať:<br />

1<br />

k<br />

R<br />

1<br />

k<br />

⋅<br />

k<br />

R<br />

I<br />

⋅ k<br />

s<br />

P<br />

k<br />

I<br />

k<br />

=<br />

s<br />

P<br />

1<br />

=<br />

1<br />

k k<br />

I<br />

P<br />

, (3.21)<br />

s<br />

Výraz (3.20) položíme rovný štandardnému tvaru pre metódu AVO a dostaneme:<br />

1<br />

1<br />

k k<br />

I<br />

P<br />

1 1<br />

= ⇒ = 2Tε<br />

(3.22)<br />

2Tε<br />

s(1<br />

+ sTε<br />

) k k<br />

s<br />

I P<br />

Teraz si zvolíme hodnotu časovej konštanty ktorou sa má systém ustáliť: T<br />

–––––––––––––––––––––––––––––––––––––––––––––––––––––––––––––––––––––––––––––––––––––<br />

ŽILINSKÁ UNIVERZITA V ŽILINE<br />

EF KVES<br />

s<br />

−3<br />

ε<br />

= 1.10 .<br />

Stavová veličina potom dosiahne ustálenú hodnotu v čase (2T<br />

) , táto hodnota vyplýva<br />

3<br />

ε<br />

z AVO metódy.<br />

Potom z výrazu (3.22) pre hodnotu integračnej konštanty platí:<br />

k<br />

I<br />

=<br />

k<br />

P<br />

1<br />

⋅ 2 ⋅<br />

T ε<br />

A pre proporcionálnu zložku :<br />

k<br />

R<br />

k I<br />

, (3.23)<br />

= T ε<br />

⋅<br />

(3.24)<br />

Pre menič s prenosom (3.13) majú výsledné časové konštanty hodnoty:<br />

1<br />

k = 1428<br />

−3<br />

0,35.2.1.10<br />

=<br />

I<br />

k<br />

R<br />

= 1,43<br />

Hodnoty konštánt regulátorov vypočítané pomocou metódy AVO sú použité<br />

v riadiacom programe pre mikropočítač ATmega16.

DIPLOMOVÁ PRÁCA List č. 34<br />

3.7 Antiwind-up<br />

Jedná sa o opatrenie, ktoré má zabrániť pokračujúcej integrácii pri generovaní<br />

signálu akčnej veličiny potom, čo akčná veličina dosiahla maximálnu hodnotu<br />

(saturáciu). K nežiadúcemu pokračovaniu činnosti integračnej zložky dochádza vtedy,<br />

keď regulačná odchýlka spôsobuje prekročenie maximálnej hodnoty akčnej veličiny.<br />

Integračná zložka regulátora pokračuje v činnosti až dovtedy, kým regulačná odchýlka<br />

nezmení polaritu a nespôsobí pokles akčnej veličiny pod medznú hodnotu. Akčnej<br />

veličine však trvá určitú dobu, ktorú potrebuje integračná zložka na „ spätné<br />

odintegrovanie“ , kým klesne pod medznú hodnotu tzv. wind-up oneskorenie. Práve<br />

toto oneskorenie je príčinou zhoršenia kvality riadenia. [1]<br />

Schéma PI regulátora s antiwind-up opatrením je na obr. 3.9:<br />

e<br />

P<br />

u´<br />

u<br />

1/T i 1/s<br />

K a<br />

Obr.3.9: Schéma regulátora s antiwind-up<br />

i Lo (t)<br />

I,U [A,V]<br />

u Co (t<br />

i p (t)<br />

u Co (t)<br />

Obr.3.10: priebehy stavových veličín bez opatrenia antiwindup<br />

Priebehy veličín aj s opatrením antiwind-up sú na obr. 2.9.<br />

–––––––––––––––––––––––––––––––––––––––––––––––––––––––––––––––––––––––––––––––––––––<br />

ŽILINSKÁ UNIVERZITA V ŽILINE<br />

EF KVES

DIPLOMOVÁ PRÁCA List č. 35<br />

4.NÁVRH SCHÉMY ZAPOJENIA RIADIACEHO<br />

OBVODU<br />

V tejto časti sa budem zaoberať návrhom schémy riadiaceho obvodu pre menič<br />

pre zvárací transformátor. Ako riadiaci prvok použijem mikropočítač AVR firmy Atmel<br />

a to 16 bitový mikroprocesor ATmega16, spolu s logickými členmi typu AND,NAND<br />

a klopných obvodov typu JK. Ako snímací prvok výstupného prúdu bude použitý LEM<br />

modul s prevodovým pomerom 1:10. Pre riadenie bude použitý vstavaný A/D<br />

prevodník, pomocou ktorého sa prekonvertuje zosnímaná hodnota z LEM modulu na<br />

číslo a 16b čítač/časovač 1 ktorý bude pracovať ako PWM modulátor. Obvody typu<br />

NAND budú použité pri vytváraní 2.(negovaného) kanálu PWM. Logické obvody typu<br />

JK sú použité pre generovanie PSM modulácie. Na vytvorenie „dead time“ pre<br />

tranzistory sú použité RC členy spolu s logickým obvodom AND. Schéma zapojenia<br />

riadiacej časti meniča je na obr.4.1<br />

Obr.4.1: Schéma zapojenia riadiaceho obvodu<br />

–––––––––––––––––––––––––––––––––––––––––––––––––––––––––––––––––––––––––––––––––––––<br />

ŽILINSKÁ UNIVERZITA V ŽILINE<br />

EF KVES

DIPLOMOVÁ PRÁCA List č. 36<br />

4.1 Opis jednotlivých obvodov a ich funkcie<br />

V tejto časti sa budem zaoberať opisom jednotlivých obvodov slúžiacich na<br />

riadenie a to smerom od snímača prúdu na sekundárnej strane meniča až po optočleny<br />

ktoré galvanicky oddeľujú riadiaci signál od silovej časti meniča. Najprv však<br />

všeobecne opíšem mikropočítač Atmel AVR ATmega 16.<br />

4.1.1 Štruktúra AVR ATmega 16<br />

AVR - rodina sú nízkopríkonové 8-bitové mikroprocesory s RISC<br />

architektúrou. Je použitá harwardská štruktúra, u ktorej je oddelená programová<br />

a dátová pamäť. ATmega-séria poskytuje bežné výhody RISC-architektúry, tj.<br />

jednocyklové inštrukcie, vyššiu taktovaciu frekvenciu spojenú s vyšším pracovným<br />

výkonom rovnako ako aj efektívnu optimalizáciu prekladu kódu programu. Na čipe<br />

procesora je umiestnená vlastná procesorová jednotka CPU, ktorá je vnútornou<br />

spoločnou zbernicou prepojená s pamäťou programu, s pamäťou RAM, so vstupnovýstupnými<br />

portami, ktoré zabezpečujú styk procesoru s vonkajšími perifériami.<br />

Hlavnou funkciou jadra CPU je zabezpečiť korektné vykonanie inštrukcií programu.<br />

CPU musí byť navyše schopný zabezpečiť prístup do pamäte, prevádzať výpočty, riadiť<br />

periférie a obsluhovať prerušenia. Ďalej je na čipe umiestnený 10-bitový 8-kanálový<br />

A/D prevodník spolu so štyrmi PWM modulátormi ktoré zabezpečujú generovanie<br />

PWM.<br />

Výpočtový výkon týchto mikroprocesorov je veľmi vysoký až 16MIPS pri<br />

16MHz pracovnej frekvencii. Pre jednoduchší styk s perifériami je procesor vybavený<br />

radičom prerušení, ktorý spracováva zdroje prerušenia.<br />

Mikropočítače rady ATmega16 obsahujú :<br />

• 16KB vlastnej programovateľnej FLASH pamäte<br />

• 512B EEPROM<br />

• 1KB vnútornej SRAM pamäte<br />

• Možnosť krokovať program v aplikácii – JTAG<br />

• Jeden 16bitový časovač/čítač<br />

• Dva 8bitové čítače/časovače<br />

• 4 kanály PWM<br />

–––––––––––––––––––––––––––––––––––––––––––––––––––––––––––––––––––––––––––––––––––––<br />

ŽILINSKÁ UNIVERZITA V ŽILINE<br />

EF KVES

DIPLOMOVÁ PRÁCA List č. 37<br />

• 8 kanálový 10bitový A/D prevodník<br />

• SPI – sériové nahrávanie programu priamo v aplikáciách<br />

• Brown-out detector – detekcia poklesu napájacieho napätia<br />

• Šesť úsporných režimov (Idle, ADC Noise Reduction, Power Save, Power<br />

Down, Stanby, Extented Standby)<br />

• Ochranný mechanizmus proti vykrádaniu softwaru<br />

Obr.4.2: Rozloženie vývodov na čipe AVR ATmega16<br />

Obr.4.3: Bloková schéma jadra mikroprocesora ATmega16<br />

–––––––––––––––––––––––––––––––––––––––––––––––––––––––––––––––––––––––––––––––––––––<br />

ŽILINSKÁ UNIVERZITA V ŽILINE<br />

EF KVES

DIPLOMOVÁ PRÁCA List č. 38<br />

AVR - mikroprocesory môžu výkonom prekonať iné 8-bitové i niektoré 16-<br />

bitové mikroprocesory, pričom ich cena sa pohybuje na veľmi prijateľnej úrovni.<br />

Jedinou nevýhodou rady ATmega16 je pomerne pomalý A/D prevodník, ktorý<br />

pre určité aplikácie môže byť nedostačujúci.<br />

4.1.2 Porty<br />

Všetky porty mikropočítača ATmega16 majú funkciu Read-Modify-Write (čítajzmeň-zapíš)<br />

čo znamená, že každý bit jednotlivých portov môže byť zmenený na<br />

vstupný, alebo výstupný, bez zmeny ostatných bitov daného portu (pinov). Každý<br />

vývod portu je schopný pracovať na úrovni TTL, bez potreby budiacich obvodov. Na<br />

všetkých pinoch sú pripojené ochranné diódy a kondenzátor na zníženie rušenia.<br />

Označenie daných portov používané v ďalšom texte a v programe má<br />

nasledujúci význam: PORTxn – znamená že používame jeden z I/O portov,označený<br />

písmenom x a pripájame jeho bit označený n. Napríklad PORTB3 znamená, že sa jedná<br />

o port B, tretí pin. Mikropočítač ATmega16 má 4 porty A,B,C,D, pričom PORTA je<br />

využívaný A/D prevodníkom, ostatné porty využívajú čítače/časovače a iné obvody.<br />

Jednotlivé porty sa ovládajú registrom DDRx, pomocou ktorého nastavujeme<br />

smer toku dát. Inštrukcia PORTx slúži na zápis údajov a inštrukcia PINx slúži len na<br />

čítanie z jednotlivých pinov.<br />

4.1.3 Zabudovaný A/D prevodník<br />

Mikropočítače ATmega16 obsahujú zabudovaný 10 bitový A/D prevodník,<br />

ktorý pracuje metódou postupnej aproximácie. Prevodník je pripojený na 8 kanálový<br />

analógový multiplexor(PORTA), takže je možné snímať až 8 kanálov.<br />

A/D prevodník má tieto základné parametre<br />

• 10bitové rozlíšenie pri frekvencii 50 – 200kHz<br />

• Doba prevodu 13-260μs<br />

• 8 multiplexovaných jednoduchých vstupov<br />

• 7 diferenciálnych vstupov<br />

• Voliteľný zdroj referenčného napätia<br />

• Jednoduchý prevod alebo voľný beh<br />

–––––––––––––––––––––––––––––––––––––––––––––––––––––––––––––––––––––––––––––––––––––<br />

ŽILINSKÁ UNIVERZITA V ŽILINE<br />

EF KVES

DIPLOMOVÁ PRÁCA List č. 39<br />

Na každý analógový vstup je potrebné pripojiť ochranný rezistor a odrušovací<br />

kondenzátor.<br />

Obr.4.4: Spôsob pripojenia analógových vstupov prevodníka<br />

Prevodník obsahuje vzorkovač (obvod S/H – Sample and Hold) spojený zo<br />

zosilňovačom, ktorý udržuje vstupné napätie v priebehu prevodu na stabilnej úrovni.<br />

A/D prevodník má oddelené napájanie pomocou vývodov AV CC (napájacie napätie)<br />

a AGND (analógová zem), pričom vývod AGND musí byť spojený s GND len<br />

v jednom bode, a veľkosť AV CC sa musí rovnať V CC ±0,3V.<br />

Referenčné napätie prevodníka môže byť 2,56V, AV CC , alebo AREF. Prvé dve<br />

napätia sú priamo na čipe mikropočítača, napätie AREF sa pripája na externý pin<br />

mikropočítača, ktorý je potrebné ošetriť kondenzátorom kvôli zníženiu rušenia.<br />

Obr.4.5: Pripojenie napájacích pinov prevodníka<br />

–––––––––––––––––––––––––––––––––––––––––––––––––––––––––––––––––––––––––––––––––––––<br />

ŽILINSKÁ UNIVERZITA V ŽILINE<br />

EF KVES

DIPLOMOVÁ PRÁCA List č. 40<br />

Funkcie<br />

A/D prevodník prevádza vstupné analógové napätie na 10bitovú číslicovú<br />

hodnotu algoritmom postupnej aproximácie. Minimum je reprezentované AGND<br />

a maximum AREF – 1LSB. Vstupné analógové kanály sa volia zápisom bitov do<br />

registra ADMUX. Všetky vstupy sú konfigurované ako SE (merajú napätie voči<br />

AGND).<br />

Prevodník sa zapína zápisom log.1 na bit ADEN v registri ADCSRA. 10bit<br />

výsledok prevodu je zapísaný v registroch ADCH a ADCL.<br />

A/D prevodník môže pracovať v dvoch režimoch – volia sa bitom ADFR<br />

z registra ADCSR):<br />

• Jednoduchý prevod (Single Conversion) – každý prevod musí byť vyvolaný<br />

užívateľom<br />

• Voľný beh (Free Running) – prevody sú periodicky opakované bez nutnosti<br />

opakovaného programového spúšťania<br />

Postupná aproximácia potrebuje vstupný hodinový kmitočet v rozsahu 50 až<br />

200kHz pre dosiahnutie maximálnej presnosti. Ak je požadované nižšie rozlíšenie ako<br />

10bit , môže byť vzorkovacia frekvencia vyššia – tým dosiahneme vyššiu vzorkovaciu<br />

rýchlosť. Modul A/D prevodníka obsahuje preddeličku, ktorá delí frekvenciu<br />

systémových hodín na frekvenciu prijateľnú pre A/D prevodník.<br />