Please purchase PDF Split-Merge on www.verypdf.com to ... - Patrz

Please purchase PDF Split-Merge on www.verypdf.com to ... - Patrz

Please purchase PDF Split-Merge on www.verypdf.com to ... - Patrz

- TAGS

- purchase

- patrz

- www30.patrz.pl

Create successful ePaper yourself

Turn your PDF publications into a flip-book with our unique Google optimized e-Paper software.

114 Urzadzenia peryferyjne i interfejsy<br />

przejscia linii na pewien czas w stan 1, nawet gdy transmisja kolejnej ramki rozpoczyna<br />

sie natychmiast po zak<strong>on</strong>czeniu nadawania poprzedniej. Ulatwia <strong>to</strong> wykrycie<br />

kolejnego bitu startu, ale nie jest k<strong>on</strong>ieczne. Stad przykladowo, ilosc bitów s<strong>to</strong>pu moze<br />

wynosic zero, jeden, pól<strong>to</strong>ra lub dwa. Oczywiscie pól<strong>to</strong>ra bitu s<strong>to</strong>pu oznacza czas<br />

trwania jedynki przez pól<strong>to</strong>ra okresu zegara nadawcz%dbiorczego. Z roli, jaka pelni<br />

bit s<strong>to</strong>pu, wynika tez jego war<strong>to</strong>sc. Musi <strong>on</strong> miec zawsze przeciwny znak niz bit startu.<br />

Podsumowujac, w transmisji szeregowej asynchr<strong>on</strong>icznej zapewniamy synctr0nizacje<br />

zegarów nadawczego i odbiorczego na czas transmisji jednej rarnki. Po odebraniu<br />

znaku zegar odbiorczy jest wylaczany i odbiornik oczekuje na kolejny bit startu.<br />

Nadajnik w przypadku braku informacji do przesylania utrzymuje na linii stan<br />

wysoki (1).<br />

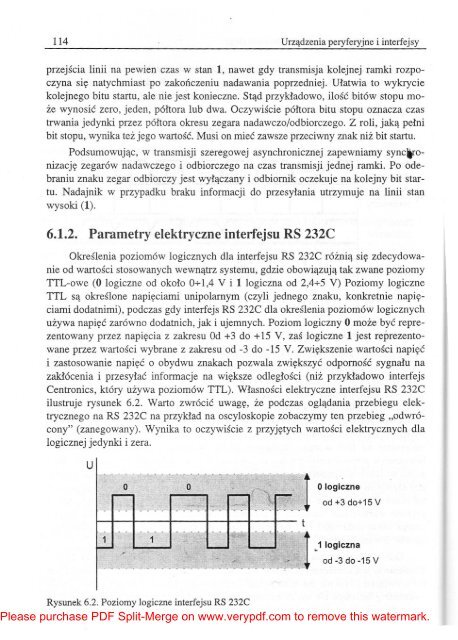

6.1.2. Parametry elektryczne interfejsu RS 232C<br />

Okreslenia poziomów logicznych dla interfejsu RS 232C róznia sie zdecydowanie<br />

od war<strong>to</strong>sci s<strong>to</strong>sowanych wewnatrz systemu, gdzie obowiazuja tak zwane poziomy<br />

TTL-owe (O logiczne od okolo 0--;-1,4V i 1logiczna od 2,4+5 V) Poziomy logiczne<br />

TTL sa okresl<strong>on</strong>e napieciami unipolarnym (czyli jednego znaku, k<strong>on</strong>kretnie napieciami<br />

dodatnimi), podczas gdy interfejs RS 232C dla okreslenia poziomów logicznych<br />

uzywa napiec zarówno dodatnich, jak i ujemnych. Poziom logiczny O moze byc reprezen<strong>to</strong>wany<br />

przez napiecia z zakresu Od +3 do +15 V, zas logiczne 1jest reprezen<strong>to</strong>wane<br />

przez war<strong>to</strong>sci wybrane z zakresu od -3 do -15 V. Zwiekszenie war<strong>to</strong>sci napiec<br />

i zas<strong>to</strong>sowanie napiec o obydwu znakach pozwala zwiekszyc odpornosc sygnalu na<br />

zaklócenia i przesylac informacje na wieksze odleglosci (niz przykladowo interfejs<br />

Centr<strong>on</strong>ics, który uzywa poziomów TTL). Wlasnosci elektryczne interfejsu RS 232C<br />

ilustruje rysunek 6.2. War<strong>to</strong> zwrócic uwage, ze podczas ogladania przebiegu elektrycznego<br />

na RS 232C na przyklad na oscyloskopie zobaczymy ten przebieg "odwróc<strong>on</strong>y"<br />

(zanegowany). Wynika <strong>to</strong> oczywiscie z przyjetych war<strong>to</strong>sci elektrycznych dla<br />

logicznej jedynki i zera.<br />

u<br />

o logiczne<br />

od +3 do+15 V<br />

Rysunek 6.2. Poziomy logiczne interfejsu RS 232C<br />

<str<strong>on</strong>g>Please</str<strong>on</strong>g> <str<strong>on</strong>g>purchase</str<strong>on</strong>g> <str<strong>on</strong>g>PDF</str<strong>on</strong>g> <str<strong>on</strong>g>Split</str<strong>on</strong>g>-<str<strong>on</strong>g>Merge</str<strong>on</strong>g> <strong>on</strong> <strong>www</strong>.<strong>verypdf</strong>.<strong>com</strong> <strong>to</strong> remove this watermark.

![[DOWNLOAD] Zapisz na dysku - Patrz](https://img.yumpu.com/44027585/1/177x260/download-zapisz-na-dysku-patrz.jpg?quality=85)

![[DOWNLOAD] Zapisz na dysku - Patrz](https://img.yumpu.com/34635637/1/184x260/download-zapisz-na-dysku-patrz.jpg?quality=85)