ETI VHDL Grundlagen - LRR

ETI VHDL Grundlagen - LRR

ETI VHDL Grundlagen - LRR

Sie wollen auch ein ePaper? Erhöhen Sie die Reichweite Ihrer Titel.

YUMPU macht aus Druck-PDFs automatisch weboptimierte ePaper, die Google liebt.

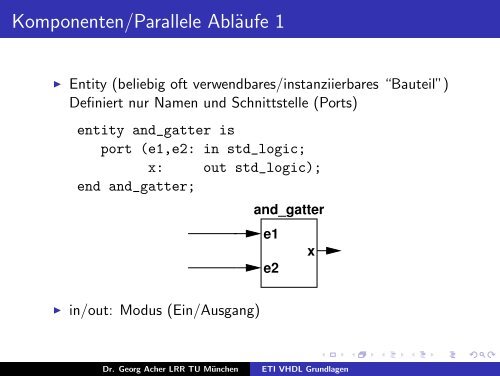

Komponenten/Parallele Abläufe 1<br />

◮ Entity (beliebig oft verwendbares/instanziierbares “Bauteil”)<br />

Definiert nur Namen und Schnittstelle (Ports)<br />

entity and_gatter is<br />

port (e1,e2: in std_logic;<br />

x: out std_logic);<br />

end and_gatter;<br />

◮ in/out: Modus (Ein/Ausgang)<br />

and_gatter<br />

e1<br />

e2<br />

Dr. Georg Acher <strong>LRR</strong> TU München <strong>ETI</strong> <strong>VHDL</strong> <strong>Grundlagen</strong><br />

x