ETI VHDL Grundlagen - LRR

ETI VHDL Grundlagen - LRR

ETI VHDL Grundlagen - LRR

Erfolgreiche ePaper selbst erstellen

Machen Sie aus Ihren PDF Publikationen ein blätterbares Flipbook mit unserer einzigartigen Google optimierten e-Paper Software.

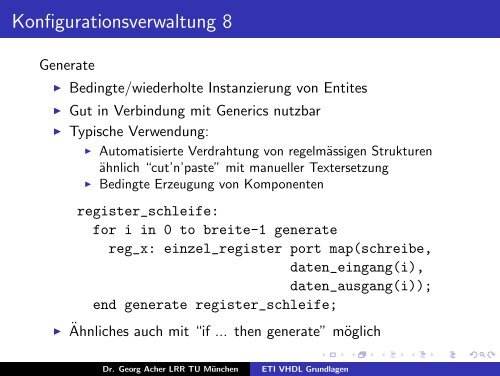

Konfigurationsverwaltung 8<br />

Generate<br />

◮ Bedingte/wiederholte Instanzierung von Entites<br />

◮ Gut in Verbindung mit Generics nutzbar<br />

◮ Typische Verwendung:<br />

◮ Automatisierte Verdrahtung von regelmässigen Strukturen<br />

ähnlich “cut’n’paste” mit manueller Textersetzung<br />

◮ Bedingte Erzeugung von Komponenten<br />

register_schleife:<br />

for i in 0 to breite-1 generate<br />

reg_x: einzel_register port map(schreibe,<br />

daten_eingang(i),<br />

daten_ausgang(i));<br />

end generate register_schleife;<br />

◮ Ähnliches auch mit “if ... then generate” möglich<br />

Dr. Georg Acher <strong>LRR</strong> TU München <strong>ETI</strong> <strong>VHDL</strong> <strong>Grundlagen</strong>