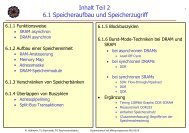

Interface-Baustein - Ra.informatik.tu-darmstadt.de

Interface-Baustein - Ra.informatik.tu-darmstadt.de

Interface-Baustein - Ra.informatik.tu-darmstadt.de

Sie wollen auch ein ePaper? Erhöhen Sie die Reichweite Ihrer Titel.

YUMPU macht aus Druck-PDFs automatisch weboptimierte ePaper, die Google liebt.

Synchronisation durch Busy-Waiting<br />

8<br />

READY-Bit wird durch das READY-Signal von <strong>de</strong>r Peripherie gesetzt<br />

<br />

<br />

Ausgabe: Peripherie hat die Daten aus <strong>de</strong>m DR übernommen (DATA ACK).<br />

Eingabe: Peripherie hat Daten bereitgestellt bzw. hat die Daten in das Datenregister<br />

<strong>de</strong>s <strong>Interface</strong>s geschrieben (DATA AVAILABLE).<br />

Abfrage <strong>de</strong>s READY-Bits in Warteschleife o<strong>de</strong>r periodisch<br />

Zurücksetzen <strong>de</strong>r READY-Bits<br />

<br />

<br />

Nachteile<br />

<br />

<br />

<br />

programmgesteuert<br />

automatisch<br />

• Ausgabe: mit <strong>de</strong>m Schreiben <strong>de</strong>s Da<strong>tu</strong>ms durch <strong>de</strong>n Prozessor (DACk write DACK:=0)<br />

• Eingabe: mit <strong>de</strong>m Lesen <strong>de</strong>s Da<strong>tu</strong>ms durch <strong>de</strong>n Prozessor (DAV read DAV:=0)<br />

Hoher Zeitverbrauch durch die wie<strong>de</strong>rholten Abfragen<br />

Prozessor muss schneller als die Peripherie sein. (Kein Handshake zum Anhalten <strong>de</strong>r<br />

P.)<br />

Gleichzeitige Bearbei<strong>tu</strong>ng mehrerer EA-Vorgänge kann zeitkritisch wer<strong>de</strong>n<br />

R. Hoffmann, TU Darmstadt, FG Rechnerarchitek<strong>tu</strong>r Systementwurf mit Mikroprozessoren WS 09/10