Interface-Baustein - Ra.informatik.tu-darmstadt.de

Interface-Baustein - Ra.informatik.tu-darmstadt.de

Interface-Baustein - Ra.informatik.tu-darmstadt.de

Sie wollen auch ein ePaper? Erhöhen Sie die Reichweite Ihrer Titel.

YUMPU macht aus Druck-PDFs automatisch weboptimierte ePaper, die Google liebt.

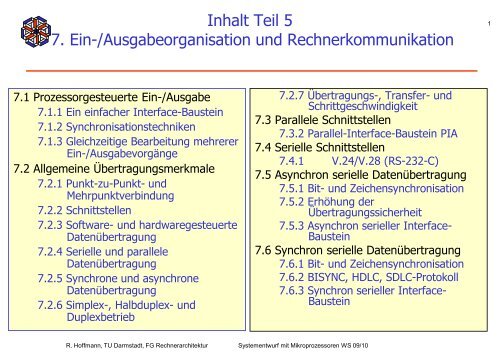

Inhalt Teil 5<br />

7. Ein-/Ausgabeorganisation und Rechnerkommunikation<br />

1<br />

7.1 Prozessorgesteuerte Ein-/Ausgabe<br />

7.1.1 Ein einfacher <strong>Interface</strong>-<strong>Baustein</strong><br />

7.1.2 Synchronisationstechniken<br />

7.1.3 Gleichzeitige Bearbei<strong>tu</strong>ng mehrerer<br />

Ein-/Ausgabevorgänge<br />

7.2 Allgemeine Übertragungsmerkmale<br />

7.2.1 Punkt-zu-Punkt- und<br />

Mehrpunktverbindung<br />

7.2.2 Schnittstellen<br />

7.2.3 Software- und hardwaregesteuerte<br />

Datenübertragung<br />

7.2.4 Serielle und parallele<br />

Datenübertragung<br />

7.2.5 Synchrone und asynchrone<br />

Datenübertragung<br />

7.2.6 Simplex-, Halbduplex- und<br />

Duplexbetrieb<br />

7.2.7 Übertragungs-, Transfer- und<br />

Schrittgeschwindigkeit<br />

7.3 Parallele Schnittstellen<br />

7.3.2 Parallel-<strong>Interface</strong>-<strong>Baustein</strong> PIA<br />

7.4 Serielle Schnittstellen<br />

7.4.1 V.24/V.28 (RS-232-C)<br />

7.5 Asynchron serielle Datenübertragung<br />

7.5.1 Bit- und Zeichensynchronisation<br />

7.5.2 Erhöhung <strong>de</strong>r<br />

Übertragungssicherheit<br />

7.5.3 Asynchron serieller <strong>Interface</strong>-<br />

<strong>Baustein</strong><br />

7.6 Synchron serielle Datenübertragung<br />

7.6.1 Bit- und Zeichensynchronisation<br />

7.6.2 BISYNC, HDLC, SDLC-Protokoll<br />

7.6.3 Synchron serieller <strong>Interface</strong>-<br />

<strong>Baustein</strong><br />

R. Hoffmann, TU Darmstadt, FG Rechnerarchitek<strong>tu</strong>r Systementwurf mit Mikroprozessoren WS 09/10

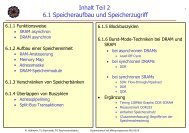

7. Ein-/Ausgabeorganisation<br />

und Rechnerkommunikation<br />

2<br />

Problem: Die Peripheriegeräte können nicht direkt an einen schnellen Bus<br />

(Prozessorbus, Systembus) angeschlossen wer<strong>de</strong>n.<br />

<strong>Interface</strong>-<strong>Baustein</strong> (EA-Einheit, IO Port) führt die Anpassung <strong>de</strong>r Protokolle<br />

durch.<br />

Steuerung <strong>de</strong>r EA durch<br />

Prozessor (prozessorgesteuerte EA)<br />

Controller mit Master-Funktion (z.B. DMA-Controller)<br />

programmierbaren EA-Prozessor<br />

R. Hoffmann, TU Darmstadt, FG Rechnerarchitek<strong>tu</strong>r Systementwurf mit Mikroprozessoren WS 09/10

7.1 Prozessorgesteuerte Ein-/Ausgabe<br />

3<br />

Aktionen eines EA-Vorgangs<br />

Start<br />

Gerät in bestimmten Zustand bringen<br />

z.B. Plattenzugriffsarm positionieren<br />

Datenübertragung und Synchronisation<br />

Bei Blockübertragung: auch<br />

Datenelementzähler erhöhen<br />

und Adressen erhöhen<br />

Sta<strong>tu</strong>sinformation lesen und auswerten<br />

z. B. zur Fehlerbehandlung<br />

Stop<br />

R. Hoffmann, TU Darmstadt, FG Rechnerarchitek<strong>tu</strong>r Systementwurf mit Mikroprozessoren WS 09/10

7.1.1 Ein einfacher <strong>Interface</strong>-<strong>Baustein</strong><br />

4<br />

<br />

<br />

Einfachster <strong>Interface</strong>-<strong>Baustein</strong>: Datenregister, liegt im Speicher- o<strong>de</strong>r EA-<br />

Adressraum<br />

An<strong>de</strong>re <strong>Interface</strong>-<strong>Baustein</strong>e besitzen serielle o<strong>de</strong>r parallele Schnittstelle zur<br />

Peripherie (peripherer Datenweg).<br />

Ein <strong>Interface</strong>-<strong>Baustein</strong> besitzt im allgemeinen folgen<strong>de</strong> Register:<br />

Steuerregister (control register) CR, zur Auswahl bestimmter Kommandos,<br />

Betriebsarten, Übertragungsprotokolle<br />

Sta<strong>tu</strong>sregister (sta<strong>tu</strong>s register) SR, zur Rückmeldung von Zustandsinformationen<br />

an <strong>de</strong>n Prozessor (z. B. zur Synchronisation, Interruptverarbei<strong>tu</strong>ng)<br />

Datenregister (data register) DR, auch getrennt für die Eingabe bzw. Ausgabe. (Die<br />

Eingabe kann auch über einen ungepufferten Eingabedatenweg erfolgen.)<br />

R. Hoffmann, TU Darmstadt, FG Rechnerarchitek<strong>tu</strong>r Systementwurf mit Mikroprozessoren WS 09/10

Systemstruk<strong>tu</strong>r mit <strong>Interface</strong>-<strong>Baustein</strong>en<br />

5<br />

R. Hoffmann, TU Darmstadt, FG Rechnerarchitek<strong>tu</strong>r Systementwurf mit Mikroprozessoren WS 09/10

7.1.2 Synchronisationstechniken<br />

6<br />

Prozessor <strong>Interface</strong> Peripheriegerät Benutzer<br />

ggf.<br />

Synchronisation<br />

Synchronisation<br />

Synchronisation<br />

Synchronisationsinformation, Synchronisationszeitpunkte<br />

Alternativen<br />

<br />

<br />

<br />

Ist eingebettet in <strong>de</strong>n Datenstrom (vergl. asynchron serielle Übertragung).<br />

Übertragung wird durch Handshake kontrolliert<br />

o<strong>de</strong>r fin<strong>de</strong>t in einem vorgegebenen Zeitraster / Protokoll statt.<br />

R. Hoffmann, TU Darmstadt, FG Rechnerarchitek<strong>tu</strong>r Systementwurf mit Mikroprozessoren WS 09/10

Synchronisation durch Busy-Waiting<br />

7<br />

Prozessor wartet<br />

(Warteschleife, o<strong>de</strong>r in<br />

regelmäßigen Abstän<strong>de</strong>n)<br />

auf ein gesetztes READY-<br />

Bit im Sta<strong>tu</strong>sregister<br />

READY=<br />

DAV: Eingabe<br />

if READY-Bit = true then<br />

goto EA-Routine<br />

DACK: Ausgabe<br />

R. Hoffmann, TU Darmstadt, FG Rechnerarchitek<strong>tu</strong>r Systementwurf mit Mikroprozessoren WS 09/10

Synchronisation durch Busy-Waiting<br />

8<br />

READY-Bit wird durch das READY-Signal von <strong>de</strong>r Peripherie gesetzt<br />

<br />

<br />

Ausgabe: Peripherie hat die Daten aus <strong>de</strong>m DR übernommen (DATA ACK).<br />

Eingabe: Peripherie hat Daten bereitgestellt bzw. hat die Daten in das Datenregister<br />

<strong>de</strong>s <strong>Interface</strong>s geschrieben (DATA AVAILABLE).<br />

Abfrage <strong>de</strong>s READY-Bits in Warteschleife o<strong>de</strong>r periodisch<br />

Zurücksetzen <strong>de</strong>r READY-Bits<br />

<br />

<br />

Nachteile<br />

<br />

<br />

<br />

programmgesteuert<br />

automatisch<br />

• Ausgabe: mit <strong>de</strong>m Schreiben <strong>de</strong>s Da<strong>tu</strong>ms durch <strong>de</strong>n Prozessor (DACk write DACK:=0)<br />

• Eingabe: mit <strong>de</strong>m Lesen <strong>de</strong>s Da<strong>tu</strong>ms durch <strong>de</strong>n Prozessor (DAV read DAV:=0)<br />

Hoher Zeitverbrauch durch die wie<strong>de</strong>rholten Abfragen<br />

Prozessor muss schneller als die Peripherie sein. (Kein Handshake zum Anhalten <strong>de</strong>r<br />

P.)<br />

Gleichzeitige Bearbei<strong>tu</strong>ng mehrerer EA-Vorgänge kann zeitkritisch wer<strong>de</strong>n<br />

R. Hoffmann, TU Darmstadt, FG Rechnerarchitek<strong>tu</strong>r Systementwurf mit Mikroprozessoren WS 09/10

Synchronisation durch Programmunterbrechung<br />

9<br />

<br />

<br />

<br />

<br />

<br />

READY-Bit wirkt als<br />

Interruptsignal.<br />

Laufen<strong>de</strong>s Programm wird durch<br />

eine EA-Service-Routine<br />

unterbrochen.<br />

Durch <strong>de</strong>n Organisationsaufwand<br />

entsteht eine Zeitverzögerung<br />

bis zur ersten Reaktion.<br />

Vorteil: Prozessor ist nicht mit<br />

<strong>de</strong>m Warten beschäftigt.<br />

Beachte auch hier: Die EA-<br />

Routine <strong>de</strong>s Prozessors muss<br />

schneller als die Peripherie sein,<br />

falls <strong>de</strong>r Prozessor die Peripherie<br />

nicht bremsen kann. - Man<br />

spricht dann auch von <strong>de</strong>r<br />

freilaufen<strong>de</strong>n EA.<br />

R. Hoffmann, TU Darmstadt, FG Rechnerarchitek<strong>tu</strong>r Systementwurf mit Mikroprozessoren WS 09/10

Allgemeines Prinzip: Sicherer Datentransport mit<br />

Handshakes (Wdh.)<br />

10<br />

Sen<strong>de</strong>r:<br />

Empfänger:<br />

Daten stehen bereit (Data available DAV)<br />

Daten abgeholt (Data acknowledge DACK), erneut bereit<br />

Auffor<strong>de</strong>rung<br />

zum Empfangen<br />

Empfangsbereit<br />

MASTER<br />

DAV<br />

SLAVE<br />

Data<br />

WRITE<br />

DACK<br />

Auffor<strong>de</strong>rung<br />

zum Sen<strong>de</strong>n<br />

Sen<strong>de</strong>bereit<br />

MASTER<br />

DAV<br />

SLAVE<br />

Data<br />

DACK<br />

READ<br />

R. Hoffmann, TU Darmstadt, FG Rechnerarchitek<strong>tu</strong>r Systementwurf mit Mikroprozessoren WS 09/10

Synchronisation durch Handshaking: Ausgabe<br />

11<br />

Prozessor<br />

2<br />

[1]<br />

<strong>Interface</strong><br />

READY(DACK)<br />

3<br />

5<br />

ACKN(DAV)<br />

Peripherie<br />

4<br />

Da<strong>tu</strong>m<br />

1. on READY: Prozessor (Interrupt-SR o<strong>de</strong>r Busy-Waiting) transportiert das<br />

nächste Da<strong>tu</strong>m in das <strong>Interface</strong> und mel<strong>de</strong>t Bereitstellung mit<br />

ACKN(DAV)<br />

2. on ACKN: Peripherie holt Da<strong>tu</strong>m aus <strong>de</strong>m <strong>Interface</strong>-DR ab und bestätigt<br />

mit READY(DACK)<br />

R. Hoffmann, TU Darmstadt, FG Rechnerarchitek<strong>tu</strong>r Systementwurf mit Mikroprozessoren WS 09/10

Synchronisation durch Handshaking: Eingabe<br />

12<br />

Prozessor<br />

5<br />

4<br />

READY(DAV)<br />

3<br />

5, [1]<br />

ACKN(DACK)<br />

Peripherie<br />

2<br />

<strong>Interface</strong><br />

1. on ACKN : Peripherie überträgt das nächste Da<strong>tu</strong>m in das <strong>Interface</strong> und<br />

mel<strong>de</strong>t die Bereitstellung mit READY (DAV)<br />

2. on READY: Prozessor (Interrupt o<strong>de</strong>r Busy-Waiting) liest das Da<strong>tu</strong>m aus<br />

<strong>de</strong>m <strong>Interface</strong>-DR, das mit ACKN(DACK) quittiert.<br />

R. Hoffmann, TU Darmstadt, FG Rechnerarchitek<strong>tu</strong>r Systementwurf mit Mikroprozessoren WS 09/10

Synchronisation durch Handshaking<br />

Hardware<br />

13<br />

R. Hoffmann, TU Darmstadt, FG Rechnerarchitek<strong>tu</strong>r Systementwurf mit Mikroprozessoren WS 09/10

Beispiel 7.1: Dateneingabe mit Handshake und<br />

Busy-Waiting<br />

14<br />

128 Bytes sollen über<br />

das 8-Bit-Datenregister<br />

DR in einen<br />

Speicherbereich ab <strong>de</strong>r<br />

Adresse BUFFER<br />

eingelesen wer<strong>de</strong>n.<br />

Das READY-Signal<br />

wird im 8-Bit-<br />

<strong>Interface</strong>-<br />

Sta<strong>tu</strong>sregister SR,<br />

Bitposition 7,<br />

zwischengespeichert.<br />

(Der <strong>Interface</strong>-<strong>Baustein</strong><br />

kann keinen Interrupt<br />

auslösen, weil das dieser<br />

Position zugeordnete<br />

Interrupt-Enable-Bit<br />

zurückgesetzt wur<strong>de</strong>.)<br />

automatisch<br />

DR<br />

in <strong>de</strong>n Speicher<br />

R. Hoffmann, TU Darmstadt, FG Rechnerarchitek<strong>tu</strong>r Systementwurf mit Mikroprozessoren WS 09/10

Beispiel 7.2: Dateneingabe mit Handshake und<br />

Programmunterbrechung<br />

15<br />

Das Interrupt-Enable-Bit ist<br />

vorher gesetzt wor<strong>de</strong>n.<br />

Dadurch kann das <strong>Interface</strong><br />

ein Interruptsignal erzeugen,<br />

nach<strong>de</strong>m SR7 durch READY<br />

gesetzt wur<strong>de</strong>.<br />

Ansonsten wie Beispiel 6.1.<br />

READY SR7 <br />

if IRENABLED then IRQ#<br />

Globaler Buffer-<br />

Pointer BUPTR<br />

Interrupt<br />

automatisch<br />

R0 retten<br />

R. Hoffmann, TU Darmstadt, FG Rechnerarchitek<strong>tu</strong>r Systementwurf mit Mikroprozessoren WS 09/10

X-ON/OFF-Synchronisation<br />

(Software-Flusssteuerung, software data flow control)<br />

16<br />

Empfänger empfängt Daten in einem Puffer (z. B. Drucker). Zur Vermeidung eines<br />

Datenverlustes muss <strong>de</strong>r Empfänger <strong>de</strong>n Datenstrom anhalten können.<br />

<br />

Durch Rücksen<strong>de</strong>n von X-OFF (13hex, <strong>de</strong>vice control) wird <strong>de</strong>r Sen<strong>de</strong>r<br />

veranlasst, <strong>de</strong>n Sen<strong>de</strong>vorgang zu unterbrechen.<br />

<br />

Durch X-ON (11hex, <strong>de</strong>vice control) wird <strong>de</strong>r Sen<strong>de</strong>r veranlasst,<br />

fortzufahren.<br />

Empfänger<br />

Sen<strong>de</strong>r<br />

warte mal<br />

mach weiter<br />

X-OFF<br />

X-ON<br />

R. Hoffmann, TU Darmstadt, FG Rechnerarchitek<strong>tu</strong>r Systementwurf mit Mikroprozessoren WS 09/10

7.1.3 Gleichzeitige Bearbei<strong>tu</strong>ng mehrerer Ein-<br />

/Ausgabevorgänge<br />

17<br />

Ein EA-Vorgang kann durch einen weiteren mit höherer Priorität<br />

unterbrochen wer<strong>de</strong>n. Der unterbrochene EA-Vorgang muss<br />

anschließend korrekt zu En<strong>de</strong> geführt wer<strong>de</strong>n.<br />

Polling<br />

<br />

<strong>Interface</strong>s, die auf einer Prioritätsebene liegen, liefern ein gemeinsames<br />

Interrupt-Signal (wired-or).<br />

<br />

Die Sta<strong>tu</strong>sregister (READY-Bits) <strong>de</strong>r <strong>Interface</strong>s wer<strong>de</strong>n in einer <strong>de</strong>finierten<br />

zyklischen Sequenz getestet, bis eine Anfor<strong>de</strong>rung vorliegt. Dann erfolgt die<br />

Verzweigung in die EA-Routine. In <strong>de</strong>m <strong>Interface</strong>, das bedient wird, wird<br />

die Anfor<strong>de</strong>rung (READY-Bit) zurückgesetzt.<br />

R. Hoffmann, TU Darmstadt, FG Rechnerarchitek<strong>tu</strong>r Systementwurf mit Mikroprozessoren WS 09/10

Polling<br />

18<br />

alle Anfor<strong>de</strong>rungen<br />

wer<strong>de</strong>n<br />

nacheinan<strong>de</strong>r<br />

bedient<br />

"fair"<br />

Bei je<strong>de</strong>r<br />

Bedienung wird<br />

eine feste<br />

Reihenfolge<br />

eingehalten<br />

"unfair"<br />

R. Hoffmann, TU Darmstadt, FG Rechnerarchitek<strong>tu</strong>r Systementwurf mit Mikroprozessoren WS 09/10

Unterbrechbarkeit von Ein-/Ausgabeprogrammen<br />

19<br />

Busy-Waiting-Routine: Anfor<strong>de</strong>rung höherer Priorität kann nur dann<br />

berücksichtigt wer<strong>de</strong>n, wenn sie innerhalb <strong>de</strong>r laufen<strong>de</strong>n EA-Routine explizit<br />

abgefragt wird.<br />

Interrupt-Service-Routine:<br />

Anfor<strong>de</strong>rung höherer Priorität wird automatisch berücksichtigt.<br />

<br />

<br />

Die IR-Service-Routinen schachteln sich ineinan<strong>de</strong>r.<br />

Der Unterbrechungszeitpunkt ist nicht bekannt.<br />

Der komplette Sta<strong>tu</strong>s <strong>de</strong>r laufen<strong>de</strong>n Routine muss sofort nach <strong>de</strong>m Eintritt in die<br />

IRC höherer Priorität gerettet und vor <strong>de</strong>m Verlassen wie<strong>de</strong>r hergestellt wer<strong>de</strong>n.<br />

• PC und SR wer<strong>de</strong>n automatisch gerettet, alle weiteren Register müssen explizit<br />

(vorzugsweise auf <strong>de</strong>m Supervisor-Stack) gerettet wer<strong>de</strong>n (z. B. durch MOVMR).<br />

R. Hoffmann, TU Darmstadt, FG Rechnerarchitek<strong>tu</strong>r Systementwurf mit Mikroprozessoren WS 09/10

Codierte/Uncodierte Interruptanfor<strong>de</strong>rungen<br />

20<br />

Codierte Interruptanfor<strong>de</strong>rungen (wie beim Mo<strong>de</strong>llprozessor)<br />

<br />

Interrupt <strong>de</strong>r Priorität i sperrt automatisch Interrupts <strong>de</strong>r Priorität

7.2 Allgemeine Übertragungsmerkmale<br />

7.2.1 Punkt-zu-Punkt- und Mehrpunktverbindung<br />

21<br />

<br />

<br />

Punkt-zu-Punkt-Verbindung (direkte Verbindung zwischen zwei "Geräten")<br />

<br />

Je<strong>de</strong>s Gerät wird über einen gerätespezifischen Controller direkt an <strong>de</strong>n Systembus angeschlossen.<br />

(Zwischen Systembus/Mikroprozessor (Punkt A) und Gerät (Punkt B) existiert eine spezifische<br />

Verbindung/Schnittstelle)<br />

Mehrpunktverbindung<br />

<br />

Mehrere gleichartige Geräte wer<strong>de</strong>n durch einen Controller (Host-Adapter) bedient (z.B. SCSI-<br />

Bus).<br />

R. Hoffmann, TU Darmstadt, FG Rechnerarchitek<strong>tu</strong>r Systementwurf mit Mikroprozessoren WS 09/10

7.2.2 Schnittstellen<br />

7.2.3 Software- und hardwaregesteuerte<br />

Datenübertragung<br />

22<br />

Schnittstelle<br />

physikalische (elektrische) Eigenschaften <strong>de</strong>r Signallei<strong>tu</strong>ngen<br />

die benannten Signale auf <strong>de</strong>n Signallei<strong>tu</strong>ngen<br />

Be<strong>de</strong>u<strong>tu</strong>ng (Funktion) <strong>de</strong>r Signale<br />

Übertragungsprotokoll (zeitliche und logische Reihenfolge <strong>de</strong>r Signale)<br />

Kontrolle (Datentransport und Synchronisation)<br />

rein softwaregesteuert<br />

rein hardwaregesteuert<br />

hardwareunterstützt<br />

R. Hoffmann, TU Darmstadt, FG Rechnerarchitek<strong>tu</strong>r Systementwurf mit Mikroprozessoren WS 09/10

7.2.4 Serielle und parallele Datenübertragung<br />

7.2.5 Synchrone und asynchrone Datenübertragung<br />

23<br />

(Bit) Seriell:<br />

Die Bits eines Zeichens wer<strong>de</strong>n<br />

auf einer einzigen Datenlei<strong>tu</strong>ng<br />

nacheinan<strong>de</strong>r in einem festen<br />

Schrittakt übertragen.<br />

(Bit) Parallel:<br />

Alle Bits eines Zeichens/Da<strong>tu</strong>ms<br />

wer<strong>de</strong>n gleichzeitig übertragen.<br />

Synchron: Übertragung in einem<br />

festen Zeitraster<br />

<br />

gemeinsamer Takt für Sen<strong>de</strong>r und<br />

Empfänger o<strong>de</strong>r zwei<br />

Taktgeneratoren, Empfänger<br />

synchronisiert sich durch die im<br />

Datenstrom enthaltene<br />

Taktinformation<br />

Asynchron: Abstand zwischen zwei<br />

Zeichen ist beliebig lang.<br />

<br />

Zwei Taktgeneratoren, Empfänger<br />

synchronisiert sich erneut mit<br />

je<strong>de</strong>m Zeichentransport durch die<br />

im Datenstrom enthaltene<br />

Start/Stop-Information.<br />

R. Hoffmann, TU Darmstadt, FG Rechnerarchitek<strong>tu</strong>r Systementwurf mit Mikroprozessoren WS 09/10

7.2.6 Simplex-, Halbduplex- und Duplexbetrieb<br />

24<br />

<br />

<br />

<br />

Simplexbetrieb: in einer Rich<strong>tu</strong>ng, unidirektional<br />

Halbduplexbetrieb: abwechselnd in <strong>de</strong>r einen o<strong>de</strong>r an<strong>de</strong>ren Rich<strong>tu</strong>ng,<br />

bidirektional<br />

(Voll)Duplexbetrieb: gleichzeitig in bei<strong>de</strong>n Rich<strong>tu</strong>ngen<br />

R. Hoffmann, TU Darmstadt, FG Rechnerarchitek<strong>tu</strong>r Systementwurf mit Mikroprozessoren WS 09/10

7.2.7 Übertragungs-, Transfer- und Schrittgeschwindigkeit<br />

25<br />

Übertragungsgeschwindigkeit,<br />

Übertragungsrate,<br />

Übertragungsbandbreite<br />

Anzahl <strong>de</strong>r übertragbaren Bits/Sekun<strong>de</strong><br />

(bit/s, bps) bzw. Bytes/Sekun<strong>de</strong> (byte/s)<br />

Transfergeschwindigkeit<br />

Netto-Übertragungsrate (Übertragungsrate<br />

abzüglich zusätzlich übertragener Information)<br />

Schrittgeschwindigkeit<br />

auch Symbolrate<br />

Symbole/Sekun<strong>de</strong> (Baud) bei <strong>de</strong>r seriellen<br />

Übertragung.<br />

(pro Schritt können sich je nach Modulationsverfahren<br />

n Zustän<strong>de</strong> verän<strong>de</strong>rn)<br />

R. Hoffmann, TU Darmstadt, FG Rechnerarchitek<strong>tu</strong>r Systementwurf mit Mikroprozessoren WS 09/10

7.3 Parallele Schnittstellen<br />

26<br />

<br />

<br />

universelle (allgemein verwendbar), z. B. für Steuer- und Regelaufgaben<br />

spezielle für bestimmte Gerätetypen (z. B. Platten: SCSI, für Drucker<br />

Centronics)<br />

7.3.1 Universelle Parallel-Schnittstellen<br />

Systembusschnittstelle:<br />

Peripherieschnittstelle:<br />

Daten, Adressen, Kontrollei<strong>tu</strong>ngen<br />

EA-Tore (8, 16, 32 Bit breit), Kontrollei<strong>tu</strong>ngen<br />

periphere Datenformate:<br />

Zeichen (7, 8 Bit), BCD-Ziffern (4 Bit),<br />

Digitalwerte (z.B. 16 Bit AD/DA)<br />

R. Hoffmann, TU Darmstadt, FG Rechnerarchitek<strong>tu</strong>r Systementwurf mit Mikroprozessoren WS 09/10

Datenpufferung und Synchronisation<br />

27<br />

R. Hoffmann, TU Darmstadt, FG Rechnerarchitek<strong>tu</strong>r Systementwurf mit Mikroprozessoren WS 09/10

7.3.2 Parallel-<strong>Interface</strong>-<strong>Baustein</strong> PIA<br />

28<br />

(Parallel <strong>Interface</strong> Adaptor)<br />

PIA<br />

<br />

<br />

<br />

Peripherieschnittstelle<br />

zwei EA-Tore A und B<br />

PD7-PD0: Peripheral Data, 8 bidirektionale<br />

Datenlei<strong>tu</strong>ngen<br />

C1, C2: Handshake-Signale<br />

Aufgaben<br />

Zwischenspeicherung <strong>de</strong>r Daten<br />

Anpassung <strong>de</strong>r Datenformate<br />

Unterstützung <strong>de</strong>r Synchronisation<br />

und Interruptverwal<strong>tu</strong>ng<br />

R. Hoffmann, TU Darmstadt, FG Rechnerarchitek<strong>tu</strong>r Systementwurf mit Mikroprozessoren WS 09/10

PIA: Systembusschnittstelle<br />

29<br />

Kontrollsignale für synchronen<br />

Buszyklus<br />

Chip Select<br />

RegisterSelect i zur Auswahl <strong>de</strong>r Register<br />

Datenbusanschluss mit Tristate-Logik<br />

DMA-Request, Anfor<strong>de</strong>rung an DMAC<br />

Interrupt-Request<br />

IR-Daisy-Chain-Signale<br />

<strong>Baustein</strong>-Initialisierung<br />

Arbeitstakt<br />

R. Hoffmann, TU Darmstadt, FG Rechnerarchitek<strong>tu</strong>r Systementwurf mit Mikroprozessoren WS 09/10

PIA: Peripherieschnittstelle<br />

30<br />

Peripheral Data, Port A, 8<br />

bidirektionale Datenlei<strong>tu</strong>ngen<br />

Handshake-Signale Port A<br />

Peripheral Data, Port B, 8<br />

bidirektionale Datenlei<strong>tu</strong>ngen<br />

Handshake-Signale Port B<br />

R. Hoffmann, TU Darmstadt, FG Rechnerarchitek<strong>tu</strong>r Systementwurf mit Mikroprozessoren WS 09/10

PIA: interne Struk<strong>tu</strong>r<br />

31<br />

Control Register<br />

Sta<strong>tu</strong>sregister<br />

Data Direction Register,<br />

Datenrich<strong>tu</strong>ng je<strong>de</strong>s Bits<br />

programmierbar<br />

Datenregister<br />

R. Hoffmann, TU Darmstadt, FG Rechnerarchitek<strong>tu</strong>r Systementwurf mit Mikroprozessoren WS 09/10

PIA: Steuerregister (Control Register)<br />

Erklärungen s. nächste Folien<br />

32<br />

(durch CR0)<br />

(gesteuert durch CR3 und CR2)<br />

(gesteuert durch CR1 und CR0)<br />

R. Hoffmann, TU Darmstadt, FG Rechnerarchitek<strong>tu</strong>r Systementwurf mit Mikroprozessoren WS 09/10

PIA Steuerregister<br />

33<br />

IRQ#<br />

C1-IR<br />

SR7<br />

rise/fall C1<br />

A) if C1-DMA=0 (kein DMA-Betrieb)<br />

C1-TRANS fallen<strong>de</strong> o<strong>de</strong>r steigen<strong>de</strong> C1-Signalflanke setzt SR7<br />

C1-IR<br />

=1: und SR7 Auslösen eines Interrupts IRQ#=0<br />

fall / rise<br />

DMARQ#<br />

rise/fall C1<br />

B) if C1-DMA=1<br />

rise/fall C1 erzeugt DMA-Request, (SR7 wird nicht gesetzt,<br />

kein IRQ#)<br />

(rise/fall abhängig von C1-TRANS)<br />

R. Hoffmann, TU Darmstadt, FG Rechnerarchitek<strong>tu</strong>r Systementwurf mit Mikroprozessoren WS 09/10

PIA Steuerregister<br />

34<br />

IRQ#<br />

read<br />

C2-IR<br />

Interrupt-Eingang<br />

rise/fall C2<br />

SR6<br />

DRA<br />

rise/fall C2<br />

(gesteuert durch CR3 und CR2)<br />

(gesteuert durch CR1 und CR0)<br />

write<br />

Eingabe-Handshake<br />

DRB<br />

C2-MODE=0: C2 ist Interrupt-Eingang<br />

C2-TRANS<br />

fallen<strong>de</strong> o<strong>de</strong>r steigen<strong>de</strong> C2-Signalflanke setzt SR6<br />

C2-IR<br />

=1: und SR6 Auslösen eines Interrupts IRQ#=0<br />

rise/fall C2<br />

Ausgabe-Handshake<br />

C2-Mo<strong>de</strong> =1: C2 ist Handshake-Ausgang o<strong>de</strong>r Pegel<br />

C2-HS=0: automatischer Handshake<br />

Tor A: Eingabe-Handshake, C2A reagiert auf<br />

Lesezugriff DRA<br />

Tor B: Ausgabe-Handshake, C2B reagiert auf<br />

Schreibzugriff DRB<br />

C2-HS=1: programmierter Pegel für C2, wird <strong>de</strong>finiert durch C2-STATE<br />

R. Hoffmann, TU Darmstadt, FG Rechnerarchitek<strong>tu</strong>r Systementwurf mit Mikroprozessoren WS 09/10

Sta<strong>tu</strong>sregister<br />

35<br />

<br />

<br />

<br />

C1-Flanke SR7 if C1-IR Enabled then IRQ#<br />

(wenn C2-Mo<strong>de</strong> = C2 als Eingang programmiert):<br />

C2-Flanke SR6 if C2-IR Enabled then IRQ#<br />

SR7 und SR6 müssen durch das Programm zurückgesetzt wer<strong>de</strong>n<br />

(Befehl Schreiben von 11 nach SR7,SR6) löscht SR7, SR6<br />

R. Hoffmann, TU Darmstadt, FG Rechnerarchitek<strong>tu</strong>r Systementwurf mit Mikroprozessoren WS 09/10

Ausgabe-Handshake<br />

36<br />

1<br />

2<br />

2<br />

3<br />

1 2 3<br />

DAV<br />

DACK<br />

R. Hoffmann, TU Darmstadt, FG Rechnerarchitek<strong>tu</strong>r Systementwurf mit Mikroprozessoren WS 09/10

Ausgabe-Handshake<br />

37<br />

DAV<br />

DACK<br />

CPU<br />

write<br />

PIA<br />

Daten<br />

DRB<br />

DAV<br />

1 C2B=1 2<br />

Peripheriegerät<br />

start/stop<br />

5<br />

4<br />

IRQ#<br />

:=0<br />

SR7B=1<br />

SR7B=0<br />

C2B=0<br />

3<br />

DACK<br />

C1B=1<br />

C1B=0<br />

programmgesteuert<br />

R. Hoffmann, TU Darmstadt, FG Rechnerarchitek<strong>tu</strong>r Systementwurf mit Mikroprozessoren WS 09/10

Eingabe-Handshake<br />

CPU<br />

4<br />

read<br />

PIA<br />

DRA<br />

Peripheriegerät<br />

start/stop<br />

Daten<br />

38<br />

1<br />

C1A=1<br />

2<br />

IRQ#<br />

SR7A=1<br />

SR7A=0<br />

C2A=0<br />

C2A=1<br />

5<br />

C1A=0<br />

3<br />

:=0<br />

programmgesteuert<br />

DAV<br />

Daten in PIA<br />

DACK<br />

R. Hoffmann, TU Darmstadt, FG Rechnerarchitek<strong>tu</strong>r Systementwurf mit Mikroprozessoren WS 09/10

Datenausgabe über PIA Port B<br />

39<br />

1 0 0 1 0 0 0 0<br />

0 0 0 0 0 0 0 0<br />

Port A IR disabled<br />

Port B Handshake<br />

MOVE.B #0x00, CRA<br />

MOVE.B #0x90 CRB<br />

empfangsbereit<br />

DAV<br />

DACK<br />

R. Hoffmann, TU Darmstadt, FG Rechnerarchitek<strong>tu</strong>r Systementwurf mit Mikroprozessoren WS 09/10

Prozesssteuerung<br />

40<br />

R. Hoffmann, TU Darmstadt, FG Rechnerarchitek<strong>tu</strong>r Systementwurf mit Mikroprozessoren WS 09/10

7.4 Serielle Schnittstellen<br />

41<br />

<br />

<br />

Vorteil: Geringer Lei<strong>tu</strong>ngsaufwand<br />

Nachteile: u. U. Geringere Übertragungsbandbreite,<br />

Parallel/Serien/Parallelwandlung<br />

<br />

Periphere Übertragungswege<br />

<br />

Bei kurzen Entfernungen (bis zu wenigen Metern):<br />

<strong>Interface</strong>-<strong>Baustein</strong>e übernehmen die Anpassung an das periphere Protokoll<br />

(Bild 7-24a).<br />

<br />

Bei großen Entfernungen:<br />

Anpassung an das Netz-Übertragungsverfahren (analoges Fernsprechnetz,<br />

Nebenstellenanlage, ISDN), z. B. über Mo<strong>de</strong>ms. (Bild 7-24b)<br />

R. Hoffmann, TU Darmstadt, FG Rechnerarchitek<strong>tu</strong>r Systementwurf mit Mikroprozessoren WS 09/10

Serielle Datenübertragung<br />

42<br />

R. Hoffmann, TU Darmstadt, FG Rechnerarchitek<strong>tu</strong>r Systementwurf mit Mikroprozessoren WS 09/10

Datenfernübertragung, Allgemeines<br />

43<br />

<br />

DÜE = Datenübertragungseinrich<strong>tu</strong>ng (wie Mo<strong>de</strong>m)<br />

(DCE = data circuit-termination equipment)<br />

<br />

DEE = Datenen<strong>de</strong>inrich<strong>tu</strong>ng (Sen<strong>de</strong>r/Empfänger inkl. <strong>Interface</strong>)<br />

(DTE = data terminal equipment)<br />

<br />

V.-Schnittstellen für die analoge Übertragung<br />

<br />

X.-Schnittstellen für die digitale Übertragung<br />

<br />

V.24-Schnittstelle wird auch für die direkte Verbindung von zwei DEEs<br />

benutzt, z. B.<br />

<br />

<br />

Rechner – Maus<br />

Rechner – Peripherie<br />

R. Hoffmann, TU Darmstadt, FG Rechnerarchitek<strong>tu</strong>r Systementwurf mit Mikroprozessoren WS 09/10

Datenfernübertragung<br />

44<br />

DTR : Data Terminal<br />

Ready, DEE betriebsbereit<br />

DTR<br />

DSR<br />

DSR: Data Set Ready,<br />

Mo<strong>de</strong>m betriebsbereit<br />

DSR<br />

DTR<br />

RTS<br />

CTS<br />

RTS : Request to Send,<br />

Sen<strong>de</strong>auffor<strong>de</strong>rung an das<br />

Mo<strong>de</strong>m<br />

CTS: Clear to Send,<br />

Mo<strong>de</strong>m: Sen<strong>de</strong>r darf<br />

sen<strong>de</strong>n<br />

CTS<br />

TxD<br />

DEE<br />

Mo<strong>de</strong>m<br />

Mo<strong>de</strong>m<br />

DEE<br />

RTS<br />

RxD<br />

TxD: Transmitted Data,<br />

Sen<strong>de</strong>datenlei<strong>tu</strong>ng<br />

RxD: Received Data,<br />

Empfangsdatenlei<strong>tu</strong>ng<br />

Sen<strong>de</strong>r<br />

Empfänger<br />

entfällt bei direktem Anschluss<br />

R. Hoffmann, TU Darmstadt, FG Rechnerarchitek<strong>tu</strong>r Systementwurf mit Mikroprozessoren WS 09/10

7.4.1 V.24/V.28 (RS-232-C)<br />

45<br />

<br />

<br />

40 Schnittstellenlei<strong>tu</strong>ngen zwischen DEE und DÜE (Signale für Daten, Steuerung,<br />

Rückmeldungen, Takt, Wählinformation, analoger Information) (Bild 7-25)<br />

Schnittstelle wird wegen <strong>de</strong>r zugenommenen Digitaltechnik bei <strong>de</strong>r Datenübertragung<br />

weniger verwen<strong>de</strong>t, aber noch üblich bei <strong>de</strong>r direkten Verbindung zweier DEEs,<br />

insbeson<strong>de</strong>re zwischen Rechner und Terminal.<br />

<br />

<br />

<br />

<br />

<br />

<br />

<br />

TxD (Mo<strong>de</strong>m Übertragungsstrecke Mo<strong>de</strong>m RxD):<br />

Transmitted Data, Sen<strong>de</strong>datenlei<strong>tu</strong>ng<br />

RxD: Received Data, Empfangsdatenlei<strong>tu</strong>ng<br />

RTS : Request to Send, Sen<strong>de</strong>auffor<strong>de</strong>rung an das Mo<strong>de</strong>m<br />

CTS: Clear to Send, Mo<strong>de</strong>m: Sen<strong>de</strong>r darf sen<strong>de</strong>n<br />

DTR : Data Terminal Ready, DEE betriebsbereit<br />

DSR: Data Set Ready, Mo<strong>de</strong>m betriebsbereit<br />

DCD: Data Carrier Detect: Verbindung in Ordnung<br />

SGND: Signal Ground, Signal Er<strong>de</strong> (Bezugspotential)<br />

Logisch 0: -3 .. -15V, logisch 1: +3 .. +15V<br />

Übertragsraten: 110, 300, 1200, 2400, 9600, 19200 bit/s<br />

R. Hoffmann, TU Darmstadt, FG Rechnerarchitek<strong>tu</strong>r Systementwurf mit Mikroprozessoren WS 09/10

V.24<br />

46<br />

ITU = International Telecommunication Union<br />

CCITT = Comite Consultativ Intern. Telegraphique et Telephonique<br />

EIA = Electronic Industries Association<br />

DIN = Deutsches Insti<strong>tu</strong>t für Normung<br />

R. Hoffmann, TU Darmstadt, FG Rechnerarchitek<strong>tu</strong>r Systementwurf mit Mikroprozessoren WS 09/10

Direkter Anschluss, Sen<strong>de</strong>r Empfänger<br />

47<br />

Sen<strong>de</strong>r bereit:<br />

Data Terminal Ready<br />

Die Kontrollinformationen wer<strong>de</strong>n, falls alle<br />

vorhan<strong>de</strong>n, im Uhrzeigersinn<br />

von außen nach innen ausgetauscht<br />

Das Signal S.RTS kann zur zusätzlichen<br />

Software-Kontrolle verwen<strong>de</strong>t wer<strong>de</strong>n,<br />

falls es nicht für <strong>de</strong>n Rückkanal benötigt<br />

wird.<br />

DTR<br />

S. will sen<strong>de</strong>n<br />

Auffor<strong>de</strong>rung<br />

zum Empf.<br />

RTS<br />

Startbit (DAV)<br />

DSR<br />

CTS<br />

Sen<strong>de</strong>r<br />

TxD<br />

Data<br />

RxD<br />

Empfänger<br />

(fehlt: DACK)<br />

DTR<br />

Man spricht von Hardware-Flusskontrolle,<br />

wenn <strong>de</strong>r Rechner S.CTS auswertet und damit<br />

<strong>de</strong>n Sen<strong>de</strong>vorgang direkt unterbricht.<br />

DSR<br />

Empfänger<br />

bereit: Data<br />

Set Ready<br />

CTS<br />

RTS<br />

Empfangsbereit<br />

R. Hoffmann, TU Darmstadt, FG Rechnerarchitek<strong>tu</strong>r Systementwurf mit Mikroprozessoren WS 09/10

V-24, direkter Anschluss<br />

48<br />

ohne Geräte-Bereitschaftskontrolle (DTR/DSR)<br />

ohne Hardware-Flusskontrolle (RTS/CTS)<br />

R. Hoffmann, TU Darmstadt, FG Rechnerarchitek<strong>tu</strong>r Systementwurf mit Mikroprozessoren WS 09/10

Serielle Schnittstellen<br />

49<br />

R. Hoffmann, TU Darmstadt, FG Rechnerarchitek<strong>tu</strong>r Systementwurf mit Mikroprozessoren WS 09/10

7.5 Asynchron serielle Datenübertragung<br />

(Protokoll)<br />

50<br />

<br />

Die Bits eines Zeichens wer<strong>de</strong>n nacheinan<strong>de</strong>r übertragen.<br />

<br />

Fest vereinbarter Schrittakt zwischen Sen<strong>de</strong>r und Empfänger<br />

<br />

<br />

asynchron: je<strong>de</strong>s Zeichen wird neu synchronisiert, Start/Stop-Betrieb, geringer<br />

Hardware-Aufwand zur Synchronisation.<br />

synchron: Längerer Bitstrom wird übertragen und synchronisiert.<br />

<br />

<br />

<br />

RS-232C/V24<br />

Standard <strong>de</strong>r ITU (International Telecommunication Union) auf Vorschlag EAI<br />

(Electrical Industry Association)<br />

für langsame Peripheriegeräte (Maus, Drucker ohne Puffer, zeichenweise<br />

arbeiten<strong>de</strong> Bildschirmterminals, weiteres Mikroprozessorsystem mit schwacher<br />

Kopplung, Mo<strong>de</strong>m) : max. 19200 bit/s<br />

COM-Port (Communications Port) beim PC bis 115 kBit/s<br />

V28, V10, RS-485: höhere Übertragungsraten<br />

R. Hoffmann, TU Darmstadt, FG Rechnerarchitek<strong>tu</strong>r Systementwurf mit Mikroprozessoren WS 09/10

7.5.1 Asynchron serielle Datenübertragung<br />

51<br />

<br />

<br />

<br />

<br />

<br />

Ruhepegel 1: Trennung <strong>de</strong>r Zeichen (auch als Test, dass Lei<strong>tu</strong>ng OK)<br />

Startbit 0: Die negative Flanke dient zum Starten <strong>de</strong>r Synchronisation <strong>de</strong>s Empfängers<br />

Übertragung von 5..8 Datenbits, positive Logik, Beginn mit <strong>de</strong>m nie<strong>de</strong>rwertigsten Bit D0<br />

optionales Paritätsbit (Ergänzung zu gera<strong>de</strong>r/ungera<strong>de</strong>r Bitzahl: even/odd parity)<br />

wahlweise 1, 1.5 , 2 Stoppbits<br />

R. Hoffmann, TU Darmstadt, FG Rechnerarchitek<strong>tu</strong>r Systementwurf mit Mikroprozessoren WS 09/10

7.5.1 Bit- und Zeichensynchronisation<br />

52<br />

Startbit: Bezugspunkt für die<br />

Bitabtas<strong>tu</strong>ng (Taktsynchronisation)<br />

und <strong>de</strong>n Beginn <strong>de</strong>s Zeichens<br />

(Zeichensynchronisation)<br />

Stoppbit: Empfänger kann sich<br />

erholen, ohne Stoppbit wäre die<br />

negative Taktflanke nicht erkennbar.<br />

<br />

<br />

<br />

<br />

Empfänger muss die Datenimpulse in <strong>de</strong>r<br />

Mitte abfragen. Dazu wird ein Abtasttakt<br />

benötigt, <strong>de</strong>r aus einem Taktgenerator<br />

beim Empfänger gewonnen wird, <strong>de</strong>r mit<br />

einem Vielfachen <strong>de</strong>s Sen<strong>de</strong>taktes (z. B.<br />

64, asynchron dazu) läuft.<br />

Mit <strong>de</strong>m Erkennen <strong>de</strong>r Startimpulses<br />

durch die negative Startflanke wird ein<br />

Zähler mit <strong>de</strong>m Empfängertakt gestartet,<br />

<strong>de</strong>r zunächst bis zur Mitte <strong>de</strong>s ersten<br />

Datenimpulses zählt (z. B. 64+32 Takte)<br />

und dann das erste Datenbit abfragt.<br />

Der Zähler zählt jeweils um eine<br />

Impulsbreite weiter (z. B. 64 Takte), um<br />

die folgen<strong>de</strong>n Bits abzufragen.<br />

Die abgetasteten Datenbits wer<strong>de</strong>n in ein<br />

Schieberegister geschoben, das<br />

anschließend in das Empfangsregister<br />

parallel übertragen wird.<br />

R. Hoffmann, TU Darmstadt, FG Rechnerarchitek<strong>tu</strong>r Systementwurf mit Mikroprozessoren WS 09/10

Takt, Fehlererkennung<br />

53<br />

<br />

<br />

<br />

Taktgeneratoren für die Baud-<strong>Ra</strong>te<br />

entwe<strong>de</strong>r nur einer auf <strong>de</strong>r Sen<strong>de</strong>rseite, Empfänger erhält Taktsignal über<br />

separate Lei<strong>tu</strong>ng<br />

o<strong>de</strong>r zwei voneinan<strong>de</strong>r unabhängige Taktgeneratoren, <strong>de</strong>r Empfänger<br />

synchronisiert sich erneut mit je<strong>de</strong>m Zeichen.<br />

Erkennung von Übertragungsfehlern<br />

mehrfaches Abtasten <strong>de</strong>r Impulses innerhalb <strong>de</strong>r Pulsdauer (zur Erkennung von<br />

Störimpulsen, falsch eingestellte Empfänger-Baudrate)<br />

Abfragen <strong>de</strong>s Stoppbits (korrekter Abschluss <strong>de</strong>s Zeichens, evtl.<br />

Nichtübereinstimmung <strong>de</strong>r eingestellten Anzahl von Daten- und Paritybits, falsche<br />

Empfänger-Baudrate) Framing-Error<br />

Auswer<strong>tu</strong>ng <strong>de</strong>s Paritätsbits Parity-Error<br />

<br />

Overrun-Error<br />

• die Empfangsdaten im Empfangsdatenregister wur<strong>de</strong>n nicht rechtzeitig abgeholt und wur<strong>de</strong>n inzwischen<br />

schon von neueren Daten überschrieben, Software-Behandlung<br />

Unterbrechung <strong>de</strong>r Übertragung<br />

Empfänger/Mo<strong>de</strong>m setzt das Mel<strong>de</strong>signal CTS# auf inaktiv<br />

R. Hoffmann, TU Darmstadt, FG Rechnerarchitek<strong>tu</strong>r Systementwurf mit Mikroprozessoren WS 09/10

7.5.2 Erhöhung <strong>de</strong>r Übertragungssicherheit<br />

54<br />

<br />

Gerätebereitschaft<br />

DTR (zum Empfänger/Mo<strong>de</strong>m)<br />

DSR, DCD<br />

(vom Empfänger/Mo<strong>de</strong>m)<br />

<br />

Synchronisation<br />

<br />

<br />

implizit im Datenstrom<br />

• Startbit = DAV<br />

• kein DACK, Empfänger soll die Daten spätestens mit <strong>de</strong>n Stoppbits übernehmen.<br />

– wenn <strong>de</strong>r Empfänger die Daten nicht rechtzeitig übernimmt, kommt es zum Overrun-Fehler<br />

Unterbrechbarkeit, sogen. Hardware-Flusskontrolle<br />

• Sen<strong>de</strong>r wertet S.CTS aus und sen<strong>de</strong>t nur wenn S.CTS aktiv ist. Empfänger kann <strong>de</strong>n Sen<strong>de</strong>r<br />

unterbrechen (E.RTS inaktiv S.CTS inaktiv)<br />

zusätzliche explizite Synchronisation (nur bei Simplexverbindung S E )<br />

• S.RTS wird vom Sen<strong>de</strong>r durch Software gesetzt, E.CTS wird vom Empfänger durch Software<br />

ausgewertet.<br />

[S.RTS (Sen<strong>de</strong>wunsch) (Auswer<strong>tu</strong>ng durch Empfänger auf E.CTS-Lei<strong>tu</strong>ng)]<br />

S.CTS (Empfänger antwortet [wie<strong>de</strong>r] empfangsbereit auf E.RTS-Lei<strong>tu</strong>ng)<br />

// zusätzlich<br />

R. Hoffmann, TU Darmstadt, FG Rechnerarchitek<strong>tu</strong>r Systementwurf mit Mikroprozessoren WS 09/10

7.5.3 Asynchron serieller <strong>Interface</strong>-<strong>Baustein</strong><br />

55<br />

ACIA = Asynchronous Communication <strong>Interface</strong> Adapter<br />

UART = Universal Asynchronous Receiver Transmitter<br />

Aufgaben<br />

<br />

<br />

<br />

<br />

<br />

Parallel/Serien- und<br />

Serien/Parallelwandlung<br />

Einstellung verschie<strong>de</strong>ner Datenformate<br />

Paritätserzeugung und -überprüfung<br />

Takt- und Zeichensynchronisation<br />

Übertragungssteuerung im<br />

Vollduplexbetrieb<br />

R. Hoffmann, TU Darmstadt, FG Rechnerarchitek<strong>tu</strong>r Systementwurf mit Mikroprozessoren WS 09/10

ACIA: Periperieschnittstelle<br />

56<br />

<br />

<br />

CTS: Clear to Send<br />

(Sen<strong>de</strong>n: Gerät mel<strong>de</strong>t empfangsbereit)<br />

TxD: Transmit Data<br />

(Sen<strong>de</strong>datenlei<strong>tu</strong>ng)<br />

RTS: Request to Send<br />

(Empfang: CPU mel<strong>de</strong>t empfangsbereit -<br />

- über CR setzbar)<br />

RxD: Receive Data<br />

(Empfangsdatenlei<strong>tu</strong>ng)<br />

<br />

DCD: Data Carrier Detect<br />

(aktiv: Verbindung in Ordnung<br />

inaktiv: ankommen<strong>de</strong> Zeichen wer<strong>de</strong>n<br />

nicht in das Schieberegister<br />

übernommen)<br />

R. Hoffmann, TU Darmstadt, FG Rechnerarchitek<strong>tu</strong>r Systementwurf mit Mikroprozessoren WS 09/10

ACIA: Systembusschnittstelle<br />

57<br />

CSTART Kontrollsignale synchr.<br />

Buszyklus<br />

RW<br />

READY<br />

CS<br />

RSi<br />

Chip Select<br />

Register Select zur Auswahl<br />

<strong>de</strong>r Register<br />

D7-D0 Datenbusanschluss, Tristate<br />

IRQ Interrupt-Request<br />

IACKIN Daisy-Chain-Signale<br />

IACKOUT<br />

RESET<br />

CLK<br />

<strong>Baustein</strong>-Initialisierung<br />

Arbeitstakt<br />

R. Hoffmann, TU Darmstadt, FG Rechnerarchitek<strong>tu</strong>r Systementwurf mit Mikroprozessoren WS 09/10

ACIA: Komponenten<br />

58<br />

Sen<strong>de</strong>teil<br />

<br />

<br />

<br />

<br />

Empfangsteil<br />

TDR: Transmit Data Register<br />

(Sen<strong>de</strong>datenregister), 8 Bit<br />

TSR: Transmit Shift Register<br />

(Sen<strong>de</strong>schieberegister), 8 Bit<br />

Taktgenerator mit Sen<strong>de</strong>takteingang TCLK<br />

Paritätsgenerator<br />

<br />

<br />

<br />

<br />

<br />

RSR: Receive Shift Register<br />

(Empfangsschieberegister)<br />

RDR: Receive Data Register<br />

(Empfangsdatenregister)<br />

Taktgenerator mit Empfangstakteingang RCLK<br />

Empfangssynchronisationseinheit<br />

Paritätsprüfung<br />

R. Hoffmann, TU Darmstadt, FG Rechnerarchitek<strong>tu</strong>r Systementwurf mit Mikroprozessoren WS 09/10

ACIA, Funktionsweise<br />

59<br />

Steuerwerk<br />

<br />

<br />

<br />

<br />

MR: Modusregister<br />

(Datenformateinstellung)<br />

CR: Control Register<br />

(Steuerregister)<br />

SR: Sta<strong>tu</strong>sregister<br />

Übertragungssteuerwerk<br />

Unterbrechungslogik<br />

<br />

<br />

VNR:<br />

Vektornummerregister<br />

Priorisierungslogik für<br />

Daisy-Chain<br />

R. Hoffmann, TU Darmstadt, FG Rechnerarchitek<strong>tu</strong>r Systementwurf mit Mikroprozessoren WS 09/10

Modusregister MR<br />

60<br />

l<br />

R. Hoffmann, TU Darmstadt, FG Rechnerarchitek<strong>tu</strong>r Systementwurf mit Mikroprozessoren WS 09/10

Betriebsarten<br />

61<br />

A<br />

B<br />

MOD1-0<br />

= 00: Vollduplexbetrieb<br />

= 01: Echobetrieb, von A empfangenes Zeichen<br />

wird zum Sen<strong>de</strong>r B zurück gesen<strong>de</strong>t<br />

=10: Local Loop: TxD RxD, gesen<strong>de</strong>tes<br />

Zeichen wird lokal empfangen (zum Testen<br />

<strong>de</strong>s Sen<strong>de</strong>rs A)<br />

=01: Remote Loop: RxD TxD, empfangenes<br />

Zeichen wird ohne Speicherung in A-RDR<br />

zurück zum Sen<strong>de</strong>r B geschickt (Test <strong>de</strong>s<br />

Übertragungsweges, ausgehend von <strong>de</strong>r<br />

Peripherie B)<br />

R. Hoffmann, TU Darmstadt, FG Rechnerarchitek<strong>tu</strong>r Systementwurf mit Mikroprozessoren WS 09/10

RESET<br />

62<br />

RESET<br />

Steuerregister CR<br />

<br />

<br />

<br />

<br />

<br />

<br />

TIRE: Transmitter Interrupt Enable<br />

if TIRE and TDRE (Sen<strong>de</strong>register leer) then Interrupt<br />

RIRE: Receiver Interrupt Enable<br />

if RIRE and RDRF (Empfangsregister voll) then Interrupt<br />

(if RIRE and (no Data Carrier or Overrun) then also Interrupt)<br />

BRK: Break, es wird konstant <strong>de</strong>r Nullpegel gesen<strong>de</strong>t. Dadurch wird die Verbindung unterbrochen. Der Empfänger erkennt<br />

diesen Zustand als Framing-Error und durch Empfang von x00<br />

ERRR: Error Reset, Löschen <strong>de</strong>r Fehlerbits im Sta<strong>tu</strong>sregister<br />

(RESET: Initialisieren von Sen<strong>de</strong>rteil, Empfängerteil, Sta<strong>tu</strong>sregister)<br />

BRK, ERRR, RESET wer<strong>de</strong>n durch Beschreiben mit 1 ausgelöst (Diese Bits wer<strong>de</strong>n nicht gespeichert).<br />

R. Hoffmann, TU Darmstadt, FG Rechnerarchitek<strong>tu</strong>r Systementwurf mit Mikroprozessoren WS 09/10

63<br />

Sta<strong>tu</strong>sregister<br />

<br />

<br />

TDRE: Transmit Data Register Empty<br />

Wenn das Sen<strong>de</strong>register leer ist, kann <strong>de</strong>r Prozessor das<br />

nächste Zeichen in das TDR la<strong>de</strong>n.<br />

TDR wird nur gesen<strong>de</strong>t und automatisch TDRE gesetzt,<br />

wenn auch die Peripherie empfangsbereit ist (CTS# aktiv).<br />

wird durch das Nachla<strong>de</strong>n von TDR automatisch<br />

zurückgesetzt.<br />

wird durch RESET gesetzt (Sen<strong>de</strong>register an Anfang leer)<br />

RDRF: Receive Data Register Full<br />

Wenn das Empfangsregister voll ist, soll <strong>de</strong>r Prozessor es<br />

lesen.<br />

RDRF wird durch das Lesen von RDR automatisch<br />

zurückgesetzt.<br />

wird durch RESET zurückgesetzt. (Empfangsregister leer)<br />

FE: Framing Error, fehlerhafte Starto<strong>de</strong>r<br />

Stoppbits<br />

OVRN: Overrun Error, ein neues<br />

Zeichen steht im Schieberegister und<br />

wird in das Empfangsdatenregister<br />

übernommen, obwohl das vorherige<br />

Zeichen vom Prozessor nicht<br />

rechtzeitig abgeholt wur<strong>de</strong>.<br />

PE: Parity Error<br />

ERR: ein o<strong>de</strong>r mehrere Fehler<br />

R. Hoffmann, TU Darmstadt, FG Rechnerarchitek<strong>tu</strong>r Systementwurf mit Mikroprozessoren WS 09/10

Ausgabe-Synchronisation<br />

(Prozessor schreibt Da<strong>tu</strong>m)<br />

Da<strong>tu</strong>m TDR<br />

(Übernahme ins Schieberegister)<br />

if TSR leer then TDR TSR (automatisch) else wait<br />

(Rückmeldung)<br />

if (TDRTSR) set TDRE im Sta<strong>tu</strong>sregister optional Interrupt-Request<br />

(Sen<strong>de</strong>vorgang)<br />

Das Zeichen wird durch Schieben von TSR bitweise ausgegeben.<br />

64<br />

Zeichen<br />

Adresse<br />

TDR<br />

3<br />

TSR<br />

if leer<br />

write<br />

1<br />

5<br />

TxD<br />

IRQ#<br />

4<br />

reset<br />

TDRE<br />

TIRE<br />

set<br />

Sen<strong>de</strong>register leer<br />

CTS<br />

2<br />

CTS ( RTS)<br />

empfangsbereit,<br />

Sen<strong>de</strong>vorgang<br />

kann<br />

unterbrochen<br />

wer<strong>de</strong>n<br />

Software<br />

(0. IR enable)<br />

RTS<br />

R. Hoffmann, TU Darmstadt, FG Rechnerarchitek<strong>tu</strong>r Systementwurf mit Mikroprozessoren WS 09/10<br />

zur zusätzlichen Software-<br />

Kontrolle verwendbar,<br />

falls RTE nicht für <strong>de</strong>n<br />

Rückkanal benötigt wird.

Eingabe-Synchronisation<br />

65<br />

(Empfangen seriell)<br />

(Übernehmen parallel)<br />

(Meldung)<br />

(Error)<br />

for i:= 0 .. n do ( RxD RSR, shift RSR ), taktweise<br />

RSR RDR (ohne Paritätsbit, automatisch)<br />

RDR full set RDRF im Sta<strong>tu</strong>sregister optional Interrupt-Request<br />

if Fehler set OVRN, PE, FE, ERR im Sta<strong>tu</strong>sregister<br />

Adresse<br />

RDR<br />

voll<br />

RSR<br />

Zeichen<br />

5<br />

read<br />

3<br />

2. RxD<br />

TxD<br />

IRQ#<br />

4<br />

reset<br />

RDRF<br />

set<br />

1. RTS<br />

ACIA<br />

empfangsbereit<br />

CTS<br />

Empfangsregister voll<br />

Software<br />

(0. IR enable) RIRE<br />

RTS<br />

CTS<br />

R. Hoffmann, TU Darmstadt, FG Rechnerarchitek<strong>tu</strong>r Systementwurf mit Mikroprozessoren WS 09/10<br />

optionale<br />

zusätzliche Software-<br />

Kontrolle

Beispiel 7.4. Datenein-/ausgabe über asynchron seriellen<br />

<strong>Interface</strong>-<strong>Baustein</strong><br />

66<br />

Ein alphanumerisches Terminal wird<br />

angeschlossen. Die von <strong>de</strong>r Tasta<strong>tu</strong>r<br />

gesen<strong>de</strong>ten Zeichen wer<strong>de</strong>n vom Prozessor<br />

empfangen und als Echo zur Anzeige<br />

zurückgesen<strong>de</strong>t. Durch RTS wird die Tasta<strong>tu</strong>r<br />

freigegeben o<strong>de</strong>r gesperrt .<br />

Eine Textzeile soll in <strong>de</strong>n Pufferbereich<br />

LINE eingelesen und als Echo<br />

ausgegeben wer<strong>de</strong>n.<br />

Bild 7-33. Anschluss eines<br />

Bildschirmterminals an <strong>de</strong>n<br />

asynchron-seriellen <strong>Interface</strong>-<br />

<strong>Baustein</strong><br />

Die Dateneingabe ist durch ein<br />

Interruptprogramm zu synchronisieren.<br />

Bei <strong>de</strong>r Ausgabe wird durch Busy-Waiting<br />

gewartet, bis das Sen<strong>de</strong>register wie<strong>de</strong>r leer<br />

ist.<br />

Durch das Setzen von STATUS=OxFF wird<br />

<strong>de</strong>m Hauptprogramm das En<strong>de</strong> <strong>de</strong>r Zeile<br />

signalisiert.<br />

R. Hoffmann, TU Darmstadt, FG Rechnerarchitek<strong>tu</strong>r Systementwurf mit Mikroprozessoren WS 09/10

Interrupt:<br />

Empfangsreg.<br />

ist voll<br />

(RDRF=1)<br />

BUFPTR R5; // SavedPointer nach R5<br />

RDR m(R5) = x; // empf. Zeichen x speichern<br />

wait until Sen<strong>de</strong>register leer, TDRE<br />

x TDR; // Echo<br />

Programmablauf<br />

Sta<strong>tu</strong>sdiagramm<br />

// am Anfang ist das Sen<strong>de</strong>register leer<br />

67<br />

// Eingabe been<strong>de</strong>n<br />

(x = CarriageRe<strong>tu</strong>rn)<br />

o<strong>de</strong>r// 80 Zeichen<br />

(R5 = LINE+80)<br />

END: 0xD0 CR (RTS inaktiv)<br />

0xFF STATUS<br />

// normales Zeichen<br />

(x = Zeichen)<br />

und<br />

// noch nicht 80 Zeichen<br />

R5 < LINE+80<br />

R5++<br />

RET: R5 BUFPTR; // Save Pointer<br />

RTE<br />

R. Hoffmann, TU Darmstadt, FG Rechnerarchitek<strong>tu</strong>r Systementwurf mit Mikroprozessoren WS 09/10

Programmbeispiel<br />

68<br />

IR<br />

BUFPTR zeigt zu Beginn auf <strong>de</strong>n<br />

Anfang von LINE.<br />

BUFEND zeigt auf das En<strong>de</strong> von<br />

LINE.<br />

R5 ist Laufzeiger, zeigt auf das<br />

ak<strong>tu</strong>elle Element von LINE.<br />

INOUT ist die Anfangsadresse <strong>de</strong>r<br />

IR-Service-Routine. Sie wird in die<br />

Vektortabelle an die Position<br />

256=64*4 gela<strong>de</strong>n.<br />

VNR enthält die Vektornummer im<br />

<strong>Interface</strong>-<strong>Baustein</strong>, wird mit 64<br />

gela<strong>de</strong>n.<br />

MR x19 = 00 01 1 00 1<br />

duplex, 7 Bits, 1.5 Stopbits, keine<br />

Parität, 1:16<br />

CR xD8 = 1 1 01 1 0 0 0<br />

<br />

T+R on, Receiver IR enabled,<br />

RTS# aktiv (Tasta<strong>tu</strong>r Freigabe)<br />

WAIT: Warten auf das leere<br />

Sen<strong>de</strong>register.<br />

R. Hoffmann, TU Darmstadt, FG Rechnerarchitek<strong>tu</strong>r Systementwurf mit Mikroprozessoren WS 09/10

Programmbeispiel<br />

69<br />

Vektortabelle beginnt bei 0<br />

LINE belegt 80 Bytes<br />

STATUS als Flag für Zeilenen<strong>de</strong><br />

BUFPTR Laufzeiger zeigt am Anf. auf LINE<br />

BUFEND zeigt auf das En<strong>de</strong> von LINE<br />

0 STATUS<br />

IR-Vektor in die Vektortabelle la<strong>de</strong>n<br />

64 Vektornummer<br />

0x19 = 00 01 1 00 1 MR duplex, 7 Bits, 1.5 Stopbits,<br />

keine Parität, 1:16<br />

xD8 = 1 1 01 1 0 0 0 CR T+R on, Receiver IR enabled,<br />

RTS# aktiv (Tasta<strong>tu</strong>r Freigabe)<br />

Interrupt RDRF, Empfangsregister voll<br />

BUFPTR (Laufzeiger) R5<br />

RDR Line[R5]<br />

WAIT: Warteschleife auf SR7 (TDRE), Sen<strong>de</strong>register leer<br />

Echo sen<strong>de</strong>n<br />

if Carriage Re<strong>tu</strong>rn=hex 0D goto END<br />

if LINE not full goto RET<br />

END: (Eingabe been<strong>de</strong>n), 0xD0 CR (RTS inaktiv)<br />

0xFF STATUS<br />

RET: (R5 retten bis zum nächsten Interrupt)<br />

R. Hoffmann, TU Darmstadt, FG Rechnerarchitek<strong>tu</strong>r Systementwurf mit Mikroprozessoren WS 09/10

Hauptprogramm<br />

Interaktionen als<br />

modifiziertes Petrinetz dargestellt<br />

Init<br />

Terminal<br />

70<br />

Befehl<br />

UART<br />

INOUT<br />

RTS=1<br />

Tasta<strong>tu</strong>r<br />

freigegeben<br />

Zeichen<br />

Interrrupt-<br />

Programm<br />

RDR<br />

RSR<br />

RDRF=1<br />

Taste betätigt<br />

Speicherzelle x<br />

RDRF=0<br />

Echozeichen eingetroffen<br />

Echoz. nicht eingetr.<br />

TDRE=1<br />

Bildspeicher<br />

x ungleich CR<br />

x gleich CR<br />

TDRE=0<br />

TDR<br />

TSR<br />

Tasta<strong>tu</strong>r<br />

gesperrt<br />

END<br />

RET<br />

Befehl<br />

RTS=0<br />

R. Hoffmann, TU Darmstadt, FG Rechnerarchitek<strong>tu</strong>r Systementwurf mit Mikroprozessoren WS 09/10

7.6 Synchron serielle Datenübertragung<br />

71<br />

<br />

<br />

<br />

<br />

Es wer<strong>de</strong>n nicht einzelne Zeichen son<strong>de</strong>rn es wird ein Bitstrom übertragen.<br />

Taktsynchronisation ist für <strong>de</strong>n gesamten Übertragungsvorgang erfor<strong>de</strong>rlich,<br />

Gleichlauf von Sen<strong>de</strong>r und Empfänger<br />

Anwendungen: Rechnerkopplungen, Datenfernübertragung, schnelle EA<br />

Übertragungsraten ca. 10 kbit/s bis 10 Gbit/s.<br />

R. Hoffmann, TU Darmstadt, FG Rechnerarchitek<strong>tu</strong>r Systementwurf mit Mikroprozessoren WS 09/10

7.6.1 Bit- und Zeichensynchronisation<br />

72<br />

<br />

<br />

Durch ein Taktsignallei<strong>tu</strong>ng vom<br />

Sen<strong>de</strong>r zum Empfänger:<br />

zu hoher Aufwand, Takt wird auf<br />

<strong>de</strong>r Lei<strong>tu</strong>ng verzögert.<br />

Ein Taktgenerator beim<br />

Empfänger wird durch die<br />

Flanken im Bitstrom nachgestellt.<br />

<br />

<br />

bitorientiertes Protokoll<br />

<br />

<br />

Bitstrom besteht aus Bitfel<strong>de</strong>rn<br />

unterschiedlicher Länge<br />

Es muss sichergestellt wer<strong>de</strong>n, dass in<br />

bestimmten Abstän<strong>de</strong>n Signalwechsel<br />

auftreten<br />

zeichenorientiertes Protokoll<br />

<br />

Bitstrom besteht aus Zeichen<br />

bestimmter Bitanzahl<br />

<br />

Synchronisationszeichen (z.B. ASCII<br />

SYN, hex 0000 1000) wer<strong>de</strong>n in <strong>de</strong>n<br />

Datenstrom eingefügt. Diese dienen<br />

auch <strong>de</strong>r Zeichensynchronisation<br />

(Datenübernahme beginnt z.B. nach <strong>de</strong>r<br />

Erkennung von zwei SYN Zeichen)<br />

R. Hoffmann, TU Darmstadt, FG Rechnerarchitek<strong>tu</strong>r Systementwurf mit Mikroprozessoren WS 09/10

7.6.2 BISYNC, HDLC, SDLC-Protokoll<br />

73<br />

Protokoll:<br />

Regeln für <strong>de</strong>n ein<strong>de</strong>utigen Ablauf <strong>de</strong>r<br />

Datenübertragung<br />

<br />

<br />

<br />

<br />

synchron/asynchron<br />

Übertragungsgeschwindigkeit<br />

zeichenorientiert/bitorientiert<br />

Datenformat, Zeichenco<strong>de</strong>, Datensicherung<br />

<br />

<br />

<br />

Einlei<strong>tu</strong>ng <strong>de</strong>r DÜ<br />

Datenübertragung (mit Zählen <strong>de</strong>r Blöcke,<br />

Reklamation fehlerhaft übertragener Blöcke,<br />

Fehlerkorrek<strong>tu</strong>r durch Blockwie<strong>de</strong>rholung)<br />

Beendigung <strong>de</strong>r DÜ<br />

R. Hoffmann, TU Darmstadt, FG Rechnerarchitek<strong>tu</strong>r Systementwurf mit Mikroprozessoren WS 09/10

OSI-Referenzmo<strong>de</strong>ll<br />

(open system interconnection)<br />

74<br />

Norm zur Kommunikation in Rechnernetzen, 7 Abstraktionsebenen<br />

Layer 3: (network layer),<br />

Vermittlungsschicht<br />

Herstellung transparenter End-zu-End-<br />

Verbindungen, Wegewahl (Routing)<br />

Paketvermittlung Datex-P, X.25, IP<br />

Layer 2: (data link layer), Sicherungsschicht<br />

Formate, Betriebsarten (halbduplex, duplex)<br />

Auf- und Abbau <strong>de</strong>r Verbindung<br />

Übertragung von Datenblöcken<br />

Fehlererkennung- und -beseitigung<br />

BISYNC, HDLC, SDLC, CSMA-Ethernet<br />

Layer 1: (physical layer), Bitübertragungsschicht<br />

Physikalisches Überragungsverfahren (V24, X.21, Ethernet)<br />

Art <strong>de</strong>r Übertragung von Bitfolgen, Synchronisation, Übertragungsrate<br />

R. Hoffmann, TU Darmstadt, FG Rechnerarchitek<strong>tu</strong>r Systementwurf mit Mikroprozessoren WS 09/10

TCP / IP<br />

Transmission Control Protocol / Internet Protocol<br />

75<br />

Transmission Control Protocol (TCP)<br />

TCP liegt in <strong>de</strong>n Schichten oberhalb von IP, <strong>de</strong>r Transportschicht. TCP setzt ausschließlich auf IP auf. Das TCP arbeitet im Gegensatz<br />

zum IP verbindungsorientiert, was heisst, dass vor <strong>de</strong>m Übertragen von Datenpaketen eine bidirektionale vir<strong>tu</strong>elle Verbindung auf und<br />

später wie<strong>de</strong>r abgebaut wird. Während in <strong>de</strong>n Schichten unterhalb vom TCP kaum Überlegungen hinsichtlich möglicher Verluste<br />

ganzer Datenpakete angestellt wer<strong>de</strong>n, wird dies hier berücksichtigt. Das TCP überträgt aus Sicht <strong>de</strong>s Dienstnutzers einen<br />

kontinuierlichen, aus Bytes bestehen<strong>de</strong>n Datenstrom in beliebige Rich<strong>tu</strong>ngen. Dabei legt es die Blockgrößen und das Weiterleiten von<br />

Daten selbst fest. Die Daten wer<strong>de</strong>n gesichert durch:<br />

Sequenznummern, Prüfsummenbildung mit Empfangsquit<strong>tu</strong>ngen, Quit<strong>tu</strong>ng mit Zeitüberwachung, Segmentwie<strong>de</strong>rholung nach<br />

Quit<strong>tu</strong>ngszeitablauf<br />

Internet Protokoll (IP)<br />

IP ist ein verbindungsloses, ungesichertes Protokoll <strong>de</strong>r<br />

Vermittlungsschicht.<br />

Hauptaufgaben von IP sind die Adressierung von Rechnern und<br />

das Fragmentieren bzw. Defragmentieren von Datenpaketen.<br />

IP versucht, Pakete so gut wie möglich <strong>de</strong>m nächsten Rechner<br />

im Netzwerk zu übermitteln.<br />

Ist dieser nicht <strong>de</strong>r Zielrechner <strong>de</strong>s Pakets, schickt die dortige<br />

IP-Implementierung das Paket weiter, dient also <strong>de</strong>r Vermittlung.<br />

Das Paket durchläuft auf seinem Weg meist mehrere<br />

Vermittlungen bis es <strong>de</strong>n Zielrechner erreicht. Je<strong>de</strong>r Rechner im<br />

Netz muss <strong>de</strong>shalb IP verstehen. Wegweiser in IP-Netzen, die an<br />

Kreuzungen von Netzen die Daten richtig weiterleiten, wer<strong>de</strong>n<br />

Router genannt.<br />

R. Hoffmann, TU Darmstadt, FG Rechnerarchitek<strong>tu</strong>r Systementwurf mit Mikroprozessoren WS 09/10

BISYNC-Protokoll (binary synchronous communication,<br />

IBM 1970)<br />

zeichenorientiert<br />

76<br />

SYN: (synchronous idle)<br />

SOH: (start of heading)<br />

CONTROL<br />

STX: (start of text)<br />

TEXT: Datenblock<br />

ETX: (end of text)<br />

BCC: (block check character)<br />

2 Synchronisationszeichen<br />

Beginn <strong>de</strong>s optionalen Kontrollblocks<br />

zur Übertragungssteuerung (Quell- und Zieladresse,<br />

Datenblock/Steuerblock)<br />

alternativ Steuerinformation<br />

En<strong>de</strong> <strong>de</strong>r Nachricht, alternativ ETB (end of block)<br />

heute kaum noch verwen<strong>de</strong>t, zur Erklärung <strong>de</strong>s Prinzips<br />

R. Hoffmann, TU Darmstadt, FG Rechnerarchitek<strong>tu</strong>r Systementwurf mit Mikroprozessoren WS 09/10

BISYNC-Beispiel: Einlei<strong>tu</strong>ng, Durchführung, Beendigung<br />

77<br />

<br />

Sen<strong>de</strong>r und<br />

Empfänger<br />

tauschen ihre<br />

Datenblöcke im<br />

Handshake-<br />

Verfahren aus.<br />

<br />

Halbduplex-Betrieb,<br />

SYN-Zeichen in <strong>de</strong>r<br />

Darstellung (Bild 7-<br />

38) weggelassen.<br />

R. Hoffmann, TU Darmstadt, FG Rechnerarchitek<strong>tu</strong>r Systementwurf mit Mikroprozessoren WS 09/10

Merkmale zeichenorientierter Protokolle<br />

78<br />

<br />

Nicht transparent<br />

<br />

<br />

Bestimmte Zeichenco<strong>de</strong>s<br />

wer<strong>de</strong>n als Steuerzeichen<br />

interpretiert und können daher<br />

nicht als Daten benutzt<br />

wer<strong>de</strong>n.<br />

Die Hardware muss die<br />

verschie<strong>de</strong>nen Steuerzeichen<br />

und Formate für die Daten-,<br />

Steuer- und<br />

Quit<strong>tu</strong>ngsinformation<br />

interpretieren hoher<br />

Aufwand.<br />

<br />

Realisierung <strong>de</strong>r transparenten<br />

Datenübertragung beim BISYNC-<br />

Protokoll durch Einfügen von DLE<br />

<br />

<br />

<br />

STX (DLE, STX) STX<br />

ETX (DLE, ETX) ETX<br />

DLE im Datenblock (DLE, DLE)<br />

"character s<strong>tu</strong>ffing"<br />

R. Hoffmann, TU Darmstadt, FG Rechnerarchitek<strong>tu</strong>r Systementwurf mit Mikroprozessoren WS 09/10

Merkmale bitorientierter Protokolle<br />

79<br />

<br />

Einheitliches Format, bei <strong>de</strong>m die<br />

Fel<strong>de</strong>r durch Bitpositionen<br />

festgelegt wer<strong>de</strong>n.<br />

<br />

Beliebige Bitmuster können<br />

(transparent) übertragen wer<strong>de</strong>n.<br />

<br />

Zeichenco<strong>de</strong>s<br />

<br />

Keine verschie<strong>de</strong>nen Formate für<br />

die Daten, Steuerinformation und<br />

Quit<strong>tu</strong>ngsinformation wie bei <strong>de</strong>n<br />

zeichenorientierten Protokollen<br />

<br />

<br />

<br />

<br />

gepackte BCD-Zahlen<br />

Ganzahlen<br />

Gleitkommmazahlen<br />

Maschinenco<strong>de</strong><br />

<br />

usw.<br />

R. Hoffmann, TU Darmstadt, FG Rechnerarchitek<strong>tu</strong>r Systementwurf mit Mikroprozessoren WS 09/10

itorientiert<br />

SDLC-Protokoll (synchronous data-link control)<br />

Synchronous Data Link Control (SDLC) (Synchrone Datenübertragungssteuerung) ist ein herstellerspezifisches bitsynchrones<br />

Datenkommunikationsprotokoll für die transparente bitserielle Datenübertragung. Es <strong>de</strong>ckt Schicht zwei <strong>de</strong>r von IBM entwickelten SNA<br />

(Systems Network Architec<strong>tu</strong>re 1974) ab. Der Datenaustausch kann über fest geschaltete Lei<strong>tu</strong>ngen o<strong>de</strong>r über vermittelte<br />

Lei<strong>tu</strong>ngen in <strong>de</strong>n Betriebsarten halbduplex und duplex erfolgen. Der Übertragungsweg kann als Punkt-zu-Punkt-Verbindung,<br />

Mehrpunktverbindung o<strong>de</strong>r als Schleife konfiguriert sein.-- SDLC ist die Grundlage für das erweiterte HDLC-Protokoll, welches einen<br />

erweiterten <strong>Ra</strong>hmen (Frame) besitzt. Ebenso wie bei HDLC wer<strong>de</strong>n auch bei SDLC so genannte Stopfbits zur Kanalkodierung<br />

verwen<strong>de</strong>t.<br />

http://<strong>de</strong>.wikipedia.org/wiki/Sdlc<br />

zur Einrahmung <strong>de</strong>s Datenblocks, zur<br />

Synchronisation und als Füllzeichen zwischen<br />

Übertragungsblöcken<br />

SNA: Hierachisch organisiertes Computernetzwerk<br />

80<br />

Empfängeradresse, auch zum<br />

Broadcasting.<br />

Übertragung von Steuerdaten/Nutzdaten, Anzahl <strong>de</strong>r<br />

gesen<strong>de</strong>ten bzw. fehlerfrei empfangenen Datenblöcke,<br />

verschie<strong>de</strong>ne Steuerkommandos.<br />

n Bytes Daten<br />

R. Hoffmann, TU Darmstadt, FG Rechnerarchitek<strong>tu</strong>r Systementwurf mit Mikroprozessoren WS 09/10<br />

(frame check sequence): 2<br />

Blockprüfzeichen

HDLC-Protokoll (high level data-link control)<br />

81<br />

High-Level Data Link Control ist ein von <strong>de</strong>r ISO normiertes Netzwerkprotokoll. Es ist innerhalb <strong>de</strong>s ISO/OSI-Mo<strong>de</strong>lls in Schicht<br />

2, <strong>de</strong>r Sicherungsschicht einzuglie<strong>de</strong>rn. HDLC basiert in seiner Grundstruk<strong>tu</strong>r auf <strong>de</strong>m SDLC-Protokoll. -- Der HDLC-Standard<br />

besteht aus:<br />

Steuerung <strong>de</strong>s Übertragungsabschnitts<br />

Erkennen von Übertragungsfehlern und Reihenfolgefehlern durch Blocküberprüfung (CRC-16) und Sequenznummernkontrolle<br />

Fehlerkorrek<strong>tu</strong>r durch Blockwie<strong>de</strong>rholung<br />

Flusskontrolle mit Fenstermechanismus<br />

Weitermel<strong>de</strong>n von nicht-korrigierbaren Fehlern und Protokollfehlern zur nächsthöheren Schicht (Vermittlungsschicht, Network<br />

Layer)<br />

Das HDLC Datenformat ist typisch für ein bitorientiertes Protokoll ohne die Möglichkeit <strong>de</strong>r Authentifizierung. Es ermöglicht<br />

Punkt-zu-Punkt-Verbindungen und Punkt-zu-Multipunkt Verbindungen.<br />

http://<strong>de</strong>.wikipedia.org/wiki/HDLC<br />

<br />

Erweiterung <strong>de</strong>s SDLC-Protokolls, bitorientiert<br />

<br />

ADDRESS und CONTROL auf mehrere BYTES erweiterbar<br />

<br />

Datenfeld kann beliebige Anzahl von Bits umfassen<br />

HDLC zählt heute zu <strong>de</strong>n wichtigsten Protokollen und wird z.B. in lokalen Netzen, im<br />

INTERNET o<strong>de</strong>r in vielen industriellen Applikationen eingesetzt.<br />

(D-Kanal ISDN, IEEE 802.2 LAN, Schicht 2 X.25 (Datex-P))<br />

R. Hoffmann, TU Darmstadt, FG Rechnerarchitek<strong>tu</strong>r Systementwurf mit Mikroprozessoren WS 09/10

Bitmuster und Codierung<br />

82<br />

<br />

<br />

<br />

<br />

Nur drei spezielle Bitmuster müssen erkannt wer<strong>de</strong>n<br />

(a) 0 [1 * 6] 0 FLAG<br />

(b) 0 [1 * 7..14] ABORT, vorzeitige Beendigung <strong>de</strong>r Übertragung<br />

(c) [1* >= 15]IDLE, Ruhezustand<br />

Bit-S<strong>tu</strong>ffing im Übertragungsblock zwischen <strong>de</strong>n Flags, so dass a,b,c weiterhin erkannt<br />

wer<strong>de</strong>n können<br />

Sen<strong>de</strong>r: [1 * 5] [1 * 5] 0 (Einfügen einer Null nach 5 Einsen)<br />

Empfänger: [1 * 5] 0 [1 * 5] (Entfernen <strong>de</strong>r Null nach 5 Einsen)<br />

NRZI-Signalcodierung (non re<strong>tu</strong>rn to zero with interchange)<br />

1 gleichbleiben<strong>de</strong> Polarität, 0 Polarität wechselt.<br />

Durch das Null-Einfügen erfolgt spätestens nach je<strong>de</strong>m 5. Bit ein Signalwechsel<br />

leichte Synchronisation<br />

R. Hoffmann, TU Darmstadt, FG Rechnerarchitek<strong>tu</strong>r Systementwurf mit Mikroprozessoren WS 09/10

7.6.3 Synchron serieller <strong>Interface</strong>-<strong>Baustein</strong><br />

83<br />

<br />

<br />

<br />

<br />

<br />

unterstützt die Datenübertragung bitorientierter Protokolle<br />

Parallel-Serien/Serien-Parallel-Wandlung<br />

Erzeugen und Erkennen von FLAG, IDLE, ABORT<br />

Null-Einfügen und –Entfernen<br />

Erzeugen und Prüfen <strong>de</strong>r Blockprüfzeichen<br />

R. Hoffmann, TU Darmstadt, FG Rechnerarchitek<strong>tu</strong>r Systementwurf mit Mikroprozessoren WS 09/10

Synchron serieller <strong>Interface</strong>-<strong>Baustein</strong><br />

84<br />

Komponenten und Schnittstellen<br />

Sen<strong>de</strong>r- und Empfängerteil<br />

Allgemeines Steuerwerk<br />

Übertragungssteuerwerk zum<br />

Austausch von Steuersignalen mit <strong>de</strong>r<br />

Peripherie<br />

Unterbrechungs- und Verket<strong>tu</strong>ngslogik<br />

Schnittstellen zum Systembus und zur<br />

Peripherie wie beim asynchron seriellen<br />

<strong>Baustein</strong><br />

Zur Aufrechterhal<strong>tu</strong>ng eines lückenlosen<br />

Datenbitstrom besitzen Sen<strong>de</strong>r- und<br />

Empfängerteil je einen FIFO-<br />

Pufferspeicher (TDR1..3, RDR1..3)<br />

R. Hoffmann, TU Darmstadt, FG Rechnerarchitek<strong>tu</strong>r Systementwurf mit Mikroprozessoren WS 09/10

Synchron serieller <strong>Interface</strong>-<strong>Baustein</strong>: Funktionsweise<br />

Sen<strong>de</strong>n<br />

85<br />

<br />

<br />

<br />

<br />

<br />

Normieren durch RESET-Signal<br />

o<strong>de</strong>r RESET-Steuerbit<br />

Initialisieren durch La<strong>de</strong>n <strong>de</strong>s<br />

Steuerregisters<br />

Nach Rücksetzen <strong>de</strong>s RESET-Bits<br />

sen<strong>de</strong>n von IDLE (inactive idle)<br />

o<strong>de</strong>r von FLAG (active idle), je nach<br />

Steuerbit<br />

La<strong>de</strong>n eines Bytes in <strong>de</strong>n<br />

Sen<strong>de</strong>-FIFO Beginn <strong>de</strong>s<br />

Sen<strong>de</strong>vorgangs, (im Falle von IDLE<br />

muss zuerst ein FLAG als Da<strong>tu</strong>m<br />

gesen<strong>de</strong>t wer<strong>de</strong>n)<br />

Den Abschluss <strong>de</strong>s Datenblocks<br />

durch ein zusätzliches FLAG wird<br />

durch La<strong>de</strong>n <strong>de</strong>s letzen Bytes an<br />

eine zweite TDR-Adresse erreicht.<br />

(Es gibt eine TDR-Adresse mit <strong>de</strong>m<br />

Attribut frame continue und eine mit<br />

<strong>de</strong>m Attribut frame terminate.)<br />

R. Hoffmann, TU Darmstadt, FG Rechnerarchitek<strong>tu</strong>r Systementwurf mit Mikroprozessoren WS 09/10

Empfangen<br />

86<br />

<br />

<br />

<br />

<br />

<br />

Normieren und Initialisieren analog<br />

zum Sen<strong>de</strong>n<br />

Wechsel in <strong>de</strong>n Aktivzustand mit<br />

<strong>de</strong>n Rücksetzen <strong>de</strong>s RESET-Bits<br />

Testen <strong>de</strong>s empfangenen<br />

Bitstroms auf IDLE, FLAG und<br />

ABORT<br />

Die auf FLAG folgen<strong>de</strong>n Daten-<br />

Bytes (nicht FLAG, IDLE, ABORT)<br />

wer<strong>de</strong>n vom<br />

Empfangsschieberegister in <strong>de</strong>n<br />

Empfangs-FIFO übernommen und<br />

von dort vom Prozessor abgeholt.<br />

Die Erkennung <strong>de</strong>s abschließen<strong>de</strong>n<br />

FLAG-Bytes been<strong>de</strong>t die<br />

Datenübernahme in <strong>de</strong>n<br />

Empfangs-FIFO.<br />

R. Hoffmann, TU Darmstadt, FG Rechnerarchitek<strong>tu</strong>r Systementwurf mit Mikroprozessoren WS 09/10