- Page 1 and 2: System Generator for DSP Reference

- Page 3 and 4: Table of Contents Chapter 1: Xilinx

- Page 5 and 6: Block Parameters Dialog Box. . . .

- Page 7 and 8: DSP48E . . . . . . . . . . . . . .

- Page 9 and 10: Block Interface . . . . . . . . . .

- Page 11 and 12: Device Support . . . . . . . . . .

- Page 13 and 14: See Also . . . . . . . . . . . . .

- Page 15 and 16: Data Format . . . . . . . . . . . .

- Page 17 and 18: See Also . . . . . . . . . . . . .

- Page 19 and 20: Xilinx Blockset Chapter 1 Organizat

- Page 21 and 22: AXI4 Blocks Table 1-1: AXI4 Blocks

- Page 23 and 24: Table 1-2: Basic Element Blocks Blo

- Page 25 and 26: Table 1-3: Communication Blocks - F

- Page 27 and 28: Data Type Blocks Table 1-4: Control

- Page 29 and 30: Table 1-6: DSP Blocks DSP Block Des

- Page 31 and 32: Table 1-7: Floating-Point Blocks In

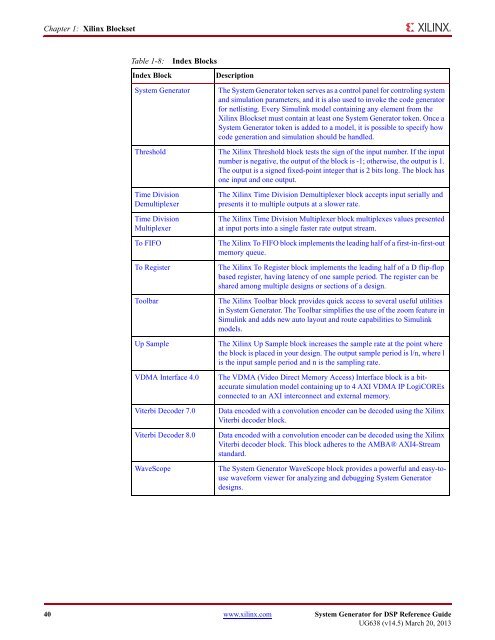

- Page 33 and 34: Table 1-8: Index Blocks Index Block

- Page 35 and 36: Table 1-8: Index Blocks Index Block

- Page 37 and 38: Table 1-8: Index Blocks Index Block

- Page 39: Table 1-8: Index Blocks Index Block

- Page 43 and 44: Memory Blocks Table 1-10: Memory Bl

- Page 45 and 46: Table 1-12: Tool Blocks Tool Blocks

- Page 47 and 48: Common Options in Block Parameter D

- Page 49 and 50: Sample Period Common Options in Blo

- Page 51 and 52: Block Reference Pages Block Referen

- Page 53 and 54: Device Support Floating-Point suppo

- Page 55 and 56: LogiCORE Documentation Device Suppo

- Page 57 and 58: Block Parameters Basic tab Addressa

- Page 59 and 60: Refer to the section Overflow and Q

- Page 61 and 62: Assert Other parameters used by thi

- Page 63 and 64: AXI FIFO Block Interface Block Para

- Page 65 and 66: LogiCORE Documentation Device Suppo

- Page 67 and 68: Slice Repeat output_var = {port_ide

- Page 69 and 70: Black Box Black Box This block is l

- Page 71 and 72: Black Box can usually be used witho

- Page 73 and 74: Block Parameters Basic tab Black Bo

- Page 75 and 76: An Example Black Box The following

- Page 77 and 78: ChipScope ChipScope This block is l

- Page 79 and 80: Known Issues More Information ChipS

- Page 81 and 82: Implementation tab CIC Compiler 2.0

- Page 83 and 84: CIC Compiler 3.0 Number of Stages:

- Page 85 and 86: Clock Enable Probe Clock Enable Pro

- Page 87 and 88: Clock Probe Clock Probe This block

- Page 89 and 90: Signed (2’s comp): The output is

- Page 91 and 92:

Complex Multiplier 3.1 Optional Por

- Page 93 and 94:

Page 2 tab Output Product Range Com

- Page 95 and 96:

Complex Multiplier 5.0 System Gener

- Page 97 and 98:

Concat Block Interface Block Parame

- Page 99 and 100:

Block Parameters The dialog box for

- Page 101 and 102:

Constant Floating-point Precision -

- Page 103 and 104:

Convert Block Parameters Convert Th

- Page 105 and 106:

Convolution Encoder 7.0 Convolution

- Page 107 and 108:

Convolution Encoder 8.0 Convolution

- Page 109 and 110:

CORDIC 4.0 CORDIC 4.0 This block is

- Page 111 and 112:

CORDIC 4.0 Precision: Configures t

- Page 113 and 114:

y_in to cartesian_tdata_imag phase

- Page 115 and 116:

CORDIC 5.0 Precision: Configures t

- Page 117 and 118:

Counter Counter This block is liste

- Page 119 and 120:

DDS Compiler 4.0 DDS Compiler 4.0 T

- Page 121 and 122:

DDS Compiler 4.0 phase_in: used wh

- Page 123 and 124:

DDS Compiler 4.0 rfd: When checked

- Page 125 and 126:

DDS Compiler 5.0 When set to stream

- Page 127 and 128:

Implementation tab DDS Compiler 5.0

- Page 129 and 130:

Phase Offset Angles tab DDS Compile

- Page 131 and 132:

Delay Block Parameters System Gener

- Page 133 and 134:

cascaded, albeit without using the

- Page 135 and 136:

System Generator for DSP Reference

- Page 137 and 138:

Depuncture Depuncture This block is

- Page 139 and 140:

Disregard Subsystem Disregard Subsy

- Page 141 and 142:

OR_all_TLASTS: Pass the logical OR

- Page 143 and 144:

Divider Generator 3.0 latency: Thi

- Page 145 and 146:

AXI Interface AXI behavior: NonBlo

- Page 147 and 148:

Down Sample Down Sample This block

- Page 149 and 150:

Block Parameters Basic tab Xilinx L

- Page 151 and 152:

DSP48 Provide BCOUT port: when sel

- Page 153 and 154:

DSP48 Macro Block Interface Block P

- Page 155 and 156:

DSP48 Macro Consider the simple mod

- Page 157 and 158:

Reserved Port Identifier Opmode Sel

- Page 159 and 160:

DSP48 Macro Pseudo Opmode P=+C+P+Ci

- Page 161 and 162:

External Registers DSP48 Macro This

- Page 163 and 164:

DSP48 macro 2.0 Individual register

- Page 165 and 166:

DSP48 macro 2.0 1. Make sure that i

- Page 167 and 168:

DSP48 Macro 2.1 Block Parameters DS

- Page 169 and 170:

DSP48 Macro 2.1 shown below. Notice

- Page 171 and 172:

DSP48 Macro 2.1 You can find the ab

- Page 173 and 174:

DSP48A Provide PCOUT port: when se

- Page 175 and 176:

DSP48E Block Parameters Basic tab D

- Page 177 and 178:

DSP48E carryout. When the mode of o

- Page 179 and 180:

See Also Implementation DSP48E Para

- Page 181 and 182:

DSP48E1 subtracter in the adder/sub

- Page 183 and 184:

DSP48E1 Length of acout pipeline:

- Page 185 and 186:

Dual Port RAM Block Interface Dual

- Page 187 and 188:

Collision Behavior The result of si

- Page 189 and 190:

Xilinx LogiCORE Dual Port RAM This

- Page 191 and 192:

EDK Processor EDK Processor This bl

- Page 193 and 194:

Advanced tab Parameters specific to

- Page 195 and 196:

Expression Block Parameters Express

- Page 197 and 198:

Output Signals: Fast Fourier Transf

- Page 199 and 200:

Basic tab Fast Fourier Transform 7.

- Page 201 and 202:

Virtex-7, Kintex-7, Virtex-6, Spart

- Page 203 and 204:

Block Parameters Fast Fourier Trans

- Page 205 and 206:

Fast Fourier Transform 8.0 Display

- Page 207 and 208:

Data path and control signals: Fast

- Page 209 and 210:

FDATool Example of Use FDA Tool Int

- Page 211 and 212:

System Generator for DSP Reference

- Page 213 and 214:

FIR Compiler 5.0 coef_we: Used for

- Page 215 and 216:

FIR Compiler 5.0 The figure below s

- Page 217 and 218:

Number of paths: Specifies the numb

- Page 219 and 220:

FIR Compiler 6.2 FIR Compiler 6.2 T

- Page 221 and 222:

FIR Compiler 6.2 The output pins of

- Page 223 and 224:

FIR Compiler 6.2 User_Field: In th

- Page 225 and 226:

FIR Compiler 6.2 Both FIR Compiler

- Page 227 and 228:

FIR Compiler 6.2 The figure below s

- Page 229 and 230:

Filter Specification Filter Type:

- Page 231 and 232:

Implementation tab FIR Compiler 6.3

- Page 233 and 234:

Interface tab FIR Compiler 6.3 Data

- Page 235 and 236:

FIR Compiler 6.3 The figure below s

- Page 237 and 238:

From FIFO Block Parameters From FIF

- Page 239 and 240:

Output tab Output Type From FIFO S

- Page 241 and 242:

Binary point: position of the binar

- Page 243 and 244:

Gateway In Binary point: specifies

- Page 245 and 246:

System Generator Data Type Simulink

- Page 247 and 248:

Interleaver/De-interleaver 6.0 Inte

- Page 249 and 250:

Block Parameters Interleaver/De-int

- Page 251 and 252:

Interleaver/De-interleaver 6.0 Num

- Page 253 and 254:

Port Parameters tab Interleaver/De-

- Page 255 and 256:

Interleaver/De-interleaver 6.0 To a

- Page 257 and 258:

Device Support Virtex-7 and Kintex-

- Page 259 and 260:

Interleaver/De-interleaver 7.0 Alth

- Page 261 and 262:

AXI Interface Interleaver/De-interl

- Page 263 and 264:

Block Parameters Interleaver/De-int

- Page 265 and 266:

Rectangular Parameters #2 Tab Param

- Page 267 and 268:

Interleaver/De-interleaver 7.1 Inte

- Page 269 and 270:

Configuration Swapping Interleaver/

- Page 271 and 272:

Control Channel Input Signals: Inte

- Page 273 and 274:

COE File: The branch lengths are sp

- Page 275 and 276:

Interleaver/De-interleaver 7.1 ARE

- Page 277 and 278:

JTAG Co-Simulation Block Parameters

- Page 279 and 280:

Software tab JTAG Co-Simulation Par

- Page 281 and 282:

LFSR Feedback polynomial: This fie

- Page 283 and 284:

MCode MCode This block is listed in

- Page 285 and 286:

Relational operators: < Less than

- Page 287 and 288:

Constant Expressions MCode An expre

- Page 289 and 290:

Slice Function: xl_slice MCode Func

- Page 291 and 292:

MCode A method of a vector that que

- Page 293 and 294:

'b = ', num2str(b), ', ', ... 'x =

- Page 295 and 296:

FOR Loop FOR statement is fully unr

- Page 297 and 298:

MCode During the Simulink simulatio

- Page 299 and 300:

The following figure shows the bloc

- Page 301 and 302:

MCode The following M-code will als

- Page 303 and 304:

Pipelining Combinational Logic MCod

- Page 305 and 306:

ModelSim Block Parameters ModelSim

- Page 307 and 308:

Fine Points ModelSim The time scale

- Page 309 and 310:

ModelSim time scales. The actual de

- Page 311 and 312:

data type you select does not requi

- Page 313 and 314:

Multiple Subsystem Generator There

- Page 315 and 316:

domain_b_ce: in std_logic := '1'; d

- Page 317 and 318:

Mux Block Parameters This block is

- Page 319 and 320:

Natural Logarithm Natural Logarithm

- Page 321 and 322:

Network-based Ethernet Co-Simulatio

- Page 323 and 324:

Opmode Block Parameters Opmode This

- Page 325 and 326:

DSP48A Control Instruction Format D

- Page 327 and 328:

Instruction Field Name Carry In op[

- Page 329 and 330:

DSP48E1 Control Instruction Format

- Page 331 and 332:

Instruction Field Name Location Mne

- Page 333 and 334:

Pause Simulation Block Parameters P

- Page 335 and 336:

PicoBlaze Microcontroller Block Int

- Page 337 and 338:

PicoBlaze6 Instruction Display Bloc

- Page 339 and 340:

Block Interface Signal Direction De

- Page 341 and 342:

Device Support Supported PicoBlaze6

- Page 343 and 344:

Point-to-point Ethernet Co-Simulati

- Page 345 and 346:

Puncture Block Parameters Puncture

- Page 347 and 348:

Reciprocal SquareRoot Block Paramet

- Page 349 and 350:

Block Parameters Reed-Solomon Decod

- Page 351 and 352:

Reed-Solomon Decoder 7.1 Symbols P

- Page 353 and 354:

Reed-Solomon Decoder 8.0 Reed-Solom

- Page 355 and 356:

Reed-Solomon Decoder 8.0 event_s_c

- Page 357 and 358:

Attributes 2 tab Reed-Solomon Decod

- Page 359 and 360:

Reed-Solomon Encoder 7.1 Block Inte

- Page 361 and 362:

Block Parameters Reed-Solomon Encod

- Page 363 and 364:

Reed-Solomon Encoder 7.1 This is a

- Page 365 and 366:

Block Interface Channels and Pins R

- Page 367 and 368:

Reed-Solomon Encoder 8.0 Symbol wi

- Page 369 and 370:

Register Block Interface Block Para

- Page 371 and 372:

LogiCORE Documentation Device Suppo

- Page 373 and 374:

Reset Generator Block Parameters Re

- Page 375 and 376:

Resource Estimator hardware (except

- Page 377 and 378:

Resource Estimator design that is n

- Page 379 and 380:

System Generator for DSP Reference

- Page 381 and 382:

Register Block Interface Block Para

- Page 383 and 384:

Scale Block Parameters Xilinx LogiC

- Page 385 and 386:

Shared Memory Block Interface Share

- Page 387 and 388:

Block Parameters Basic tab Shared M

- Page 389 and 390:

Shared Memory Read FIFO Transaction

- Page 391 and 392:

Shared Memory Write FIFO Transactio

- Page 393 and 394:

Shift Block Parameters Xilinx LogiC

- Page 395 and 396:

Block Parameters Simulation Multipl

- Page 397 and 398:

Write Modes Single Port RAM Provid

- Page 399 and 400:

Xilinx LogiCORE Single Port RAM The

- Page 401 and 402:

Single-Step Simulation Block Parame

- Page 403 and 404:

SquareRoot Block Parameters Basic t

- Page 405 and 406:

System Generator Create interface

- Page 407 and 408:

c. Observe the elements in the gene

- Page 409 and 410:

System Generator Block icon displa

- Page 411 and 412:

Threshold Block Parameters Xilinx L

- Page 413 and 414:

Block Parameters Time Division Demu

- Page 415 and 416:

To FIFO Block Parameters To FIFO Th

- Page 417 and 418:

Output tab Output Type To FIFO Spe

- Page 419 and 420:

Output tab Specify explicit output

- Page 421 and 422:

Toolbar Block Interface Toolbar Thi

- Page 423 and 424:

Up Sample Block Interface Up Sample

- Page 425 and 426:

VDMA Interface 4.0 VDMA Interface 4

- Page 427 and 428:

X-Ref Target - Figure 1-5 X-Ref Tar

- Page 429 and 430:

VDMA Interface 4.0 AXI VDMA registe

- Page 431 and 432:

Block Parameters Basic tab VDMA Int

- Page 433 and 434:

VDMA Interface 5.4 VDMA Interface 5

- Page 435 and 436:

Block Parameters Basic tab VDMA Int

- Page 437 and 438:

Viterbi Decoder 7.0 Block Interface

- Page 439 and 440:

Viterbi Decoder 7.0 Best State Use

- Page 441 and 442:

Page7 tab Synchronization Options V

- Page 443 and 444:

Viterbi Decoder 8.0 Block Interface

- Page 445 and 446:

data points. The delay equals the d

- Page 447 and 448:

Viterbi Decoder 8.0 Best State Use

- Page 449 and 450:

LogiCORE Documentation Device Suppo

- Page 451 and 452:

WaveScope automatically updates. Yo

- Page 453 and 454:

Block Interface WaveScope Cursor >

- Page 455 and 456:

WaveScope A logic signal will, by d

- Page 457 and 458:

The Grid WaveScope Displaying the G

- Page 459 and 460:

Move Cursor Next WaveScope This opt

- Page 461 and 462:

Xilinx Reference Blockset Communica

- Page 463 and 464:

2 Channel Decimate by 2 MAC FIR Fil

- Page 465 and 466:

2n-tap Linear Phase MAC FIR Filter

- Page 467 and 468:

4-channel 8-tap Transpose FIR Filte

- Page 469 and 470:

5x5Filter tab. 5x5Filter The Xilinx

- Page 471 and 472:

BPSK AWGN Channel Block Parameters

- Page 473 and 474:

Block Parameters Reference CIC Filt

- Page 475 and 476:

Block Interface Block Parameters Co

- Page 477 and 478:

CORDIC DIVIDER Block Parameters Ref

- Page 479 and 480:

Reference CORDIC LOG 1. J. E. Volde

- Page 481 and 482:

CORDIC SQRT Block Parameters CORDIC

- Page 483 and 484:

Dual Port Memory Interpolation MAC

- Page 485 and 486:

m-channel n-tap Transpose FIR Filte

- Page 487 and 488:

Example Block Parameters Mealy Stat

- Page 489 and 490:

Mealy State Machine The following t

- Page 491 and 492:

Example Moore State Machine Conside

- Page 493 and 494:

Multipath Fading Channel Model Theo

- Page 495 and 496:

Functions Multipath Fading Channel

- Page 497 and 498:

Input Multipath Fading Channel Mode

- Page 499 and 500:

Reference Multipath Fading Channel

- Page 501 and 502:

n-tap MAC FIR Filter Block Paramete

- Page 503 and 504:

Example Registered Mealy State Mach

- Page 505 and 506:

Registered Moore State Machine Regi

- Page 507 and 508:

Block Parameters Registered Moore S

- Page 509 and 510:

Virtex2 Line Buffer Block Parameter

- Page 511 and 512:

White Gaussian Noise Generator Whit

- Page 513 and 514:

Xilinx XtremeDSP Kit Blockset Block

- Page 515 and 516:

XtremeDSP Co-Simulation Block Param

- Page 517 and 518:

XtremeDSP Digital to Analog Convert

- Page 519 and 520:

XtremeDSP LED Flasher Block Paramet

- Page 521 and 522:

System Generator Utilities xlAddTer

- Page 523 and 524:

xlAddTerms Syntax Description xlAdd

- Page 525 and 526:

Examples Remarks See Also optionStr

- Page 527 and 528:

See Also xlCache [maxentries] = xlC

- Page 529 and 530:

xlfda_denominator Syntax Descriptio

- Page 531 and 532:

xlGenerateButton Syntax Description

- Page 533 and 534:

xlgetparam and xlsetparam When xlse

- Page 535 and 536:

See Also directory: './bitstream' t

- Page 537 and 538:

See Also Example To illustrate how

- Page 539 and 540:

xlLoadChipScopeData Syntax Descript

- Page 541 and 542:

xlSBDBuilder JTAG Options: System G

- Page 543 and 544:

xlSetNonMemMap Syntax Description E

- Page 545 and 546:

xlSwitchLibrary Syntax Description

- Page 547 and 548:

Field Names Description [Default va

- Page 549 and 550:

Remarks See Also xlTBUtils The acti

- Page 551 and 552:

xlUpdateModel Syntax Description xl

- Page 553 and 554:

Examples Example 1: >> xlUpdateMode

- Page 555 and 556:

xlVersion Syntax Description See Al

- Page 557 and 558:

System Generator GUI Utilities Chap

- Page 559 and 560:

Xilinx BlockAdd As shown below, to

- Page 561 and 562:

Xilinx BlockConnect Simple Connecti

- Page 563 and 564:

Xilinx Tools > Terminate How to Use

- Page 565 and 566:

Verifying Input Port Data Type Requ

- Page 567 and 568:

Programmatic Access System Generato

- Page 569 and 570:

xInport xOutport System Generator A

- Page 571 and 572:

System Generator API for Programmat

- Page 573 and 574:

PG API Examples Hello World PG API

- Page 575 and 576:

MACC in a Masked Subsystem PG API E

- Page 577 and 578:

You’ll get the following subsyste

- Page 579 and 580:

PG API Error/Warning Handling & Mes

- Page 581 and 582:

M-Code Access to Hardware Co-Simula

- Page 583 and 584:

M-Hwcosim Examples M-Code Access to

- Page 585 and 586:

M-Code Access to Hardware Co-Simula

- Page 587 and 588:

Example 3 M-Code Access to Hardware

- Page 589 and 590:

M-Code Access to Hardware Co-Simula

- Page 591 and 592:

Resource Management M-Code Access t

- Page 593 and 594:

Write data Syntax h('portName') = i

- Page 595 and 596:

M-Code Access to Hardware Co-Simula

- Page 597 and 598:

elease(m); Description Releases the

- Page 599 and 600:

Set properties Syntax set(m, prop,

- Page 601 and 602:

xlHwcosimSimulate Syntax M-Code Acc

- Page 603 and 604:

Index Numerics 2 Channel Decimate b

- Page 605 and 606:

Expose Clock Ports option 408 Hybri