Bridgeless PFC Boosts Low-Line Efficiency - Power Electronics

Bridgeless PFC Boosts Low-Line Efficiency - Power Electronics

Bridgeless PFC Boosts Low-Line Efficiency - Power Electronics

Create successful ePaper yourself

Turn your PDF publications into a flip-book with our unique Google optimized e-Paper software.

<strong>Bridgeless</strong> <strong>PFC</strong> <strong>Boosts</strong><br />

<strong>Low</strong>-<strong>Line</strong> Effi ciency<br />

By Jon Mark Hancock,<br />

Principal Engineer,<br />

In neon Technologies, N.A.,<br />

Milpitas, Calif.<br />

A bridgeless input power<br />

factor boost converter<br />

o ers the potential for<br />

higher e ciency to meet<br />

increasing demands for<br />

power savings, especially<br />

in switch-mode powersupply<br />

applications at<br />

low-line voltages.<br />

ide input-voltage range<br />

power factor correction<br />

(<strong>PFC</strong>) converters present<br />

some of the most difficult<br />

component challenges in acdc<br />

power electronics. With an<br />

input-voltage range that can extend<br />

from 265 Vac to as low as 75 Vac,<br />

the range of operating conditions is<br />

relatively extreme with wide current<br />

operating range and duty-cycle demands.<br />

As energy costs soar, the<br />

pressure is on to fi nd ways to improve<br />

effi ciency in power supplies used for<br />

applications such as telecommunications<br />

and computing. One solution is<br />

the bridgeless <strong>PFC</strong> technique.<br />

<strong>Bridgeless</strong> boost <strong>PFC</strong> is a concept that<br />

has been long on promise for many years,<br />

but has not reached mainstream acceptance.<br />

Issues with EMI, robustness and the complexity<br />

of early confi gurations have stymied eff orts to<br />

realize the bridgeless boost <strong>PFC</strong> converter’s potential.<br />

Furthermore, improvements in components used in<br />

standard <strong>PFC</strong> boost converters have resulted in effi ciency<br />

gains that did not justify the extra cost and complexity of<br />

the bridgeless confi guration. And while bridgeless <strong>PFC</strong> has<br />

been viewed as a potentially useful technique to improve lowline<br />

input effi ciency, it is not certain that is where the demand for<br />

improvement lies today.<br />

As discussed in many forums over the last two years, the specifi -<br />

cation and evaluation of switch-mode power-supply (SMPS) systems<br />

is changing in response to the industry’s desire to save energy in the real<br />

<strong>Power</strong> <strong>Electronics</strong> Technology February 2008 14<br />

www.powerelectronics.com<br />

802PET20.indd 14 2/12/2008 9:36:58 AM

world. Traditionally, effi ciency has normally been specifi ed<br />

at full load for high- and low-line ranges, but now a more<br />

realistic approach is being widely adopted, looking at the<br />

behavior of the system and its effi ciency in the range where<br />

the SMPS usually operates.<br />

VIN [1] Th is means that for redundant<br />

power systems such as computing servers and telecom<br />

power, it is now realized that effi ciency in the 10% to 50%<br />

range must be considered along with full load behavior, as<br />

shown in Fig. 1.<br />

As a result, system manufacturers such as IBM are<br />

changing the focus of how they specify and procure power.<br />

Th is change has been driven by customers with limited abilities<br />

to expand data centers because of power and cooling<br />

capacity. While the best of contemporary<br />

conventional <strong>PFC</strong> designs can just meet<br />

such current voluntary standards as<br />

Green Grid and ClimateSavers, more<br />

stringent future requirements may force<br />

designers to look for new solutions. A<br />

bridgeless <strong>PFC</strong> input confi guration can<br />

help support these requirements, although<br />

it may require some rethinking<br />

of design methodology and optimization<br />

methods.<br />

Conventional <strong>PFC</strong><br />

Versus <strong>Bridgeless</strong><br />

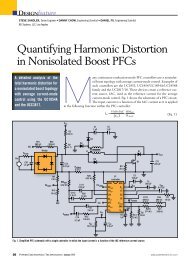

The well-known single-boost <strong>PFC</strong><br />

rectifi er confi guration shown in Fig. 2a<br />

consists of a full-bridge rectifi er input,<br />

which provides a rectified pulsating<br />

half-sine waveform applied to a boost<br />

converter consisting of switch S1, boost<br />

inductor L1 and boost rectifier D1,<br />

which charges a bulk rectifi er capacitor,<br />

“bus cap.”<br />

Fig. 2b shows the basic bridgeless<br />

boost concept, patented in 1983. [2] Th is<br />

variant shows a dual-winding inductor<br />

on one core. With alternating halfsine<br />

polarity on the ac line voltage, the<br />

MOSFETs alternate between operating<br />

as a low-frequency half-wave rectifi er<br />

diode connecting the ac line voltage to<br />

the bulk bus negative terminal. It also<br />

operates as a high-frequency chopper<br />

driving the respective boost inductor winding and boost<br />

rectifi er diode.<br />

Th is confi guration reduces the number of semiconductor<br />

devices in the inductor charging-current path from three to<br />

two, lowering conduction loss by about one diode-junction<br />

voltage drop (V F ). Th e MOSFETs conduct as either a highfrequency<br />

switch or a low-frequency half-wave rectifi er<br />

operating on alternate ac half cycles. As a result, some of<br />

the power losses normally handled by the ac bridge rectifi er<br />

V IN<br />

www.powerelectronics.com 15<br />

<strong>Power</strong> <strong>Electronics</strong> Technology February 2008<br />

<strong>Efficiency</strong> (%)<br />

95<br />

90<br />

85<br />

80<br />

75<br />

70<br />

Latest SMPS<br />

Proposed silver level<br />

Proposed gold level<br />

Typical SMPS<br />

65<br />

10 20 35 50 75 100<br />

Load (% rated power-supply output)<br />

Fig. 1. In some computing and telecom applications, power supplies<br />

are now expected to meet targets for effi ciency in the 10% to 50%<br />

load range, while still achieving high effi ciency at full load. [1]<br />

Boost<br />

inductor<br />

(a) Conventional boost <strong>PFC</strong> configuration<br />

L1a<br />

L1b<br />

Dual-winding<br />

boost inductor<br />

(b) Basic bridgeless boost <strong>PFC</strong> configuration<br />

Boost rectifier<br />

L1 IL D1<br />

D<br />

D1<br />

I L1a<br />

S1<br />

S1 S2<br />

Bus<br />

cap<br />

D2<br />

I L1b<br />

Vdc OUT<br />

+<br />

Load<br />

Vdc OUT<br />

Fig. 2. A comparison of the conventional single-boost <strong>PFC</strong> rectifi er confi gurations: The basic<br />

bridgeless boost <strong>PFC</strong> confi guration employs a full-bridge rectifi er, inductor, power MOSFET<br />

switch and bus capacitor (a). The conventional confi guration includes a dual-winding<br />

inductor on a single core, along with two power MOSFET switches, diodes D1 and D2, and<br />

an output capacitor (b).<br />

Load<br />

are now transferred to the power MOSFETs, potentially<br />

resulting in higher junction temperatures, which aff ects<br />

the overall MOSFET size.<br />

Deterring the industry’s adoption of the bridgeless <strong>PFC</strong><br />

are several innate confi guration characteristics. Because<br />

of the inductor confi guration and lack of a low-frequency<br />

path to the output, there is a relatively high common-mode<br />

switching voltage present at the bulk negative connection<br />

and no low-frequency path to the ac input. Th is can result<br />

in relatively high common-mode EMI because of the<br />

802PET20.indd 15 2/12/2008 9:37:03 AM<br />

I DC<br />

I DC

charge and discharge of normal parasitic<br />

capacitances associated with the converter’s<br />

physical construction.<br />

Sensing the input voltage and input current<br />

usually require isolated circuits due to<br />

the high-frequency potential between the<br />

ac input and output ground reference. It<br />

may even be necessary to use dual currentsense<br />

transformers (for switch and inductor<br />

current), while also applying rectifi ed<br />

half-sine voltage sensing on the primary. [3]<br />

Th is example makes no provision for precharging<br />

the bulk capacitance or dealing<br />

with surge stress encountered during cycle<br />

skip or low-line to high-line jumps.<br />

Hall Eff ect Current Sensing<br />

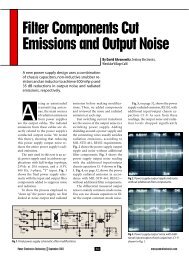

A modifi ed version of this confi guration<br />

was used to develop an experimental<br />

high-effi ciency bridgeless <strong>PFC</strong> front end<br />

in coordination with Isle Engineering,<br />

an independent consulting company in<br />

Ilmenau, Thuringia, Germany, up to a<br />

maximum output power level of 1500 W. [4]<br />

Fig. 3 shows the basic confi guration. Some<br />

of the design issues for this bridgeless <strong>PFC</strong><br />

were addressed with specifi c techniques to<br />

optimize effi ciency to the greatest extent<br />

possible, with a target value of 99% at full<br />

load. In practice, these eff orts made it possible<br />

to realize about 98.8% effi ciency at full<br />

output in the fi nished design.<br />

First, input-voltage sensing was eliminated by using a<br />

<strong>PFC</strong> controller based on single-cycle control, as pioneered<br />

by Smedly and Cuk. [5] Th is does not require input-voltage<br />

sensing and <strong>PFC</strong> controllers are available from vendors<br />

that use this technique. [6] Th e LAH25 wideband Hall Eff ect<br />

sensor with isolated data outputs accomplishes current<br />

sensing on the ac primary aft er the bulk precharge diodes<br />

D3 and D4. Th is component avoids the losses associated<br />

with resistive sensing and eliminates the need for sensing<br />

transformers in high-speed switching paths.<br />

Th e boost rectifi er diodes are silicon carbide, merged<br />

PiN Schottky types that combine the characteristics of<br />

Schottky and p-n diodes with nearly negligible reverse<br />

recovery charge (Q RR ) capacitive losses and low forward<br />

drop. The switching MOSFETs were selected for lowenergy-specifi<br />

ed output capacitance (C OSS ) to minimize<br />

turn-on loss and are capable of near zero-voltage switching<br />

turn-off with very low losses due to their output capacitance<br />

nonlinearity. [7]<br />

Th e control arrangements for this confi guration are<br />

somewhat complex, and a zero-crossing detector and<br />

driver-steering logic located aft er the PWM output of the<br />

<strong>PFC</strong> controller steer the driver signal to either S1 or S2.<br />

Th is depends on the ac-voltage input phase while driving<br />

V IN<br />

bridgeless pfc<br />

the other MOSFET as a synchronous rectifi er. A fl yback<br />

bias supply, using an integrated controller and FET, provides<br />

±12 V for the <strong>PFC</strong> controller and Hall Eff ect sensor<br />

module, which is part of the overall losses accounted for<br />

in the effi ciency measurement.<br />

Th is development was successful in demonstrating a<br />

range of techniques to achieve quite high effi ciency in the<br />

<strong>PFC</strong> front end, but it was limited to a high-line confi guration<br />

due to the lack of conventional heatsinks, and suff ers<br />

from the common-mode EMI issues of the original confi<br />

guration. Derivations of another proposed confi guration<br />

address these issues.<br />

Half-Wave Design<br />

A bridgeless half-wave rectifi ed dual boost <strong>PFC</strong> was<br />

proposed by Barbi and Souza that used insulated-gate bipolar<br />

transistors (IGBTs) with a nondissipative snubber to<br />

reduce switching losses. [8] IGBTs lack the functional body<br />

diode of MOSFETs, so diodes must accomplish input halfwave<br />

rectifi cation (slow-recovery diodes are suffi cient).<br />

A modifi cation of this design was adapted to MOSFETs,<br />

removing the nondissipative snubbers and adding diodes<br />

for bulk capacitor precharge (Fig. 4).<br />

Diodes D5 and D6 are low-frequency half-wave rectifi ers,<br />

www.powerelectronics.com 17<br />

<strong>Power</strong> <strong>Electronics</strong> Technology February 2008<br />

LAH25<br />

ZCD<br />

driver<br />

logic<br />

Isolated input current sense<br />

using Hall Effect sensor<br />

Dual-winding<br />

boost inductor<br />

L1a<br />

L1b<br />

<strong>Bridgeless</strong> boost <strong>PFC</strong> with bulk precharge, Hall current sense<br />

D3<br />

D1<br />

I L1a<br />

D4<br />

D2<br />

S1 S2<br />

I L1b<br />

Vdc OUT<br />

Fig. 3. A bridgeless boost <strong>PFC</strong> with bulk precharge and a Hall current sensor realizes about<br />

98.8% effi ciency at full output.<br />

V IN<br />

D3<br />

D5<br />

D6<br />

D4<br />

NTC<br />

L1<br />

L2<br />

Current<br />

sense<br />

D1<br />

I L1<br />

D2<br />

S1 S2<br />

<strong>Bridgeless</strong> boost <strong>PFC</strong> with half-wave rectifier and bulk bus precharge<br />

I L2<br />

+<br />

+<br />

Load<br />

Vdc OUT<br />

Fig. 4. A bridgeless boost <strong>PFC</strong> with half-wave and bulk bus precharge removes the nondissipative<br />

snubbers and adds diodes for bulk capacitor precharge.<br />

802PET20.indd 17 2/12/2008 9:37:04 AM<br />

Load<br />

I DC<br />

I DC

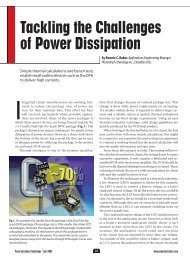

Losses (W)<br />

40<br />

30<br />

20<br />

10<br />

bridgeless pfc<br />

Conduction losses<br />

Capacitive losses CP Series<br />

CoolMOS CP 600 V Series<br />

0<br />

0 50 100<br />

Spec RDS (m)<br />

ON<br />

150 200<br />

(a) Loss minimal for 800 W, 130 kHz, 90 Vac<br />

Fig. 5. MOSFET losses in the boost <strong>PFC</strong> vary with the power MOSFET R DSON as demonstrated with a <strong>PFC</strong> stage configured for 800-W output<br />

(full load), switching at 130 kHz. For the case where input voltage is 90 Vac, conduction loss (shown in yellow) and switching loss (shown in<br />

red) are balanced and minimized at an R DSON of 30 mΩ (a). When input voltage is raised to 208 Vac , lowest losses occur with higher R DSON ,<br />

and reduced capacitive loss (b).<br />

alternately making a low-frequency connection between the<br />

ac line and the bulk negative connection. Diodes D3 and D4<br />

provide the bulk precharge function during startup and in<br />

SIP AD1 6/1/07 2:06 PM Page 1<br />

cycle skip or brownout recovery. The configuration of D3,<br />

D4, D5 and D6 forms a bridge and can be implemented<br />

Losses (W)<br />

0<br />

0 50 100<br />

Spec RDS (m)<br />

ON<br />

150 200<br />

(b) Loss minimal for 800 W, 130 kHz, 208 Vac<br />

with standard slow-recovery ac bridge rectifiers.<br />

Chopper switches S1 and S2 drive inductors L1 and L2<br />

on alternate line half cycles. This is a potential cost disadvantage<br />

compared with the combined coupled-inductor<br />

structure of the last example. However, by using separate<br />

cores high-frequency excitation and heating occurs for each<br />

inductor only during every other ac half cycle, providing<br />

thermal benefits that reduce inductor size and cost. Some<br />

half-wave rectification still occurs through the inductor<br />

and the MOSFET body diode, shown in Fig. 4, because<br />

they’re not the primary half-wave rectifier used for other<br />

configurations.<br />

The majority of current flows in diodes D5 and D6,<br />

slow-recovery half-wave rectifiers. This has the effect of<br />

reducing the power dissipation and maximum junction<br />

temperature in the MOSFET switches, which lowers their<br />

effective operating on-resistance (R DSON ). MOSFET R DSON<br />

can double between room temperature and maximum<br />

operating temperatures, so a lower junction temperature<br />

lowers conduction losses.<br />

In this configuration, current sense is at the same potential<br />

as the output load return and controller ground,<br />

allowing some flexibility in measurement technique and<br />

including the use of conventional resistive in-line sensing.<br />

Of course, resistive sensing increases the losses, but by<br />

how much?<br />

Let’s consider an example of a 1-kW output converter, assuming<br />

a nominal efficiency (η) of 90% and a low-input-line<br />

voltage of 90 Vac. Let’s assume that for the controller being<br />

used, we need 26 mΩ to generate the required maximum<br />

sense voltage. The peak input current is:<br />

(Eq. 1)<br />

<strong>Power</strong> <strong>Electronics</strong> Technology February 2008 18<br />

www.powerelectronics.com<br />

40<br />

30<br />

20<br />

10<br />

I<br />

PK<br />

POUT<br />

×<br />

=<br />

η×<br />

V<br />

IN MIN<br />

Conduction losses<br />

Capacitive losses CP Series<br />

CoolMOS CP 600 V Series<br />

2<br />

= 17. 64 A.<br />

The sense resistor power dissipation is:<br />

802PET20.indd 18 2/12/2008 9:37:06 AM

P<br />

SENSE<br />

2<br />

IPK<br />

= RSENSE<br />

⎛ ⎞<br />

⎜ ⎟ × = 4. 365 W. (Eq. 2)<br />

⎝ 2 ⎠<br />

This amounts to 0.5% efficiency loss at low line. However,<br />

if normal operation at high line and cost are a greater concern,<br />

at 208 Vac the total P SENSE loss is only 0.755 W, less than<br />

0.1%. This may be a tolerable tradeoff. Note that eliminating<br />

the extra diode drop of the conventional bridge diode even<br />

at high line may save 5 W to 8 W.<br />

Examining this bridgeless <strong>PFC</strong> configuration, it could<br />

appear that the component count is double that of the conventional<br />

<strong>PFC</strong> configuration in Fig. 2a. In reality, with the<br />

same total MOSFET and boost rectifier silicon “budget” in<br />

either configuration, a higher total efficiency can be achieved<br />

with the bridgeless configuration. And considering the<br />

targets shown in Fig. 1, achieving higher efficiency at the<br />

lower power ranges is well served by splitting up the switch<br />

and diode budget between the dual boost phases.<br />

To understand why this is so, examine the selection of the<br />

MOSFETs based on a conventional boost <strong>PFC</strong> that delivers<br />

the lowest total losses at full load and low-line ac. An Excel<br />

workbook was used to do this, with some assumptions translated<br />

from the data sheet to the application (Fig. 5a).<br />

Fig. 5 shows an 800-W output <strong>PFC</strong> application, with a<br />

net input to output efficiency of 85%, which is used to factor<br />

up the required input power. The switching frequency<br />

bridgeless pfc<br />

is 130 kHz, with an input voltage of either 90 Vac in Fig.<br />

5a or 208 Vac in Fig. 5b. The x axis is the nominal R DSON<br />

specification, but this is not used for calculation; instead,<br />

the R DSON is normalized to 105°C for the calculation of<br />

conduction losses.<br />

Since turn-off losses can be made nearly negligible with<br />

super-junction MOSFETs [7] , the focus for dynamic losses is<br />

on C OSS discharge at turn-on, an unavoidable loss in hardswitching<br />

circuits. With conventional diodes, this loss might<br />

be nearly swamped out by the Q RR and C OSS of the boost<br />

rectifier diode. With modern silicon carbide and even silicon<br />

ultrafast diodes, the output capacitance of the MOSFETs can<br />

play a dominant role in losses. [9]<br />

Looking at Fig. 5a, the minimum of the loss curve occurs<br />

for a specified R DSON of 25 mΩ to 30 mΩ. At this point, at<br />

full load and low line, the conduction and switching losses<br />

are balanced and minimized. This low resistance would take<br />

two 75-mΩ TO-247 MOSFETs in parallel to achieve. This<br />

may not be the best way to achieve efficiency, particularly<br />

if we consider the bridgeless option. Those switching losses<br />

due to C OSS capacitance will be there regardless of the load<br />

current or line voltage.<br />

Considering that the bridgeless option can save 5 W to 8<br />

W or more in conduction losses, we can take that savings into<br />

account in derating the conduction performance requirement<br />

for the MOSFETs. Moving on the loss line to the right,<br />

Take a look at our broad offering of quality<br />

power modules and fi nd out why Bel is now<br />

the preferred source for dc-dc converters.<br />

Finally, you can get cost effective products<br />

in industry standard form factors without<br />

sacrifi cing performance. To learn more<br />

about how Bel can help you power your<br />

next system, visit us at www.belpower.com.<br />

High Effi ciency <strong>Power</strong> Modules<br />

www.belpower.com • 1-800-BELFUSE<br />

Isolated Converters-Single & Dual Output<br />

•1/16, 1/8, 1/4, 1/2 Bricks up to 120A<br />

Bus Converters-4:1, 5:1, 6:1 Fixed Ratios<br />

•1/16, 1/8, 1/4 Bricks up to 500W<br />

VRMs-Solutions for most Microprocessors<br />

•Up to 150A Output; Goldfi nger and TH<br />

Non-Isolated POL Modules-Boost, Buck<br />

and Inverting<br />

•1A to 150A Output; Vertical Mount or SMT<br />

power PE 4-30-07.indd 1 6/27/07 12:14:13 PM<br />

www.powerelectronics.com 19<br />

<strong>Power</strong> <strong>Electronics</strong> Technology February 2008<br />

802PET20.indd 19 2/12/2008 9:37:08 AM

idgeless pfc<br />

the losses increase as a function of conduction loss, so it’s<br />

possible to move over to the right, where conduction losses<br />

are up by 5 W to 7 W, and write that off due to the conduction<br />

loss improvement of the bridgeless configuration.<br />

Most importantly, shifting to a single 75-mΩ, instead of<br />

a 25-mΩ to 30-mΩ MOSFET cuts C switching losses in<br />

OSS<br />

half. Therefore, switching loss reduction at all other load<br />

ranges and line voltages will be significant. This is shown in<br />

Fig. 5b for operation at full load at the SMPS normal operating<br />

208-Vac input, where the optimum MOSFET choice<br />

would appear to be around 100-mΩ. In fact, if you have that<br />

so-called “optimum” conventional MOSFET of 25 mΩ to<br />

30 mΩ for low-line performance in a conventional <strong>PFC</strong><br />

circuit, the total losses at full load are doubled for the<br />

MOSFET, due to higher C switching loss when operating<br />

OSS<br />

at 208 Vac. The loss is even worse at 50% load and below.<br />

PETech<br />

References<br />

1. Janick, J., “IBM Technology and Solutions,” IBM <strong>Power</strong><br />

and Cooling Symposium, October 2007, Raleigh, N.C.,<br />

proceedings at www-03.ibm.com/procurement.<br />

2. Mitchell, D.M., “AC-DC Converter Having an Improved<br />

<strong>Power</strong> Factor,” U.S. Patent 4,412,277, Oct. 25, 1983.<br />

3. Moriconi, U., “A <strong>Bridgeless</strong> <strong>PFC</strong> Configuration Based<br />

CKE-PET on L4981 7-06 <strong>PFC</strong> 12/27/07 Controller,” 10:10 Application AM Page Note 1AN<br />

1606,<br />

REPLACEMENTS<br />

FOR MANY<br />

FUJI DIODES<br />

AVAILABLE<br />

1 kV to 300 kV<br />

Fast Recovery<br />

down to 35nS<br />

Average Forward<br />

Current up to<br />

10 Amps<br />

HVCA diodes are ideal for use<br />

in high voltage power supplies<br />

and multipliers found in<br />

medical equipment and<br />

instrumentation. They<br />

are also well-suited for<br />

aerospace, military,<br />

automotive, down hole and<br />

high temperature applications<br />

and X-ray equipment used<br />

for medical, dental,<br />

industrial and<br />

security purposes.<br />

HVCA<br />

P.O. Box 848, Farmingdale, NJ 07727<br />

(732) 938-4499 (732) 938-4451 FAX<br />

e-mail: info@hvca.com www.hvca.com<br />

STMicroelectronics, November 2002.<br />

4. Hancock, J., “Meeting the Challenge for Offline SMPS<br />

Through Improved Semiconductor Current Density,”<br />

IBM <strong>Power</strong> and Cooling Symposium, 2005, proceedings<br />

at www-03.ibm.com/procurement.<br />

5. Smith, K.M., Jr.; Lai, Z.; and Smedley, K.M., “A New PWM<br />

Controller with One-Cycle response,” IEEE Transactions<br />

on <strong>Power</strong> <strong>Electronics</strong>, Volume 14, Issue 1, January 1999,<br />

pp. 142-150.<br />

6. Lu, B.; Brown, R.; and Soldano, M., “<strong>Bridgeless</strong> <strong>PFC</strong><br />

Implementation Using One Cycle Control Technique,”<br />

IEEE Applied <strong>Power</strong> <strong>Electronics</strong> Conference (APEC) 2005<br />

proceedings, pp. 812-817.<br />

7. Bjoerk, F.; Hancock, J.; and Deboy, G., “CoolMOS CP:<br />

How to Make Most Beneficial Use of the Latest Generation<br />

of Super Junction Technology Devices,” AN-CoolMOS<br />

CP-01, www.infineon.com.<br />

8. Souza, A.F., and Barbi, I., “High <strong>Power</strong> Factor Rectifier<br />

with Reduced Conduction and Commutation Losses,’’<br />

International Telecommunication Energy Conference<br />

(INTELEC) proceedings, June 1999, session 8, paper 1.<br />

9. Lu, B.; Dong, W.; Shao, Q.; and Lee, F., “Performance<br />

Evaluation of CoolMOS and SiC Diode for Single Phase<br />

<strong>Power</strong> Factor Correction Applications,” IEEE APEC 2003<br />

proceedings.<br />

Minisens<br />

FHS Current<br />

transducer<br />

Minisens is taking miniaturization to the next level as it<br />

is a fully fledged isolated current transducer including<br />

magnetic concentrators in an IC SO8 size.<br />

• Non-contact, no insertion<br />

losses<br />

• Isolation provider<br />

• Attractive price<br />

• Flexible design to measure<br />

2-70 A RMS<br />

• +5V power supply<br />

• Access to voltage reference<br />

• Ratiometric or fixed gain and<br />

offset<br />

• Standby mode pin<br />

• Dedicated additional fast output<br />

for short circuit detection<br />

• High performance gain and<br />

offset thermal drifts<br />

www.lem.com<br />

At the heart of power electronics<br />

<strong>Power</strong> <strong>Electronics</strong> Technology February 2008 20<br />

www.powerelectronics.com<br />

802PET20.indd 20 2/12/2008 9:37:09 AM