Note: Please refer to ASIX Multi-Port Ethernet Controller Application ...

Note: Please refer to ASIX Multi-Port Ethernet Controller Application ...

Note: Please refer to ASIX Multi-Port Ethernet Controller Application ...

You also want an ePaper? Increase the reach of your titles

YUMPU automatically turns print PDFs into web optimized ePapers that Google loves.

5<br />

4<br />

3<br />

2<br />

1<br />

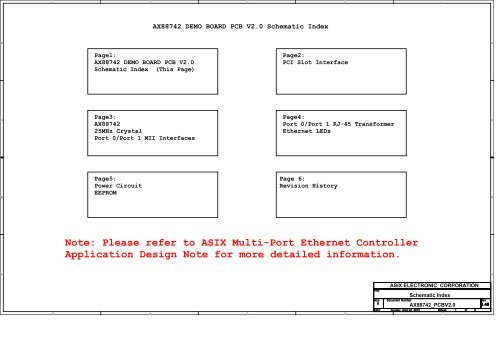

AX88742 DEMO BOARD PCB V2.0 Schematic Index<br />

D<br />

D<br />

Page1:<br />

AX88742 DEMO BOARD PCB V2.0<br />

Schematic Index (This Page)<br />

Page2:<br />

PCI Slot Interface<br />

C<br />

Page3:<br />

AX88742<br />

25MHz Crystal<br />

<strong>Port</strong> 0/<strong>Port</strong> 1 MII Interfaces<br />

Page4:<br />

<strong>Port</strong> 0/<strong>Port</strong> 1 RJ-45 Transformer<br />

<strong>Ethernet</strong> LEDs<br />

C<br />

B<br />

Page5:<br />

Power Circuit<br />

EEPROM<br />

Page 6:<br />

Revision His<strong>to</strong>ry<br />

B<br />

<strong>Note</strong>: <strong>Please</strong> <strong>refer</strong> <strong>to</strong> <strong>ASIX</strong> <strong>Multi</strong>-<strong>Port</strong> <strong>Ethernet</strong> <strong>Controller</strong><br />

<strong>Application</strong> Design <strong>Note</strong> for more detailed information.<br />

A<br />

A<br />

5<br />

4<br />

3<br />

2<br />

Title<br />

<strong>ASIX</strong> ELECTRONIC CORPORATION<br />

Schematic Index<br />

Size Document Number Rev<br />

B<br />

AX88742_PCBV2.0<br />

Date: Sunday, April 04, 2010<br />

Sheet 1 of<br />

6<br />

1<br />

1.40

8<br />

7<br />

6<br />

5<br />

4<br />

3<br />

2<br />

1<br />

D<br />

C<br />

B<br />

P3<br />

P3<br />

P3<br />

P3<br />

P3<br />

P3<br />

P3<br />

P3<br />

P3<br />

P3<br />

P3<br />

P3<br />

P3<br />

P3<br />

P3<br />

P3<br />

P3<br />

P3<br />

P3<br />

P3<br />

P3<br />

P3<br />

P3<br />

P3<br />

P3<br />

P3<br />

P3<br />

P3<br />

P3<br />

P3<br />

P3<br />

P3<br />

P3<br />

P3<br />

P3<br />

P3<br />

P3<br />

P3<br />

P3<br />

P3<br />

P3<br />

P3<br />

P3<br />

P3<br />

P3<br />

P3<br />

P3<br />

P3<br />

P3<br />

P3<br />

P3<br />

AD0<br />

AD1<br />

AD2<br />

AD3<br />

AD4<br />

AD5<br />

AD6<br />

AD7<br />

AD8<br />

AD9<br />

AD10<br />

AD11<br />

AD12<br />

AD13<br />

AD14<br />

AD15<br />

AD16<br />

AD17<br />

AD18<br />

AD19<br />

AD20<br />

AD21<br />

AD22<br />

AD23<br />

AD24<br />

AD25<br />

AD26<br />

AD27<br />

AD28<br />

AD29<br />

AD30<br />

AD31<br />

FRAME#<br />

IRDY#<br />

PCI_CLK<br />

RESETN<br />

PERR#<br />

SERR#<br />

PAR<br />

IDSEL<br />

C/BE0#<br />

C/BE1#<br />

C/BE2#<br />

C/BE3#<br />

INT<br />

PME<br />

GNT#<br />

REQ#<br />

TRDY#<br />

DEVSEL#<br />

STOP#<br />

AD0<br />

AD1<br />

AD2<br />

AD3<br />

AD4<br />

AD5<br />

AD6<br />

AD7<br />

AD8<br />

AD9<br />

AD10<br />

AD11<br />

AD12<br />

AD13<br />

AD14<br />

AD15<br />

AD16<br />

AD17<br />

AD18<br />

AD19<br />

AD20<br />

AD21<br />

AD22<br />

AD23<br />

AD24<br />

AD25<br />

AD26<br />

AD27<br />

AD28<br />

AD29<br />

AD30<br />

AD31<br />

FRAME#<br />

IRDY#<br />

PCI_CLK<br />

RESETN<br />

PERR#<br />

SERR#<br />

PAR<br />

IDSEL<br />

C/BE0#<br />

C/BE1#<br />

C/BE2#<br />

C/BE3#<br />

INT<br />

PME<br />

GNT#<br />

REQ#<br />

TRDY#<br />

DEVSEL#<br />

STOP#<br />

C51<br />

0.1uF<br />

PCI_CLK<br />

+ C50<br />

47uF<br />

GND<br />

R25 10<br />

R23 0<br />

R24 0<br />

VCC33P<br />

C54<br />

0.1uF<br />

VCC33P<br />

C26<br />

C55<br />

+<br />

0.1uF<br />

47uF<br />

GND<br />

VCC5P<br />

PRSNT1#<br />

PRSNT2#<br />

GND<br />

GND<br />

REQ#<br />

AD31<br />

AD29<br />

GND<br />

AD27<br />

AD25<br />

C/BE3#<br />

AD23<br />

GND<br />

AD21<br />

AD19<br />

AD17<br />

C/BE2#<br />

GND<br />

IRDY#<br />

DEVSEL#<br />

GND<br />

PERR#<br />

SERR#<br />

C/BE1#<br />

AD14<br />

GND<br />

AD12<br />

AD10<br />

GND<br />

AD8<br />

AD7<br />

AD5<br />

AD3<br />

GND<br />

AD1<br />

VCC5P<br />

C56<br />

C57<br />

+<br />

0.1uF<br />

47uF<br />

JB1<br />

1<br />

-12V<br />

2<br />

TCK<br />

3<br />

GND<br />

4<br />

TDO<br />

5<br />

+5V<br />

6<br />

+5V<br />

7<br />

INTB#<br />

8<br />

INTD#<br />

9<br />

PRSNT1#<br />

10<br />

RESERVED<br />

11<br />

PRSNT2#<br />

14<br />

RESERVED<br />

15<br />

GND<br />

16<br />

CLK<br />

17<br />

GND<br />

18<br />

REQ#<br />

19<br />

+3.3V(I/O)<br />

20<br />

AD31<br />

21<br />

AD29<br />

22<br />

GND<br />

23<br />

AD27<br />

24<br />

AD25<br />

25<br />

+3.3V<br />

26<br />

C/BE3#<br />

27<br />

AD23<br />

28<br />

GND<br />

29<br />

AD21<br />

30<br />

AD19<br />

31<br />

+3.3V<br />

32<br />

AD17<br />

33<br />

C/BE2#<br />

34<br />

GND<br />

35<br />

IRDY#<br />

36<br />

+3.3V<br />

37<br />

DEVSEL#<br />

38<br />

GND<br />

39<br />

LOCK#<br />

40<br />

PERR#<br />

41<br />

+3.3V<br />

42<br />

SERR#<br />

43<br />

+3.3V<br />

44<br />

C/BE1#<br />

45<br />

AD14<br />

46<br />

GND<br />

47<br />

AD12<br />

48<br />

AD10<br />

49<br />

M66EN<br />

52<br />

AD8<br />

53<br />

AD7<br />

54<br />

+3.3V<br />

55<br />

AD5<br />

56<br />

AD3<br />

57<br />

GND<br />

58<br />

AD1<br />

59<br />

+3.3V(I/O)<br />

60<br />

ACK64#<br />

61<br />

+5V<br />

62<br />

+5V<br />

PCIJB<br />

JA1<br />

TRST#<br />

1<br />

+12V<br />

2<br />

TMS<br />

3<br />

TDI<br />

4<br />

+5V<br />

5<br />

INTA#<br />

6<br />

INTC#<br />

7<br />

+5V<br />

8<br />

RESERVED 9<br />

+3.3V(I/O)<br />

10<br />

RESERVED 11<br />

3.3Vaux<br />

14<br />

RST#<br />

15<br />

+3.3V(I/O)<br />

16<br />

GNT#<br />

17<br />

GND 18<br />

PME#<br />

19<br />

AD30<br />

20<br />

+3.3V<br />

21<br />

AD28<br />

22<br />

AD26<br />

23<br />

GND 24<br />

AD24<br />

25<br />

IDSEL<br />

26<br />

+3.3V<br />

27<br />

AD22<br />

28<br />

AD20<br />

29<br />

GND 30<br />

AD18<br />

31<br />

AD16<br />

32<br />

+3.3V<br />

33<br />

FRAME#<br />

34<br />

GND 35<br />

TRDY#<br />

36<br />

GND 37<br />

STOP#<br />

38<br />

+3.3V<br />

39<br />

RESERVED 40<br />

RESERVED 41<br />

GND 42<br />

PAR 43<br />

AD15<br />

44<br />

+3.3V<br />

45<br />

AD13<br />

46<br />

AD11<br />

47<br />

GND 48<br />

AD9<br />

49<br />

C/BE0#<br />

52<br />

+3.3V<br />

53<br />

AD6<br />

54<br />

AD4<br />

55<br />

GND 56<br />

AD2<br />

57<br />

AD0<br />

58<br />

+3.3V(I/O)<br />

59<br />

REQ64#<br />

60<br />

+5V<br />

61<br />

+5V<br />

62<br />

PCIJA<br />

VCC5P<br />

INT<br />

VCC5P<br />

3.3VAUX<br />

RESETN<br />

GNT#<br />

C53<br />

GND<br />

0.1uF<br />

PME<br />

AD30<br />

AD28<br />

AD26<br />

GND<br />

AD24<br />

IDSEL<br />

AD22<br />

AD20<br />

GND<br />

AD18<br />

AD16<br />

FRAME#<br />

GND<br />

TRDY#<br />

GND<br />

STOP#<br />

GND<br />

PAR<br />

AD15<br />

VCC33P<br />

AD13<br />

AD11<br />

C25<br />

GND<br />

AD9<br />

0.1uF<br />

C/BE0#<br />

VCC33P<br />

AD6<br />

AD4<br />

C27<br />

GND<br />

AD2<br />

0.1uF<br />

AD0<br />

VCC5P<br />

C58<br />

0.1uF<br />

C24<br />

0.1uF<br />

+ C52<br />

47uF<br />

D<br />

C<br />

B<br />

A<br />

P5<br />

P5<br />

P5<br />

P3,4,5<br />

VCC33P<br />

VCC5P<br />

3.3VAUX<br />

GND<br />

VCC33P<br />

VCC5P<br />

3.3VAUX<br />

GND<br />

A<br />

8<br />

7<br />

6<br />

5<br />

4<br />

3<br />

Title<br />

<strong>ASIX</strong> ELECTRONICS CORPORATION<br />

PCI I/F<br />

Size Document Number Rev<br />

B<br />

AX88742_PCBV2.0<br />

Date: Sunday, April 04, 2010<br />

Sheet 2 of<br />

6<br />

2<br />

1<br />

1.40

8<br />

2<br />

1<br />

7<br />

6<br />

5<br />

4<br />

3<br />

2<br />

1<br />

D<br />

C<br />

B<br />

P2<br />

P2<br />

P2<br />

P2<br />

P2<br />

P2<br />

P2<br />

P2<br />

P2<br />

P2<br />

P2<br />

P2<br />

P2<br />

P2<br />

P2<br />

P2<br />

P2<br />

P2<br />

P2<br />

P2<br />

P2<br />

P2<br />

P2<br />

P2<br />

P2<br />

P2<br />

P2<br />

P2<br />

P2<br />

P2<br />

P2<br />

P2<br />

P2<br />

P2<br />

FRAME#<br />

IRDY#<br />

P2 PCI_CLK<br />

P2 RESETN<br />

P2 PERR#<br />

P2 SERR#<br />

P2 PAR<br />

P2<br />

P2<br />

P2<br />

P2<br />

P2<br />

P2<br />

P2<br />

P2<br />

P2<br />

IDSEL<br />

C/BE0#<br />

C/BE1#<br />

C/BE2#<br />

C/BE3#<br />

INT<br />

PME<br />

P0_RXIN<br />

P0_RXIP<br />

P0_TXON<br />

P0_TXOP<br />

P1_RXIN<br />

P1_RXIP<br />

P1_TXON<br />

P1_TXOP<br />

EECS<br />

EESK<br />

EEDIO<br />

VCC33<br />

AD0<br />

AD1<br />

AD2<br />

AD3<br />

AD4<br />

AD5<br />

AD6<br />

AD7<br />

AD8<br />

AD9<br />

AD10<br />

AD11<br />

AD12<br />

AD13<br />

AD14<br />

AD15<br />

AD16<br />

AD17<br />

AD18<br />

AD19<br />

AD20<br />

AD21<br />

AD22<br />

AD23<br />

AD24<br />

AD25<br />

AD26<br />

AD27<br />

AD28<br />

AD29<br />

AD30<br />

AD31<br />

GNT#<br />

REQ#<br />

P2 TRDY#<br />

P2 DEVSEL#<br />

P2 STOP#<br />

P4 MII0_TXD0<br />

P4 MII0_TXD1<br />

P4 MII0_TXD2<br />

P4 MII1_TXD0<br />

P4 MII1_TXD1<br />

P4 MII1_TXD2<br />

P4<br />

P4<br />

P4<br />

P4<br />

P4<br />

P4<br />

P4<br />

P4<br />

P5<br />

P5<br />

P5<br />

P5<br />

P5<br />

P4,5<br />

VCC5P<br />

3.3VAUX<br />

P5 VCC33-18<br />

P4,5 VCC33A<br />

P5 VCC18<br />

P5 VCC18A<br />

P2,4,5 GND<br />

AD0<br />

AD1<br />

AD2<br />

AD3<br />

AD4<br />

AD5<br />

AD6<br />

AD7<br />

AD8<br />

AD9<br />

AD10<br />

AD11<br />

AD12<br />

AD13<br />

AD14<br />

AD15<br />

AD16<br />

AD17<br />

AD18<br />

AD19<br />

AD20<br />

AD21<br />

AD22<br />

AD23<br />

AD24<br />

AD25<br />

AD26<br />

AD27<br />

AD28<br />

AD29<br />

AD30<br />

AD31<br />

FRAME#<br />

IRDY#<br />

PCI_CLK<br />

RESETN<br />

PERR#<br />

SERR#<br />

PAR<br />

IDSEL<br />

C/BE0#<br />

C/BE1#<br />

C/BE2#<br />

C/BE3#<br />

INT<br />

PME<br />

GNT#<br />

REQ#<br />

TRDY#<br />

DEVSEL#<br />

STOP#<br />

MII0_TXD0<br />

MII0_TXD1<br />

MII0_TXD2<br />

MII1_TXD0<br />

MII1_TXD1<br />

MII1_TXD2<br />

P0_RXIN<br />

P0_RXIP<br />

P0_TXON<br />

P0_TXOP<br />

P1_RXIN<br />

P1_RXIP<br />

P1_TXON<br />

P1_TXOP<br />

EECS<br />

EESK<br />

EEDIO<br />

VCC5P<br />

3.3VAUX<br />

VCC33<br />

VCC33-18<br />

VCC33A<br />

VCC18<br />

VCC18A<br />

GND<br />

VCC33<br />

GND<br />

GND<br />

MII0_RX_COL<br />

MII0_RXD2<br />

MII0_RXD0<br />

MII0_RX_CLK<br />

MII0_TX_EN<br />

MII0_TXD1<br />

MII0_TXD3<br />

MII0_MDIO<br />

GND<br />

25MHz +- 30ppm Crystal *<strong>Note</strong>3-1<br />

for <strong>Port</strong> 0/<strong>Port</strong> 1 <strong>Ethernet</strong> I/F<br />

P0_XTLP<br />

C6<br />

27pF<br />

50MHz Reference Clock Circuit<br />

for RMII/Reverse-RMII Modes<br />

Optional<br />

VCC18<br />

MII0 Interface Connec<strong>to</strong>r<br />

Optional<br />

J2<br />

MII1_TX_CLK<br />

P0_XTLN<br />

C7<br />

27pF<br />

6<br />

7<br />

8<br />

9<br />

10<br />

11<br />

14<br />

MII0_TXD3<br />

MII0_TXD2<br />

MII0_TXD1<br />

MII0_TXD0<br />

MII0_TX_EN<br />

MII0_TX_CLK<br />

MII0_RX_CLK<br />

MII0_RXD3<br />

MII0_RXD2<br />

MII0_RXD1<br />

MII0_RXD0<br />

MII0_RX_DV<br />

MII0_RX_CLK<br />

MII0_TX_CLK<br />

MII1_RX_CLK<br />

J2 HEADER Table MII0 Interface<br />

AX88742 J2<br />

Reverse<br />

PIN PIN MII Mode MII Mode RMII Mode<br />

123<br />

122<br />

121<br />

120<br />

113<br />

112<br />

70<br />

C32<br />

NC,0.1uF<br />

4<br />

1<br />

OSC1<br />

VDD<br />

E/D<br />

NC,50.000MHz<br />

R32<br />

Y1<br />

O/P 3<br />

GND 2<br />

1M<br />

25.000MHz<br />

R14<br />

*<strong>Note</strong>3-5/*<strong>Note</strong>3-6<br />

24<br />

22<br />

20<br />

18<br />

16<br />

14<br />

12<br />

10<br />

8<br />

6<br />

4<br />

2<br />

C33<br />

10uF<br />

R33 0,0805<br />

C31<br />

0.1uF<br />

R13<br />

NC,0<br />

*<strong>Note</strong>3-8<br />

NC,HEADER 12X2<br />

23 GND<br />

21 MII0_RX_CRS<br />

19 MII0_RXD3<br />

17 MII0_RXD1<br />

15 MII0_RX_DV<br />

13<br />

11 MII0_TX_CLK<br />

9 MII0_TXD0<br />

7 MII0_TXD2<br />

5 MII0_MDC<br />

3 GND<br />

1 GND<br />

J3<br />

NC,HEADER 2<br />

NC,0<br />

*<strong>Note</strong>3-3<br />

VCC33<br />

L1<br />

NC,PBY160808T-110Y-S<br />

VCC33-18<br />

L4<br />

NC,PBY160808T-110Y-S<br />

NC<br />

NC<br />

MII0_TXD1<br />

MII0_TXD0<br />

MII0_TX_EN<br />

MII0_REFCLKO<br />

MII0_REFCLK<br />

C29<br />

10uF<br />

*<strong>Note</strong>3-2<br />

3.3VAUX<br />

MII1_TXD3<br />

Reverse<br />

RMII Mode<br />

NC<br />

NC<br />

*<strong>Note</strong>3-9<br />

*<strong>Note</strong>3-4<br />

C30<br />

0.1uF<br />

MII0_RXD1<br />

MII0_RXD0<br />

MII0_CRSDV<br />

R40<br />

12.1 K 1%<br />

R39<br />

12.1 K 1%<br />

MII0_REFCLKO<br />

MII0_REFCLK<br />

R47<br />

4.7K<br />

R17<br />

4.7K<br />

R44 0,0805<br />

GND<br />

P0_TXON<br />

P0_TXOP<br />

P0_RXIN<br />

P0_RXIP<br />

P0_XTLN<br />

P0_XTLP<br />

P1_TXON<br />

P1_TXOP<br />

P1_RXIN<br />

P1_RXIP<br />

MII0_MDIO<br />

MII0_MDC<br />

MII0_RX_CLK<br />

MII0_RX_DV<br />

MII0_RXD0<br />

MII0_RXD1<br />

MII0_RXD2<br />

MII0_RXD3<br />

MII0_RX_CRS<br />

MII0_RX_COL<br />

MII0_TX_CLK<br />

MII0_TX_EN<br />

MII0_TXD0<br />

MII0_TXD1<br />

MII0_TXD2<br />

MII0_TXD3<br />

MII1_MDIO<br />

MII1_MDC<br />

MII1_RX_CLK<br />

MII1_RX_DV<br />

MII1_RXD0<br />

MII1_RXD1<br />

MII1_RXD2<br />

MII1_RXD3<br />

MII1_RX_CRS<br />

MII1_RX_COL<br />

MII1_TX_CLK<br />

MII1_TX_EN<br />

MII1_TXD0<br />

MII1_TXD1<br />

MII1_TXD2<br />

46<br />

47<br />

48<br />

49<br />

44<br />

43<br />

31<br />

VCC33<br />

VCC33<br />

VCC33<br />

VCC18<br />

VCC18<br />

VCC18<br />

VCC18<br />

VCC18-S<br />

VCC33-S<br />

VCC33A<br />

VCC33A<br />

VCC18A<br />

VCC18A<br />

VCC18A<br />

VCC18A<br />

7<br />

18<br />

1<br />

13<br />

14<br />

24<br />

25<br />

45<br />

72<br />

106<br />

128<br />

MII1 Interface Connec<strong>to</strong>r<br />

Optional<br />

2<br />

3<br />

5<br />

6<br />

9<br />

11<br />

12<br />

23<br />

22<br />

20<br />

19<br />

16<br />

107<br />

108<br />

70<br />

71<br />

91<br />

92<br />

96<br />

97<br />

100<br />

101<br />

112<br />

113<br />

120<br />

121<br />

122<br />

123<br />

29<br />

30<br />

31<br />

34<br />

35<br />

36<br />

37<br />

38<br />

32<br />

33<br />

43<br />

44<br />

49<br />

48<br />

47<br />

46<br />

42<br />

78<br />

105<br />

53<br />

65<br />

87<br />

118<br />

27<br />

26<br />

8<br />

17<br />

10<br />

15<br />

21<br />

4<br />

GND<br />

GND<br />

MII1_RX_COL<br />

MII1_RXD2<br />

MII1_RXD0<br />

MII1_RX_CLK<br />

MII1_TX_EN<br />

MII1_TXD1<br />

MII1_TXD3<br />

MII1_MDIO<br />

GND<br />

U4<br />

P0_TXON<br />

P0_TXOP<br />

P0_RXIN<br />

P0_RXIP<br />

P0_RSET_BG<br />

P0_XTLN<br />

P0_XTLP<br />

P1_TXON<br />

P1_TXOP<br />

P1_RXIN<br />

P1_RXIP<br />

P1_RSET_BG<br />

MII0_MDIO<br />

MII0_MDC<br />

MII0_RX_CLK<br />

MII0_RX_DV<br />

MII0_RXD0<br />

MII0_RXD1<br />

MII0_RXD2<br />

MII0_RXD3<br />

MII0_RX_CRS<br />

MII0_RX_COL<br />

MII0_TX_CLK<br />

MII0_TX_EN<br />

MII0_TXD0<br />

MII0_TXD1<br />

MII0_TXD2<br />

MII0_TXD3<br />

MII1_MDIO<br />

MII1_MDC<br />

MII1_RX_CLK<br />

MII1_RX_DV<br />

MII1_RXD0<br />

MII1_RXD1<br />

MII1_RXD2<br />

MII1_RXD3<br />

MII1_RX_CRS<br />

MII1_RX_COL<br />

MII1_TX_CLK<br />

MII1_TX_EN<br />

MII1_TXD0<br />

MII1_TXD1<br />

MII1_TXD2<br />

MII1_TXD3<br />

VCC3IO<br />

VCC3IO<br />

VCC3IO<br />

VCCK<br />

VCCK<br />

VCCK<br />

VCCK<br />

V18<br />

VCCAH<br />

P0_VCC33A<br />

P1_VCC33A<br />

P0_VCC18A<br />

P1_VCC18A<br />

P1_VCC18A<br />

P0_VCC18A<br />

P0_GND33A<br />

P1_GND33A<br />

P0_GND18A<br />

P0_GND18A<br />

P1_GND18A<br />

P1_GND18A<br />

GNDA<br />

GND<br />

GND<br />

GND<br />

GND<br />

E-PAD<br />

J1<br />

24<br />

22<br />

20<br />

18<br />

16<br />

14<br />

12<br />

10<br />

8<br />

6<br />

4<br />

2<br />

AX88742<br />

PCI I/F<br />

AX88742<br />

*<strong>Note</strong>3-8<br />

NC,HEADER 12X2<br />

23 GND<br />

21 MII1_RX_CRS<br />

19 MII1_RXD3<br />

17 MII1_RXD1<br />

15 MII1_RX_DV<br />

13<br />

11 MII1_TX_CLK<br />

9 MII1_TXD0<br />

7 MII1_TXD2<br />

5 MII1_MDC<br />

3 GND<br />

1 GND<br />

AD0<br />

AD1<br />

AD2<br />

AD3<br />

AD4<br />

AD5<br />

AD6<br />

AD7<br />

AD8<br />

AD9<br />

AD10<br />

AD11<br />

AD12<br />

AD13<br />

AD14<br />

AD15<br />

AD16<br />

AD17<br />

AD18<br />

AD19<br />

AD20<br />

AD21<br />

AD22<br />

AD23<br />

AD24<br />

AD25<br />

AD26<br />

AD27<br />

AD28<br />

AD29<br />

AD30<br />

AD31<br />

6<br />

7<br />

8<br />

9<br />

10<br />

11<br />

14<br />

MII1_TXD3<br />

MII1_TXD2<br />

MII1_TXD1<br />

MII1_TXD0<br />

MII1_TX_EN<br />

MII1_TX_CLK<br />

MII1_RX_CLK<br />

MII1_RXD3<br />

MII1_RXD2<br />

MII1_RXD1<br />

MII1_RXD0<br />

MII1_RX_DV<br />

MII1_RX_CLK<br />

MII1_TX_CLK<br />

RST_N 28<br />

MODE2<br />

MODE1<br />

MODE0<br />

NC<br />

NC<br />

AD0<br />

AD1<br />

AD2<br />

AD3<br />

AD4<br />

AD5<br />

AD6<br />

AD7<br />

AD8<br />

AD9<br />

AD10<br />

AD11<br />

AD12<br />

AD13<br />

AD14<br />

AD15<br />

AD16<br />

AD17<br />

AD18<br />

AD19<br />

AD20<br />

AD21<br />

AD22<br />

AD23<br />

AD24<br />

AD25<br />

AD26<br />

AD27<br />

AD28<br />

AD29<br />

AD30<br />

AD31<br />

FRAME#<br />

IRDY#<br />

PCI_CLK<br />

RESETN<br />

PERR#<br />

SERR#<br />

PAR<br />

IDSEL<br />

C/BE0#<br />

C/BE1#<br />

C/BE2#<br />

C/BE3#<br />

INT<br />

ISOLATE<br />

PME<br />

GNT#<br />

REQ#<br />

TRDY#<br />

DEVSEL#<br />

STOP#<br />

EECS<br />

EESK<br />

EEDIO<br />

MODE2<br />

MODE1<br />

MODE0<br />

J1 HEADER Table MII1 Interface<br />

AX88742 J1<br />

Reverse<br />

PIN PIN MII Mode MII Mode RMII Mode<br />

GNT<br />

119<br />

117<br />

116<br />

115<br />

114<br />

104<br />

103<br />

102<br />

90<br />

89<br />

88<br />

86<br />

85<br />

81<br />

80<br />

79<br />

77<br />

76<br />

75<br />

74<br />

73<br />

69<br />

68<br />

67<br />

63<br />

62<br />

58<br />

57<br />

56<br />

52<br />

51<br />

50<br />

FRAME 83<br />

IRDY 84<br />

PCI_CLK 124<br />

PERR 98<br />

SERR 99<br />

PAR 109<br />

IDSEL<br />

CBE0<br />

CBE1<br />

CBE2<br />

CBE3<br />

INT<br />

66<br />

111<br />

110<br />

82<br />

64<br />

61<br />

ISOLATE 60<br />

PME 59<br />

55<br />

REQ 54<br />

TRDY 93<br />

DEVSEL<br />

94<br />

STOP 95<br />

CS 127<br />

SK 125<br />

DIO 126<br />

41<br />

40<br />

39<br />

MII1_TXD1<br />

MII1_TXD0<br />

MII1_TX_EN<br />

MII1_REFCLKO<br />

MII1_REFCLK<br />

R38<br />

4.7K<br />

VCC5P<br />

VCC33<br />

*<strong>Note</strong>3-7<br />

Reverse<br />

RMII Mode<br />

NC<br />

NC<br />

R43<br />

6.8K<br />

R42<br />

15K<br />

MII1_RXD1<br />

MII1_RXD0<br />

MII1_CRSDV<br />

R41<br />

4.7K<br />

R37<br />

4.7K<br />

MII1_REFCLKO<br />

MII1_REFCLK<br />

*<strong>Note</strong>3-1:<br />

The 1M feedback resis<strong>to</strong>r is necessary for 25MHz<br />

crystal circuit. The <strong>refer</strong>ence 25MHz crystal<br />

is the NSK HC-49/U-S 25MHz crystal with<br />

CL 20pF and ESR max. 40 Ohm.<br />

*<strong>Note</strong>3-2:<br />

The P0_RSET_BG and P1_RSET_BG pins must be cocnnected<br />

<strong>to</strong> GND through a 12.1K ohm +/- 1% resiter.<br />

*<strong>Note</strong>3-3:<br />

This 50MHz Reference Clock Circuit is optional<br />

for AX88742 RMII/Reverse-RMII Modes. <strong>Please</strong> <strong>refer</strong> <strong>to</strong><br />

Section 4.3 of AX88742 datasheet for more details.<br />

*<strong>Note</strong>3-4:<br />

The pin #46 should be pulled high via a resister<br />

when the 3.3V PCI Aux. Power exists. <strong>Please</strong> <strong>refer</strong> <strong>to</strong><br />

Section 2.2.6 of AX88742 datasheet for more details.<br />

*<strong>Note</strong>3-5:<br />

The (C29, C30) and (C31, C33) capaci<strong>to</strong>rs should be<br />

as close as AX88742 pin #26 and #27 respectively.<br />

*<strong>Note</strong>3-6:<br />

(1) Enable the AX88742 on-chip 3.3V <strong>to</strong> 1.8V regula<strong>to</strong>r:<br />

Unmount the R44 resis<strong>to</strong>r and mount the L1 or L4 F.B.<br />

based on the 3.3V power source is from the U5 VCC33<br />

or from the U6 VCC33-18.<br />

(2) Disable the AX88742 on-chip 3.3V <strong>to</strong> 1.8V regula<strong>to</strong>r:<br />

Mount the R44 resis<strong>to</strong>r and unmount the L1 and L4 F.B.<br />

(This is the default circuit for AX88742 demo board)<br />

*<strong>Note</strong>3-7:<br />

The AX88742 should be configured <strong>to</strong> the PCI interface<br />

mode. (Pull high the MODE2 signal and pull down the<br />

MODE1 and MODE0 signals.)<br />

*<strong>Note</strong>3-8:<br />

The pin pitch of the J1, J2 headers is 2.54mm.<br />

*<strong>Note</strong>3-9:<br />

The AX88742 pin #123 needs <strong>to</strong> be pulled down through a<br />

4.7K Ohm resis<strong>to</strong>r when the AX88742 <strong>Port</strong> 0 was set <strong>to</strong><br />

MII or Reverse MII mode. <strong>Please</strong> <strong>refer</strong> <strong>to</strong> Section 2.1.2<br />

and 2.1.3 of AX88742 datasheet for more details.<br />

This block circuit was not implemented on AX88742 PCB<br />

V2.0 demo board.<br />

This pin should be manually pulled down when the AX88742<br />

<strong>Port</strong> 0 was set <strong>to</strong> MII or Reverse MII mode.<br />

D<br />

C<br />

B<br />

71<br />

15 MII0_RX_DV MII0_TX_EN<br />

MII0_CRSDV<br />

MII0_TX_EN<br />

34<br />

15 MII1_RX_DV MII1_TX_EN<br />

MII1_CRSDV<br />

MII1_TX_EN<br />

A<br />

91<br />

16 MII0_RXD0 MII0_TXD0<br />

MII0_RXD0<br />

MII0_TXD0<br />

35<br />

16 MII1_RXD0 MII1_TXD0<br />

MII1_RXD0<br />

MII1_TXD0<br />

A<br />

92<br />

17 MII0_RXD1 MII0_TXD1<br />

MII0_RXD1<br />

MII0_TXD1<br />

36<br />

17 MII1_RXD1 MII1_TXD1<br />

MII1_RXD1<br />

MII1_TXD1<br />

96<br />

18 MII0_RXD2 MII0_TXD2 NC<br />

NC<br />

37<br />

18 MII1_RXD2 MII1_TXD2 NC<br />

NC<br />

97<br />

19 MII0_RXD3 MII0_TXD3 NC<br />

NC<br />

38<br />

19 MII1_RXD3 MII1_TXD3 NC<br />

NC<br />

101<br />

20<br />

MII0_RX_COL<br />

NC<br />

NC<br />

NC<br />

33<br />

20<br />

MII1_RX_COL<br />

NC<br />

NC<br />

NC<br />

8<br />

100<br />

107<br />

108<br />

4<br />

5<br />

7<br />

21<br />

MII0_RX_CRS<br />

MII0_CRS<br />

MII0_MDIO MII0_MDIO MII0_MDIO MII0_MDIO<br />

MII0_MDC MII0_MDC MII0_MDC MII0_MDC<br />

NC<br />

6<br />

NC<br />

32<br />

29<br />

30<br />

5<br />

21<br />

4<br />

5<br />

MII1_RX_CRS<br />

MII1_CRS<br />

MII1_MDIO MII1_MDIO MII1_MDIO MII1_MDIO<br />

MII1_MDC MII1_MDC MII1_MDC MII1_MDC<br />

4<br />

NC<br />

NC<br />

3<br />

2<br />

Title<br />

<strong>ASIX</strong> ELECTRONICS CORPORATION<br />

AX88742-MII I/F<br />

Size Document Number Rev<br />

C<br />

1.40<br />

AX88742_PCBV2.0<br />

Sunday, April 04, 2010<br />

Date: Sheet of<br />

3 6<br />

1

8<br />

7<br />

6<br />

5<br />

4<br />

3<br />

2<br />

1<br />

D<br />

P3<br />

P3<br />

P3<br />

P3<br />

P3<br />

P3<br />

P3<br />

P3<br />

P3<br />

P3<br />

P3<br />

P3<br />

P3<br />

P3<br />

MII0_TXD0<br />

MII0_TXD1<br />

MII0_TXD2<br />

MII1_TXD0<br />

MII1_TXD1<br />

MII1_TXD2<br />

P0_RXIN<br />

P0_RXIP<br />

P0_TXON<br />

P0_TXOP<br />

P1_RXIN<br />

P1_RXIP<br />

P1_TXON<br />

P1_TXOP<br />

MII0_TXD0<br />

MII0_TXD1<br />

MII0_TXD2<br />

MII1_TXD0<br />

MII1_TXD1<br />

MII1_TXD2<br />

P0_RXIN<br />

P0_RXIP<br />

P0_TXON<br />

P0_TXOP<br />

P1_RXIN<br />

P1_RXIP<br />

P1_TXON<br />

P1_TXOP<br />

PHY <strong>Port</strong> 0 RJ-45 Connec<strong>to</strong>r + Tranformer<br />

(Turns Ratio 1CT:1CT, with au<strong>to</strong>-MDIX) *<strong>Note</strong>4-2<br />

P0_RXIN<br />

P0_RXIP<br />

P0_TXON<br />

P0_TXOP<br />

C3<br />

0.1uF<br />

C5<br />

0.1uF<br />

VCC33A<br />

C2<br />

1uF<br />

R5<br />

49.9<br />

R4<br />

49.9<br />

C1<br />

R6<br />

49.9<br />

R3<br />

49.9<br />

U7<br />

8<br />

7 CHS<br />

6 NC<br />

5 RD-<br />

4 CT<br />

3 CT<br />

2 RD+<br />

1 TD-<br />

TD+<br />

12<br />

LED1 LED2<br />

10 11<br />

LED1 LED2<br />

9<br />

R31<br />

R28 0<br />

MII0_TXD2<br />

MII0_TXD0<br />

R26 0<br />

R29<br />

1K<br />

YL2J201A<br />

1K<br />

VCC33<br />

PHY <strong>Port</strong> 1 RJ-45 Connec<strong>to</strong>r + Tranformer<br />

(Turns Ratio 1CT:1CT, with au<strong>to</strong>-MDIX) *<strong>Note</strong>4-2<br />

P1_RXIN<br />

P1_RXIP<br />

P1_TXON<br />

P1_TXOP<br />

C19<br />

0.1uF<br />

C22<br />

0.1uF<br />

VCC33A<br />

C21<br />

1uF<br />

R22<br />

49.9<br />

R19<br />

49.9<br />

C15<br />

R21<br />

49.9<br />

R20<br />

49.9<br />

U8<br />

8<br />

7 CHS<br />

6 NC<br />

5 RD-<br />

4 CT<br />

3 CT<br />

2 RD+<br />

1 TD-<br />

TD+<br />

12<br />

LED1 LED2<br />

10 11<br />

LED1 LED2<br />

9<br />

R36<br />

R34<br />

1K<br />

R15 0<br />

R18 0<br />

1K<br />

MII1_TXD2<br />

YL2J201A<br />

MII1_TXD0<br />

VCC33<br />

D<br />

C<br />

P3,5<br />

P3,5<br />

P2,3,5<br />

VCC33<br />

VCC33A<br />

GND<br />

VCC33<br />

VCC33A<br />

GND<br />

*<strong>Note</strong>4-1<br />

0.1uF<br />

*<strong>Note</strong>4-1<br />

0.1uF<br />

C<br />

MII0_TXD1<br />

R27 0<br />

D2 C<br />

A<br />

LED,O<br />

R30<br />

1K<br />

VCC33<br />

MII1_TXD1<br />

R16 0<br />

D5<br />

C<br />

A<br />

LED,O<br />

R35<br />

1K<br />

VCC33<br />

*<strong>Note</strong>4-3<br />

*<strong>Note</strong>4-3<br />

B<br />

*<strong>Note</strong>4-1:<br />

The TXCT and RXCT pins of the magnetic with Au<strong>to</strong>-MDIX<br />

function should already be connected <strong>to</strong>gether inside.<br />

The TXCT and RXCT pins of the magnetic without Au<strong>to</strong>-MDIX<br />

function should be separate, these two pins should be<br />

short <strong>to</strong>gether on your schematic.<br />

*<strong>Note</strong>4-3:<br />

The AX88742 PHY <strong>Port</strong> 0/<strong>Port</strong> 1 LED display modes can be set<br />

by the AX88742 LED Control Register (LCR, address 0x0DC).<br />

<strong>Please</strong> <strong>refer</strong> <strong>to</strong> Section 5.2.18 of AX88742 datasheet for<br />

more details.<br />

B<br />

*<strong>Note</strong>4-2:<br />

The <strong>refer</strong>ence transformer of AX88742 demo board is<br />

YL2J201 Single RJ-45 Connec<strong>to</strong>r Module with<br />

Integrated 10/100 Base-TX Magnetics<br />

(Turns Ratio is 1CT:1CT with Au<strong>to</strong>-MDIX).<br />

Reference Transformer Part No. list<br />

YL2J201A<br />

YuTai Electronics Co.,LTD<br />

TEL:86-574-63620701,63621610<br />

http;//www.yutai-elec.com<br />

EMAIL:nico_yu@yeah.net<br />

A<br />

A<br />

8<br />

7<br />

6<br />

5<br />

4<br />

3<br />

Title<br />

<strong>ASIX</strong> ELECTRONICS CORPORATION<br />

RJ45-LED<br />

Size Document Number Rev<br />

B<br />

AX88742_PCBV2.0<br />

Date: Sunday, April 04, 2010<br />

Sheet 4 of<br />

6<br />

2<br />

1<br />

1.40

8<br />

7<br />

6<br />

5<br />

4<br />

3<br />

2<br />

1<br />

D<br />

P3 EECS<br />

P3 EESK<br />

P3 EEDIO<br />

P2 VCC5P<br />

P2 3.3VAUX<br />

P2 VCC33P<br />

P3 VCC33-18<br />

P3,4 VCC33<br />

P3,4 VCC33A<br />

P3 VCC18<br />

P3 VCC18A<br />

P2,3,4 GND<br />

EECS<br />

EESK<br />

EEDIO<br />

VCC5P<br />

3.3VAUX<br />

VCC33P<br />

VCC33-18<br />

VCC33<br />

VCC33A<br />

VCC18<br />

VCC18A<br />

GND<br />

Power circuit and by-pass capaci<strong>to</strong>rs<br />

3.3VAUX<br />

VCC5P<br />

VCC33<br />

C12<br />

10uF<br />

C14<br />

0.1uF<br />

C13<br />

10uF<br />

C16<br />

0.1uF<br />

C17<br />

10uF<br />

*<strong>Note</strong>5-1<br />

C18<br />

0.1uF<br />

*<strong>Note</strong>5-2<br />

J4 HEADER 3<br />

1<br />

2<br />

3<br />

VCC33P<br />

1<br />

2<br />

3<br />

4<br />

5V <strong>to</strong> 3.3V<br />

Voltage Regula<strong>to</strong>r<br />

VCC33<br />

C9<br />

U5<br />

NC<br />

VIN<br />

VOUT<br />

VAUX<br />

SI91861<br />

GND 8<br />

GND 7<br />

GND 6<br />

GND 5<br />

C34<br />

C46<br />

C48<br />

Optional<br />

VCC5P<br />

VCC33-18<br />

3.3VAUX<br />

C62<br />

NC,1uF<br />

*<strong>Note</strong>5-3<br />

C39<br />

L2<br />

C60<br />

NC,10uF<br />

PBY160808T-110Y-S<br />

100MHz/11ohm<br />

C37<br />

C61<br />

NC,0.1uF<br />

C42<br />

1<br />

2<br />

3<br />

4<br />

C59<br />

NC,10uF<br />

U6<br />

NC<br />

VIN<br />

VOUT<br />

VAUX<br />

NC,SI91861<br />

5V <strong>to</strong> 3.3V<br />

Voltage Regula<strong>to</strong>r<br />

VCC33A<br />

C41<br />

GND 8<br />

GND 7<br />

GND 6<br />

GND 5<br />

*<strong>Note</strong>5-1:<br />

All power pin should be implemented with by-pass<br />

capaci<strong>to</strong>r, and the by-pass capaci<strong>to</strong>r should be as close<br />

as the power pin. The analog powers and digital powers<br />

should be isolated with a Ferrite Bead.<br />

*<strong>Note</strong>5-2:<br />

This is the VCC33 power source selection jumper.<br />

J4 Pin #1 & #2 short: VCC33 comes from the U5 (Default)<br />

J4 Pin #2 & #3 short: VCC33 comes from the PCI 3.3V<br />

*<strong>Note</strong>5-3:<br />

The SI91861 is a 400mA Current Linear Regula<strong>to</strong>r.<br />

The 5V <strong>to</strong> 3.3V Voltage Regula<strong>to</strong>r circuit is optional<br />

for extra power supply.<br />

D<br />

C<br />

External 3.3V <strong>to</strong> 1.8V Voltage Regula<strong>to</strong>r<br />

VCC33-18<br />

VCC33<br />

R46<br />

*<strong>Note</strong>5-5<br />

NC,0,0805<br />

R45 0,0805<br />

C10<br />

0.1uF<br />

C11<br />

22uF<br />

3<br />

U3<br />

Vi<br />

RT9164A<br />

Vo<br />

ADJ<br />

3.3V <strong>to</strong> 1.8V<br />

Voltage Regula<strong>to</strong>r<br />

*<strong>Note</strong>5-4<br />

2<br />

1<br />

R12<br />

220 1%<br />

R11<br />

100 1%<br />

C8<br />

22uF<br />

22uF<br />

VCC18<br />

C47<br />

0.1uF<br />

0.1uF<br />

C45<br />

0.1uF<br />

0.1uF<br />

C49<br />

0.1uF<br />

0.1uF<br />

L3<br />

0.1uF<br />

PBY160808T-110Y-S<br />

100MHz/11ohm<br />

C44<br />

C38<br />

0.1uF<br />

10uF<br />

10uF<br />

C36<br />

0.1uF<br />

0.1uF<br />

C35<br />

0.1uF<br />

0.1uF<br />

C43<br />

0.1uF<br />

VCC18A<br />

C40<br />

0.1uF<br />

*<strong>Note</strong>5-4:<br />

The external 3.3V <strong>to</strong> 1.8V Voltage Regula<strong>to</strong>r circuit can<br />

be removed if the AX88742 build-in 3.3V <strong>to</strong> 1.8V Voltage<br />

Regula<strong>to</strong>r is enabled.<br />

<strong>Please</strong> <strong>refer</strong> <strong>to</strong> <strong>Note</strong>3-6 of Page 3 for more details.<br />

*<strong>Note</strong>5-5:<br />

(1) Get U3 3.3V voltage input from U5 VCC33:<br />

-- mount R45 and unmount R46. (Default)<br />

(2) Get U3 3.3V voltage input from U6 VCC33-18:<br />

-- mount R46 and unmount R45.<br />

C<br />

EEPROM<br />

*<strong>Note</strong>5-6<br />

*<strong>Note</strong>5-6:<br />

The AX88742 supports 8-bit mode EEPROM only.<br />

You can select the 93C46/93C56/93C66 EEPROM<br />

by setting the EESK and EECS signals level.<br />

VCC33<br />

R8<br />

4.7K<br />

VCC33<br />

R7<br />

4.7K<br />

VCC33<br />

R9 4.7K<br />

EECS<br />

EESK<br />

EEDIO<br />

1<br />

2<br />

3<br />

4<br />

U2<br />

CS<br />

SK<br />

DI<br />

DO<br />

VCC 8<br />

NC 7<br />

ORG 6<br />

GND 5<br />

VCC33<br />

C4<br />

0.1uF<br />

EESK<br />

EECS<br />

AT93C66A<br />

SOIC-8P<br />

B<br />

EEPROM Model Setting:<br />

(High:Pull-High, Low:Pull-Low)<br />

TYPE SIZE EESK EECS<br />

N/A (Default) - Low Low<br />

93C46 1K Low High<br />

93C56 2K High Low<br />

93C66 4K High High<br />

EECS<br />

EESK<br />

EEDIO<br />

U1<br />

CS<br />

SK<br />

DI<br />

DO<br />

NC,AT93C66A<br />

DIP-8P<br />

Optional<br />

1<br />

2<br />

3<br />

4<br />

VCC 8<br />

NC 7<br />

ORG 6<br />

GND 5<br />

VCC33<br />

GND<br />

R10<br />

4.7K<br />

B<br />

A<br />

A<br />

8<br />

7<br />

6<br />

5<br />

4<br />

3<br />

2<br />

Title<br />

<strong>ASIX</strong> ELECTRONICS CORPORATION<br />

POWER / EEPROM<br />

Size Document Number Rev<br />

C<br />

1.40<br />

AX88742_PCBV2.0<br />

Sunday, April 04, 2010<br />

Date: Sheet of<br />

5 6<br />

1

8<br />

7<br />

6<br />

5<br />

4<br />

3<br />

2<br />

1<br />

D<br />

Revision His<strong>to</strong>ry<br />

Revision Date Comment<br />

V0.1 2007/09/28 Initial release.<br />

V1.00 2008/02/20 AX88742 DEMO BOARD PCB V2.0<br />

D<br />

V1.10 2008/03/03 R43 Change <strong>to</strong> 6.8 K ohm.<br />

V1.20 2008/03/04 Add the E-PAD related circuit<br />

(i.e. connect the E-PAD <strong>to</strong> GND.)<br />

C<br />

V1.30 2009/03/12 The U1 AX88742 pin name change:<br />

Pin10 P0_VCC18D was changed <strong>to</strong> P0_VCC18A<br />

Pin15 P1_VCC18D was changed <strong>to</strong> P1_VCC18A<br />

Pin13 P0_GND18D was changed <strong>to</strong> P0_GND18A<br />

Pin14 P1_GND18D was changed <strong>to</strong> P1_GND18A<br />

Pin 10,15 Net "VCC18" was changed <strong>to</strong> "VCC18A"<br />

C35,C36 Net "VCC18" was changed <strong>to</strong> "VCC18A"<br />

C<br />

V1.40 2009/05/08 1. Add R47 in Page 3.<br />

2. Add *<strong>Note</strong>3-9 in Page 3.<br />

B<br />

B<br />

A<br />

8<br />

7<br />

6<br />

5<br />

4<br />

Title<br />

<strong>ASIX</strong> ELECTRONICS CORPORATION<br />

Revision His<strong>to</strong>ry<br />

Size Document Number Rev<br />

A<br />

AX88742_PCBV2.0<br />

Date: Sunday, April 04, 2010<br />

Sheet 6 of<br />

6<br />

3<br />

2<br />

1<br />

1.40<br />

A

![P-CAD EDA - [Sheet1]](https://img.yumpu.com/49470492/1/190x115/p-cad-eda-sheet1.jpg?quality=85)