Open PDF

Open PDF

Open PDF

Create successful ePaper yourself

Turn your PDF publications into a flip-book with our unique Google optimized e-Paper software.

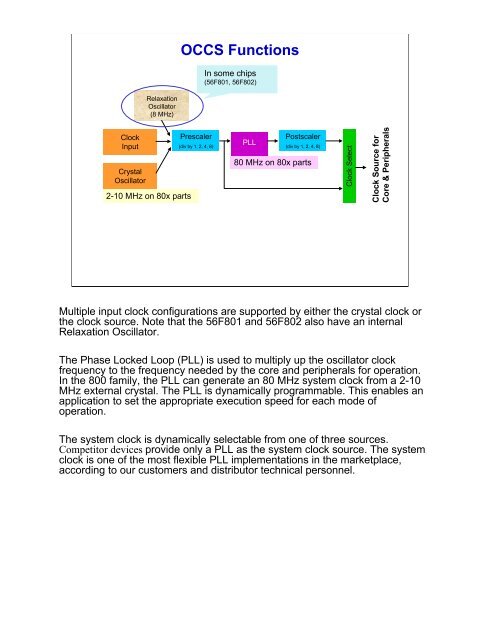

OCCS Functions<br />

In some chips<br />

(56F801, 56F802)<br />

Relaxation<br />

Oscillator<br />

(8 MHz)<br />

Clock<br />

Input<br />

Crystal<br />

Oscillator<br />

2-10 MHz on 80x parts<br />

Prescaler<br />

(div by 1, 2, 4, 8)<br />

PLL<br />

Postscaler<br />

(div by 1, 2, 4, 8)<br />

80 MHz on 80x parts<br />

Clock Select<br />

Clock Source for<br />

Core & Peripherals<br />

Multiple input clock configurations are supported by either the crystal clock or<br />

the clock source. Note that the 56F801 and 56F802 also have an internal<br />

Relaxation Oscillator.<br />

The Phase Locked Loop (PLL) is used to multiply up the oscillator clock<br />

frequency to the frequency needed by the core and peripherals for operation.<br />

In the 800 family, the PLL can generate an 80 MHz system clock from a 2-10<br />

MHz external crystal. The PLL is dynamically programmable. This enables an<br />

application to set the appropriate execution speed for each mode of<br />

operation.<br />

The system clock is dynamically selectable from one of three sources.<br />

Competitor devices provide only a PLL as the system clock source. The system<br />

clock is one of the most flexible PLL implementations in the marketplace,<br />

according to our customers and distributor technical personnel.