Open PDF

Open PDF

Open PDF

Create successful ePaper yourself

Turn your PDF publications into a flip-book with our unique Google optimized e-Paper software.

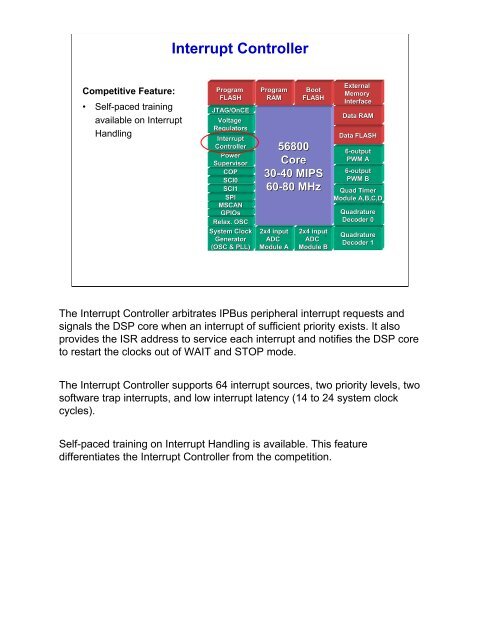

Interrupt Controller<br />

Competitive Feature:<br />

• Self-paced training<br />

available on Interrupt<br />

Handling<br />

Program<br />

FLASH<br />

JTAG/OnCE<br />

Voltage<br />

Regulators<br />

Interrupt<br />

Controller<br />

Power<br />

Supervisor<br />

COP<br />

SCI0<br />

SCI1<br />

SPI<br />

MSCAN<br />

GPIOs<br />

Relax. OSC<br />

System Clock<br />

Generator<br />

(OSC & PLL)<br />

Program<br />

Boot<br />

RAM<br />

FLASH<br />

56800<br />

Core<br />

30-40 MIPS<br />

60-80 MHz<br />

2x4 input<br />

2x4 input<br />

ADC<br />

ADC<br />

Module A<br />

Module B<br />

External<br />

Memory<br />

Interface<br />

Data RAM<br />

Data FLASH<br />

6-output<br />

PWM A<br />

6-output<br />

PWM B<br />

Quad Timer<br />

Module A,B,C,D<br />

Quadrature<br />

Decoder 0<br />

Quadrature<br />

Decoder 1<br />

The Interrupt Controller arbitrates IPBus peripheral interrupt requests and<br />

signals the DSP core when an interrupt of sufficient priority exists. It also<br />

provides the ISR address to service each interrupt and notifies the DSP core<br />

to restart the clocks out of WAIT and STOP mode.<br />

The Interrupt Controller supports 64 interrupt sources, two priority levels, two<br />

software trap interrupts, and low interrupt latency (14 to 24 system clock<br />

cycles).<br />

Self-paced training on Interrupt Handling is available. This feature<br />

differentiates the Interrupt Controller from the competition.