Open PDF

Open PDF

Open PDF

You also want an ePaper? Increase the reach of your titles

YUMPU automatically turns print PDFs into web optimized ePapers that Google loves.

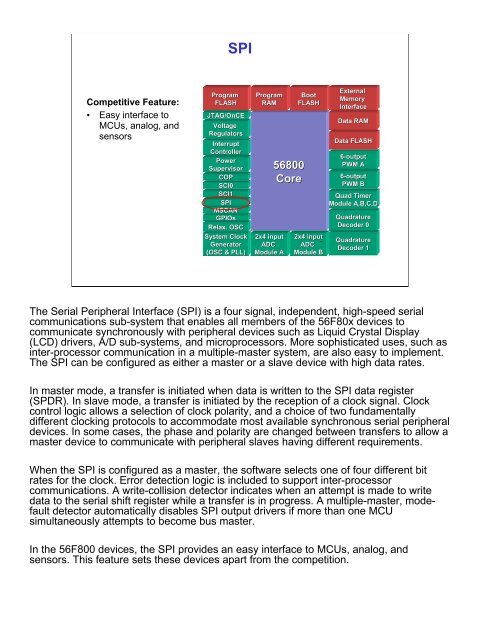

SPI<br />

Competitive Feature:<br />

• Easy interface to<br />

MCUs, analog, and<br />

sensors<br />

Program<br />

FLASH<br />

JTAG/OnCE<br />

Voltage<br />

Regulators<br />

Interrupt<br />

Controller<br />

Power<br />

Supervisor<br />

COP<br />

SCI0<br />

SCI1<br />

SPI<br />

MSCAN<br />

GPIOs<br />

Relax. OSC<br />

System Clock<br />

Generator<br />

(OSC & PLL)<br />

Program<br />

Boot<br />

RAM<br />

FLASH<br />

56800<br />

Core<br />

2x4 input<br />

2x4 input<br />

ADC<br />

ADC<br />

Module A<br />

Module B<br />

External<br />

Memory<br />

Interface<br />

Data RAM<br />

Data FLASH<br />

6-output<br />

PWM A<br />

6-output<br />

PWM B<br />

Quad Timer<br />

Module A,B,C,D<br />

Quadrature<br />

Decoder 0<br />

Quadrature<br />

Decoder 1<br />

The Serial Peripheral Interface (SPI) is a four signal, independent, high-speed serial<br />

communications sub-system that enables all members of the 56F80x devices to<br />

communicate synchronously with peripheral devices such as Liquid Crystal Display<br />

(LCD) drivers, A/D sub-systems, and microprocessors. More sophisticated uses, such as<br />

inter-processor communication in a multiple-master system, are also easy to implement.<br />

The SPI can be configured as either a master or a slave device with high data rates.<br />

In master mode, a transfer is initiated when data is written to the SPI data register<br />

(SPDR). In slave mode, a transfer is initiated by the reception of a clock signal. Clock<br />

control logic allows a selection of clock polarity, and a choice of two fundamentally<br />

different clocking protocols to accommodate most available synchronous serial peripheral<br />

devices. In some cases, the phase and polarity are changed between transfers to allow a<br />

master device to communicate with peripheral slaves having different requirements.<br />

When the SPI is configured as a master, the software selects one of four different bit<br />

rates for the clock. Error detection logic is included to support inter-processor<br />

communications. A write-collision detector indicates when an attempt is made to write<br />

data to the serial shift register while a transfer is in progress. A multiple-master, modefault<br />

detector automatically disables SPI output drivers if more than one MCU<br />

simultaneously attempts to become bus master.<br />

In the 56F800 devices, the SPI provides an easy interface to MCUs, analog, and<br />

sensors. This feature sets these devices apart from the competition.