V54C3128(16/80/40)4VC 128Mbit SDRAM 3.3 VOLT, TSOP II / BGA ...

V54C3128(16/80/40)4VC 128Mbit SDRAM 3.3 VOLT, TSOP II / BGA ...

V54C3128(16/80/40)4VC 128Mbit SDRAM 3.3 VOLT, TSOP II / BGA ...

Create successful ePaper yourself

Turn your PDF publications into a flip-book with our unique Google optimized e-Paper software.

ProMOS TECHNOLOGIES<br />

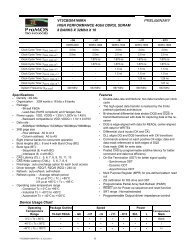

<strong>V54C3128</strong>(<strong>16</strong>/<strong>80</strong>/<strong>40</strong>)<strong>4VC</strong><br />

Limit Values<br />

-5 -6 -7PC -7 -10<br />

# Symbol Parameter<br />

Min. Max. Min. Max. Min. Max. Min. Max. Min. Max.<br />

Unit<br />

Note<br />

Read Cycle<br />

23 t OH Data Out Hold Time 2 – 2.5 – 2.5 – 2.5 – 2.5 – ns 2<br />

24 t LZ Data Out to Low Impedance Time 1 – 1 – 1 – 1 – 1 – ns<br />

25 t HZ Data Out to High Impedance Time<br />

CAS Latency = 3<br />

CAS Latency = 2<br />

–<br />

_<br />

4.5<br />

4.5<br />

–<br />

_<br />

5.4<br />

5.4<br />

–<br />

_<br />

5.4<br />

5.4<br />

–<br />

_<br />

5.4<br />

5.4<br />

–<br />

_<br />

6<br />

6<br />

ns<br />

ns<br />

7<br />

26 t DQZ DQM Data Out Disable Latency – 2 – 2 – 2 – 2 – 2 CLK<br />

Write Cycle<br />

27 t WR Write Recovery Time 2 – 2 – 2 – 2 – 2 – CLK<br />

28 t DAL Last data in to Active command 2*CLK<br />

+t RP<br />

– 2*CLK<br />

+t RP<br />

– 2*CLK<br />

+t RP<br />

– 2*CLK<br />

+t RP<br />

– 2*CLK<br />

+t RP<br />

– ns<br />

Notes for AC Parameters:<br />

1. For proper power-up see the operation section of this data sheet.<br />

2. AC timing tests have V IL = 0.8V and V IH = 2.0V with the timing referenced to the 1.4 V crossover point. The transition<br />

time is measured between V IH and V IL . All AC measurements assume t T = 1ns with the AC output load circuit shown<br />

in Figure 1.<br />

CLK<br />

VIH<br />

VIL<br />

+ 1.4 V<br />

tIS<br />

tIH<br />

COMMAND<br />

1.4V<br />

Z=50 Ohm<br />

tAC<br />

tLZ<br />

tAC<br />

tOH<br />

t T<br />

Figure 1.<br />

50 Ohm<br />

I/O<br />

50 pF<br />

OUTPUT<br />

1.4V<br />

tHZ<br />

4. If 1.2ns < t T < t CK /2, a time (t T /2 – 0.5)ns has to be added to this parameter. t T = CLK t T .<br />

5. If 1.2ns < t T < t CK /2, a time (t T – 1)ns has to be added to this parameter. t T = (CLK t T + Command t T ) / 2.<br />

6. These parameter account for the number of clock cycle and depend on the operating frequency of the clock, as<br />

follows:<br />

the number of clock cycle = specified value of timing period (counted in fractions as a whole number)<br />

Self Refresh Exit is a synchronous operation and begins on the 2nd positive clock edge after CKE returns high.<br />

Self Refresh Exit is not complete until a time period equal to tRC is satisfied once the Self Refresh Exit command<br />

is registered.<br />

7. Referenced to the time which the output achieves the open circuit condition, not to output voltage levels.<br />

<strong>V54C3128</strong>(<strong>16</strong>/<strong>80</strong>/<strong>40</strong>)<strong>4VC</strong> Rev. 1.3 November 2008<br />

19