Chip Scale Review - July 2007

Chip Scale Review - July 2007

Chip Scale Review - July 2007

You also want an ePaper? Increase the reach of your titles

YUMPU automatically turns print PDFs into web optimized ePapers that Google loves.

<strong>Chip</strong><strong>Scale</strong><br />

www.<strong>Chip</strong><strong>Scale</strong><strong>Review</strong>.com<br />

®<br />

r e v i e w<br />

<strong>July</strong> <strong>2007</strong><br />

• Lead-Free One Year After<br />

• Wafer Bumping

See us at SEMICON West, Booth #7358

CONTENTS<br />

The International Magazine of <strong>Chip</strong>-<strong>Scale</strong><br />

Electronics, Flip-<strong>Chip</strong> Technology, Optoelectronics<br />

Interconnection and Wafer-Level Packaging<br />

<strong>July</strong> <strong>2007</strong><br />

Volume 11, Number 5<br />

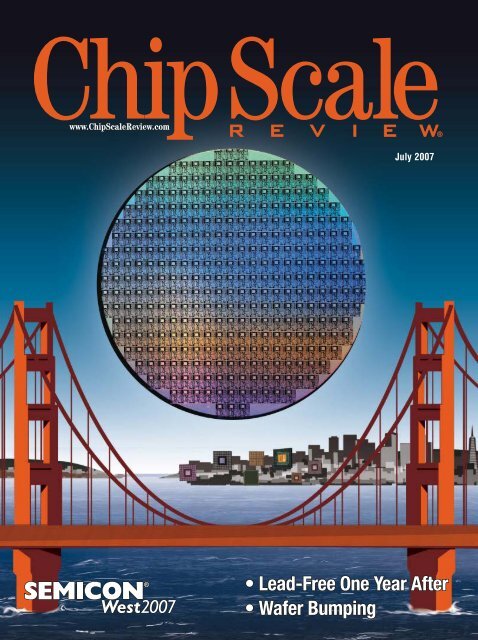

THE COVER<br />

It’s time again for your humble cover scribe to apply<br />

his flying fingers to the keyboard and tell you about our<br />

magnificent <strong>July</strong> issue. By now, you have correctly identified<br />

the Golden Gate Bridge on our cover, (opened in 1937),<br />

which has become an icon for San Francisco, current home<br />

of SEMICON West. At the time, it was painted with a red<br />

lead primer and a lead-based topcoat. Far ahead of RoHS,<br />

the bridge scraped the lead off in 1965 and applied a zinc<br />

silicate primer and an acrylic topcoat of Sherwin Williams’<br />

“International Orange.” The bridge’s conversion from lead<br />

to lead-free provides an outstanding segue into mention of<br />

the article by my favorite editor, Ron Iscoff. I just peeked at<br />

his article that looks at RoHS one year after. You don’t want<br />

to miss it! If you don’t know what RoHS is by this time,<br />

please confine your reading in future to Sports Illustrated<br />

or Playboy! Is RoHS merely an exercise in futility by a<br />

bunch of silly, frustrated Europeans with nothing better to<br />

do than munch on their braunschweigers and pate de fois<br />

gras, while hoisting a Heineken? La plume de ma tante—I<br />

don’t know! But I am pleased to refer you to Terry<br />

Thompson’s article and column. Terry is our senior editor<br />

and our “go-to” guy for MEMS. Don’t miss “MEMS the<br />

Word!” or his article on wafer-bumping tools and services.<br />

There is so much good stuff in this issue to tell you about,<br />

and so little space, that I’m beside myself with angst!<br />

See you at SEMICON West!<br />

(Illustration for <strong>Chip</strong> <strong>Scale</strong> <strong>Review</strong> by<br />

Design 2 Market) [design2marketinc.com]<br />

<strong>Chip</strong> <strong>Scale</strong> <strong>Review</strong>, at 7291 Coronado Dr., Suite 8, San Jose, CA 95129<br />

(ISSN 1526-1344), is published eight times a year, with issues in<br />

January-February, March, April, May-June, <strong>July</strong>, August-September,<br />

October and November-December.<br />

Periodical postage paid at San Jose, Calif., and additional offices.<br />

POSTMASTER: Send address changes to <strong>Chip</strong> <strong>Scale</strong> <strong>Review</strong> magazine,<br />

7291 Coronado Dr., Suite 8, San Jose, CA 95129.<br />

COVER FEATURES<br />

RoHS a Year After: Too Little, Too Late; 36<br />

Too Much, Too Soon—or Just Right?<br />

Ron Iscoff, Editor<br />

It’s been a year since RoHS became the hottest electronics industry buzzword<br />

since Chlorofluorocarbons. Although the European Union earmarked<br />

six hazardous substances for elimination in electronics, clearly the removal<br />

of lead from electronics was closest to the hearts of the EU commission.<br />

Where has RoHS gone? We’ll tackle that subject now.<br />

Wafer-Bumping Processes, Tools and Trends<br />

Terrence E. Thompson, Senior Editor<br />

Wafer bumping continues to make inroads into the IC packaging<br />

mainstream. As it does, the technology opens Pandora’s box: Should I<br />

bump my own wafers or send them to an experienced contractor?<br />

What technology should I use for bumping? This article might help<br />

you decide.<br />

International Directory of Wafer-Bumping Services<br />

<strong>Chip</strong> <strong>Scale</strong> <strong>Review</strong> Staff<br />

Single Device Tracking: A Cost-Benefit Analysis<br />

Dave Huntley, KINESYS Software<br />

42<br />

50<br />

55<br />

The acceptance and implementation of single device tracking has been<br />

made much easier with the release of SEMI standard E142. This article<br />

discusses how, when and why to implement this new standard on the<br />

assembly floor.<br />

Advances in Wafer Plating: Meeting the Next 61<br />

Challenge of Through-Silicon-Via Processing<br />

Bob Forman, Rohm and Haas Electronic Materials<br />

Copper electroplating has become a standard in electronics for making<br />

electrical interconnects between devices. A new packaging technology,<br />

using through-silicon-vias employs copper plating for high-density<br />

packaging at wafer level through chip stacking.<br />

Handling and Processing Technologies Utilized 69<br />

In a High-Volume Manufacturing Environment<br />

Stefan Pargfrieder, Paul Lindner, Steven Dwyer<br />

and Thorsten Matthias, EV Group<br />

As semiconductor manufacturers continue to squeeze the thickness<br />

of devices and wafers down, new and disruptive methods to meet the<br />

manufacturing challenges associated with new products and processes<br />

have to be utilized.<br />

CONTINUED >><br />

<strong>Chip</strong> <strong>Scale</strong> <strong>Review</strong> ■ <strong>July</strong> <strong>2007</strong> ■ [<strong>Chip</strong><strong>Scale</strong><strong>Review</strong>.com] 1

The roadmap to opportunity<br />

starts here<br />

Electrolytic Wafer Bumping<br />

Electrolytic Copper<br />

Stop by our Semicon West booth<br />

for an opportunity to win a GPS<br />

© Rohm and Haas Electronic Materials, <strong>2007</strong>. InterVia, Solderon, Rohm and Haas, and Rohm<br />

and Haas Electronic Materials are trademarks of Rohm and Haas Company or its affiliates.<br />

Photoimageable Dielectric<br />

Opportunity::: We know you are faced with immense challenges on your technology roadmap.<br />

Our suite of InterVia and Solderon products and processes provides you with the opportunity to meet<br />

your biggest challenges. We bring the most advanced materials technology, innovative processes,<br />

improved reliability and environmentally-friendly solutions for your most demanding wafer-level<br />

packaging applications:<br />

■<br />

■<br />

■<br />

Dielectrics for WLCSP and redistribution<br />

Electrolytic copper for through silicon<br />

vias, redistribution and seed layers<br />

Thick resists for wafer bumping<br />

■<br />

■<br />

Electrolytic low-alpha tin and lead-free<br />

processes for wafer bumping<br />

Electroplating metals for UBM<br />

The roadmap to opportunity starts here…<br />

please visit us at Semicon West, booth #8533, West Hall, Level 2 to find out more.<br />

www.rohmhaas.com

CONTENTS<br />

FEATURE ARTICLES<br />

Projection Scanning: Not a New Kid on the Block<br />

Jim Sooy<br />

75<br />

What’s the best photolithography tool for<br />

your wafer-level packaging applications? In<br />

this article we’ll take a close look at projection<br />

scanning and compare it to 1:1 wafer<br />

steppers and proximity alignment systems.<br />

From Cow <strong>Chip</strong>s to Silicon <strong>Chip</strong>s: Setting-Up a WLP 87<br />

Microfabrication Facility Far from the Infrastructure<br />

Fred Haring, Bernd Scholz, Syed Sajid Ahmad and Aaron<br />

Reinholz, Center for Nanoscale Science and Engineering,<br />

North Dakota State University<br />

Setting up a modern facility for wafer-level<br />

fabrication, chip-scale packaging and<br />

surface mount technology far from the center<br />

of semiconductor activity entails tough<br />

challenges and careful planning. This article<br />

relates some of the good, the bad and the<br />

Quasimodo-ugly experiences faced by the<br />

NDSU staff.<br />

Did You Know? <strong>Chip</strong> <strong>Scale</strong> <strong>Review</strong> is now offered in a<br />

digital format with a powerful search engine!<br />

DEPARTMENTS<br />

Publisher’s Letter Gene Selven<br />

Another great year For SEMICON and us!<br />

Assembly Lines Ron Iscoff<br />

Software radio: can you hear me now?<br />

MEMS the Word! Terrence E. Thompson<br />

What packaging hurdles do MEMS face?<br />

Electronic Trends Steve Berry and Sandra Winkler<br />

Wafer-level packaging with a twist<br />

Industry News<br />

Profile: TTS Group (Advertorial)<br />

Product Showcase (Advertisement)<br />

What’s New!<br />

Inside Patents A. Jason Mirabito and Carol Peters<br />

How to file patents (and fight patents) without tears!<br />

Calendar<br />

Ad Index/More News/Sales Offices<br />

4<br />

7<br />

9<br />

13<br />

15<br />

80<br />

81<br />

82<br />

85<br />

99<br />

104<br />

<strong>Chip</strong> <strong>Scale</strong> <strong>Review</strong> ■ <strong>July</strong> <strong>2007</strong> ■ [<strong>Chip</strong><strong>Scale</strong><strong>Review</strong>.com] 3

PUBLISHER’S LETTER<br />

Another Great Year<br />

For SEMICON and Us!<br />

By Gene Selven, Publisher [gselven@aol.com]<br />

The SEMICON West exposition in San Francisco this year will feature 1300<br />

exhibitors—including <strong>Chip</strong> <strong>Scale</strong> <strong>Review</strong>. During the show, we’ll distribute<br />

thousands of extra copies of this magazine to show visitors from our booth,<br />

W2-8717, and from racks in Moscone Center’s West Hall.<br />

Forgive us for tooting our own horn, but our SEMICON West issue—the one you’re<br />

reading right now—has about 25 percent more advertisers than we carried in last<br />

year’s show issue!<br />

We’ve mailed about 26,000 copies, and our digital edition will be read by an estimated<br />

additional 10,000 people worldwide.<br />

By the way, did you know that <strong>Chip</strong> <strong>Scale</strong> <strong>Review</strong> is the leading magazine for the IC<br />

assembly and packaging community? What do we mean by “leading”?<br />

• More editorial pages on an issue-by-issue basis than our nearest competitor.<br />

• More staff-written editorial pages on an issue-by-issue basis, more than twice as many!<br />

• More advertising pages in every issue—and this is where the “rubber meets the<br />

road” for a publication, since it shows the faith our advertisers have placed in us!<br />

• Two key editors with a combined total of 50 years in the semiconductor industry,<br />

creating a magazine of editorial excellence!<br />

The company that publishes the number two magazine in the field has 40 other magazines<br />

in such areas as oil and gas, dentistry, graphic arts, electrification, etc., plus a multitude<br />

of conferences in those areas.<br />

We have one magazine, this one; a newsletter, The TUESDAY REPORT; and one conference,<br />

our International Wafer-Level Packaging Conference in September. We don’t have to worry<br />

about what the corporate nabobs in Tulsa want. The buck stops right here—with me.<br />

Decisions are made in Silicon Valley, the capitol of semiconductor technology since the beginning.<br />

We’re dedicated to publishing the best magazine for IC assembly and packaging<br />

available. That is our continuing goal, and that is our mission. And our advertisers and<br />

readers, by making us #1, have shown that we’re succeeding.<br />

Report from ECTC<br />

I recently returned from the 57th Electronic Components and Technology Conference<br />

(ECTC) in Reno, Nevada.<br />

ECTC continues to be a “must-see” conference that provides a dynamic environment<br />

for learning, discussion and networking the technology.<br />

We were, by the way, the only publication whose publisher was on site. We spoke to<br />

about 60 exhibitors, many of whom will also be at SEMICON West.<br />

Our congratulations to the ECTC participants and staff for an outstanding event! i<br />

4<br />

<strong>Chip</strong> <strong>Scale</strong> <strong>Review</strong> ■ <strong>July</strong> <strong>2007</strong> ■ [<strong>Chip</strong><strong>Scale</strong><strong>Review</strong>.com]<br />

VOLUME 11, NUMBER 5<br />

The International Magazine of <strong>Chip</strong>-<strong>Scale</strong><br />

Electronics, Flip-<strong>Chip</strong> Technology, Optoelectronic<br />

Interconnection and Wafer-Level Packaging<br />

STAFF<br />

Gene Selven Publisher<br />

7291 Coronado Dr., Ste. 8, San Jose, CA 95129<br />

b 408.996.7016 > 408.996.7871<br />

gselven@aol.com<br />

Ron Iscoff Editor & Associate Publisher<br />

929 Ebbetts Ave., Manteca, CA 95337<br />

b 209.824.1289 > 209.644.7747<br />

chipscale@gmail.com<br />

Terrence Thompson Senior Editor<br />

2303 Randall Rd. #140, Carpentersville, IL 60110<br />

b 847.515.1255<br />

tethompson@aol.com<br />

Steve Berry Contributing Editor<br />

b 408.369.7000 > 408.369.8021<br />

saberry@electronictrendpubs.com<br />

Dr. Tom Di Stefano Contributing Editor<br />

b 408.399.4501 > 408.395.0448<br />

tom@centipedesystems.com<br />

Dr. Subash Khadpe Contributing Editor<br />

skhadpe@semitech.com<br />

Harvey S. Miller Contributing Editor-at-Large<br />

b 650.328.4550 > 650.327.2360<br />

h.miller@ieee.org<br />

Paul M. Sakamoto Contributing Editor–Test<br />

b 925.924.9110 x148<br />

paul.sakamoto@inovys.com<br />

Sandra Winkler Contributing Editor<br />

b 408.369.7000 > 408.369.8021<br />

slwinkler@electronictrendpubs.com<br />

The Official Publication of the WLCSP Forum<br />

SUBSCRIPTION INQUIRIES<br />

Judy Levin <strong>Chip</strong> <strong>Scale</strong> <strong>Review</strong><br />

7291 Coronado Dr., Ste. 8, San Jose, CA 95129<br />

b 408.996.7016 > 408.996.7871<br />

csrsubs@chipscalereview.com<br />

ADVERTISING PRODUCTION<br />

INQUIRIES<br />

Kim Newman<br />

7291 Coronado Dr., Ste. 8, San Jose, CA 95129<br />

b 408.996.7016 > 408.996.7871<br />

csradv@aol.com<br />

REPRINTS<br />

Kim Newman b 408.996.7016<br />

8 csradv@aol.com<br />

ADVISORS<br />

Mark DiOrio MTBSolutions<br />

Dr. Tom Di Stefano Centipede Systems<br />

Charles R. Harper Technology Seminars Inc.<br />

Mark Murdza Antares Advanced Test Technologies<br />

Dr. Guna Selvaduray San Jose State University<br />

Dr. Thorsten Teutsch Pac Tech<br />

Dr. Dietrich Tönnies SUSS MicroTec AG<br />

Dr. David Tuckerman Tessera Technologies<br />

Professor C.P. Wong Georgia Tech<br />

Copyright © <strong>2007</strong> by Gene Selven & Associates Inc.<br />

<strong>Chip</strong> <strong>Scale</strong> <strong>Review</strong> (ISSN 1526-1344) is a registered trademark<br />

of Gene Selven & Associates Inc. Publishing headquarters are<br />

located at 7291 Coronado Drive, Suite 8, San Jose, CA 95129.<br />

All rights reserved.<br />

<strong>Chip</strong> <strong>Scale</strong> <strong>Review</strong> is published eight times a year.<br />

Subscriptions in the U.S. are available without charge to<br />

qualified individuals in the electronics industry. Subscriptions<br />

outside the U.S. (eight issues) by airmail are $60 per year to<br />

Canada or $60 to other countries. In the U.S., subscriptions<br />

by first class mail are $40 per year.

Semicon booth #7857<br />

let us<br />

qualify<br />

your<br />

samples<br />

Introducing our new Advanced Packaging Laboratory<br />

For the first time in North America—qualify your samples on high-volume production equipment,<br />

not semi-automatic tools.<br />

Our equipment set includes:<br />

• Dispensing<br />

• Au/Au ultrasonic bonders<br />

• ±3μm accuracy flip chip bonders<br />

• Plasma treatment—in-line<br />

• Au stud bump bonders<br />

• High-speed chip mounters<br />

• Printing and reflow<br />

For Process:<br />

• Bumping, dicing, bonding, underfill—then full<br />

analysis with X-Ray, SEM and C-SAM<br />

• Conduct DOE’s on production equipment,<br />

expedite the transition to HVM<br />

For inspection and analysis:<br />

• X-Ray<br />

• SEM<br />

• C-SAM<br />

• Die/Bump Shear Tester<br />

• Goniometer<br />

• Temp/Humidity Cycling Chamber<br />

• IR Scope<br />

• Digital Scope<br />

Panasonic<br />

Factory Solutions Company of America<br />

847-495-6100<br />

PFSAmarketing@us.panasonic.com<br />

panasonicfa.com/lab3/

MicrobondAntec –<br />

the power to keep in touch<br />

Solder pastes, wires and<br />

ribbons for Die-Attach and<br />

Die- & Clip-Attach applications<br />

Please visit us at<br />

Semicon West<br />

San Francisco<br />

Booth 8810<br />

01784 www.aim.de<br />

Umicore AG & Co. KG<br />

Microbond - EPM<br />

Hanau · Singapore · Raleigh<br />

www.microbond.eu<br />

Each problem is different; there are specific<br />

answers to any question and specialists who<br />

know what they are doing for every kind of work.<br />

This is why we focus on two things: individual<br />

solutions and innovative ideas.<br />

In our work it is not the search for patent that<br />

has priority in our work, but rather the conversion<br />

of basic research and skills into reliable, customerspecific<br />

processes. This guarantees our customers<br />

functional products and smooth integration.<br />

However, above all it is a love of detail and<br />

consistent quality management that make<br />

MicrobondAntec products into what they are:<br />

the reliable individual solution for all Die-Attach<br />

and Die- & Clip-Attach applications!<br />

Ask us, because Umicore has the solution for<br />

your problems and with MicrobondAntec,<br />

the right answer.<br />

Umicore: a good joint keeps its promise!

ASSEMBLY LINES<br />

Software Radio: Can You Hear Me Now?<br />

By Ron Iscoff, Editor [chipscale@gmail.com]<br />

Unlike “normal” people,<br />

editors live in issue years.<br />

When it’s May, which it is<br />

now, we’re thinking of <strong>July</strong>. When it’s<br />

August, we’ll be thinking of December,<br />

or earlier or later, depending on when<br />

our next issue is printed.<br />

Too bad everyone doesn’t think like we<br />

do. If they did, no one would ever be late!<br />

When you read this, SEMICON West<br />

will be almost a memory—a good, bad<br />

or indifferent one, depending on your<br />

point of view and your business.<br />

At this point, many of you may be<br />

soaking your feet in Epsom salts as you<br />

wait for your corns and calluses to enjoy<br />

the sweet relief from Moscone’s hard,<br />

concrete floors.<br />

Still Lamented<br />

Even after all these years, I still lament<br />

the loss of the San Mateo County Fairgrounds,<br />

SEMICON West’s original venue<br />

(and one that was only about two miles<br />

from my house).<br />

For my colleagues who are becoming<br />

somewhat long in the tooth like me—<br />

and you know who you are—I have a<br />

pop quiz for you: What “things” were<br />

the buildings at the San Mateo County<br />

Fairgrounds named after? Can you<br />

name four of them? You’ll find the<br />

answers at the bottom of this page.<br />

Sadly, Moscone has taken the easy<br />

way out: The buildings are either North<br />

Hall, South Hall or West Hall.<br />

Last year after the show, I suggested<br />

that the Powers that Be (PtB) at Moscone<br />

rename the halls after famous people. I<br />

suggested “Homer Simpson Hall,”“Spartacus<br />

Hall,” and “Venus de Milo Hall.”<br />

I won’t even go into further details,<br />

since the PtB appear to have disregarded<br />

my well-meaning suggestions.<br />

In my next column, I’ll be thinking<br />

out loud again. And we will both have<br />

benefited because SEMICON West will<br />

be over for another year.<br />

One possible question I will address<br />

may be, “Is SEMICON West now an<br />

antiquated albatross with algae-like<br />

detritus dangling from its oral cavity?”<br />

I hope to see you (or hope I saw you<br />

at Moscone). If not, I guess it was karma.<br />

Sin City Follies<br />

As we reported earlier, APEX has abandoned<br />

The City of the Angels, Los Angeles, for<br />

Las Vegas, the City of What? I’ve been to<br />

Vegas a few times over the years, but I<br />

leave the gambling to my better fraction.<br />

APEX, however, is betting that Vegas<br />

will bring the magic touch to its conference—magic<br />

that’s been on the wane.<br />

Appropos Vegas, as philosophers have<br />

pointed out, you don’t build multimillion-dollar<br />

casinos like New York,<br />

New York or Mandalay Bay from the<br />

contributions of winners!<br />

SEMI itself, which is getting as long<br />

in the tooth as I am, has made guttural<br />

noises from time-to-time about moving<br />

the whole SEMICON West kit-n-kaboodle<br />

to Sin City. From what I understand,<br />

that’s still a possibility over the long<br />

term.<br />

Photo taken at last year’s SEMICON West shows<br />

Homer Simpson Hall (at left, formerly North Hall)<br />

and Venus de Milo Hall (formerly South Hall).<br />

Free for All<br />

Seriously folks, how often do you get<br />

something valuable free? I don’t mean<br />

the samples of Grandma’s Tortilla Dip<br />

that they hand out at Costco while you’re<br />

heading for the bread aisle. I mean something<br />

really good for you!<br />

Well, it’s here now. Dr. Ken Gilleo,<br />

that witty inventor, chemist, litigation<br />

consultant, MEMS<br />

expert, public<br />

speaker, mime,<br />

scrivener, multicoastal<br />

manabout-Rhode<br />

Island and manamong-men<br />

(and<br />

Get your free download these are only a<br />

of Ken Gilleo's book! few of the glowing<br />

descriptions he<br />

uses in his own bio!) will let you download<br />

his latest book, The Day Niagara<br />

Falls Turned Green, free!<br />

Continued on page 101 >><br />

<strong>Chip</strong> <strong>Scale</strong> <strong>Review</strong> ■ <strong>July</strong> <strong>2007</strong> ■ [<strong>Chip</strong><strong>Scale</strong><strong>Review</strong>.com] 7

MEMS THE WORD!<br />

What Packaging Hurdles Do MEMS Face?<br />

By Terrence E. Thompson, Senior Editor [tethompson@aol.com]<br />

Will MEMS (microelectromechanical<br />

systems) play<br />

nice with ICs and what<br />

packaging hurdles lie ahead? Are they<br />

candidates for wafer-level packaging?<br />

Let’s look at the facts:<br />

One of the most exciting, and frustrating,<br />

aspects of grasping the MEMS<br />

market share is the incredible rate of<br />

adoption in dozens, probably hundreds,<br />

of industries. Industry groups such<br />

as the MEMS Industry Group (MIG)<br />

in Pittsburgh, Pa. do an excellent job<br />

of tracking progress.<br />

[memsindustrygroup.org]<br />

A Better MEMS Product<br />

Those incredibly small MEMS, and<br />

their nanoscale NEMS counterparts, are<br />

increasingly fulfilling needs that complement<br />

ICs, not replacing them.<br />

In some cases, ICs were small enough<br />

for many sensor, medical and other<br />

applications, but were in need of equally<br />

Sensors are a major application area for MEMS.<br />

(Bosch Sensortec GmbH)<br />

Continued on page 99 >><br />

<strong>Chip</strong> <strong>Scale</strong> <strong>Review</strong> ■ <strong>July</strong> <strong>2007</strong> ■ [<strong>Chip</strong><strong>Scale</strong><strong>Review</strong>.com] 9

Coat/Develop<br />

Photolithography Clusters<br />

Spin Coating<br />

SSEC 3306/8<br />

Fully Automated<br />

to 8 Process Modules<br />

SSEC 3303/4<br />

Fully Automated<br />

to 4 Process Modules<br />

Hot Plate Bake Processing<br />

Wafer production success comes only through a combination of effective<br />

processes and the systems that implement them. Turn to Solid State<br />

Equipment Corporation, a company committed to process—with precise,<br />

high throughput systems that will maximize your wafer production and<br />

support that optimizes your processing. Contact us to have a system<br />

configured to your specific requirements.<br />

SCARA Robotics<br />

SSEC robotic clusters with Class 1 internal<br />

environment include DSP servo spin<br />

control with dynamic coat dispensing and<br />

dispense pump modulation, to routinely<br />

achieve < 1% uniformity.<br />

Clean Production Capability<br />

SSEC Compliance<br />

SEMI ® S2-0703aE Safety<br />

SEMI S8-0705 Ergonomics<br />

FM 4910 Materials<br />

SECS GEM CCS 200 & 300<br />

CE Marked<br />

ETL Listed<br />

Fluid Recirculation System with Maximum Purity (Patent Pending)<br />

A programmable, in-situ collection ring precisely controls the collection of fluids during processing. The system, with open and closed<br />

positions, maintains the purity of the recirculated fluid. A simple gravity drain system avoids hygroscopic action on chemistry.<br />

Open for Etch Solution Recirculation Closed for Post-etch Cleanup Closed for Final Rinse and Dry

Solvent Strip<br />

Immersion and Single<br />

Wafer Processing<br />

Etch<br />

Uniform, Selective Etching on<br />

Multiple Process Levels<br />

Clean<br />

99% Particle Removal Efficiency at<br />

the 88 nm, 65 nm, and 45 nm Nodes<br />

Solvent Immersion<br />

Backside/Bevel Cleaning<br />

High Velocity Fan Scrub<br />

High Pressure Spray<br />

Spray Etch<br />

Single Wafer Megasonic Scrub<br />

US #6,539,952<br />

High Pressure Needle Dispense<br />

Using only milliliters of solvent per wafer,<br />

SSEC solvent processors combine batch<br />

immersion and single wafer spray technology<br />

in one SEMI ® safety compliant,<br />

dry-in/dry-out system. High pressure sprays<br />

are entirely under closed-loop control<br />

for flow, temperature, and dispense<br />

arm motions.<br />

High Pressure Flow Control<br />

Stream Flow Etch<br />

Whether your wet etch requirements are<br />

for structured wafers, backside/bevel strips,<br />

or wafer thinning, SSEC’s patented tools<br />

achieve more controlled results and substantial<br />

COO reduction, compared to batch<br />

or alternative single wafer systems. SSEC’s<br />

exclusive WaferChek in-situ adaptive<br />

process control ensures an optimum etch<br />

on every wafer.<br />

Rotary PVA Brush Scrub<br />

With advanced single wafer non-contact<br />

and contact cleans, SSEC systems can<br />

be configured exactly to your cleaning<br />

requirements. Using dilute chemistries,<br />

such as SC-1 1:1:300, SSEC cleaning<br />

processors have 99% particle removal<br />

efficiency at the 88 nm, 65 nm, and<br />

45 nm nodes, with 30 nm particle size<br />

in development.<br />

Pressure<br />

SiO 2 Etch<br />

Time<br />

Ti Etch<br />

Cu Etch<br />

Solid State<br />

Equipment Corporation<br />

215-328-0700 • email: info@ssecusa.com<br />

www.ssecusa.com

JCET<br />

Your Next<br />

Packaging Partner<br />

for turnkey services in package design,<br />

wafer bumping and probing, assembly and test!<br />

JCET – China<br />

Tel: +86-510-86853728-21#<br />

E-mail: Mary.Hsu@cj-elec.com<br />

Web: www.cj-elec.com<br />

JCET – USA<br />

Tel: 510-573-3612<br />

E-mail: bli@jcet-us.com<br />

Web: www.cj-elec.com<br />

JCET – Taiwan<br />

Tel: +886-3-5634717<br />

E-mail: climax6@ms65.hinet.net<br />

Web: www.cj-elec.com

ELECTRONIC TRENDS<br />

Wafer-Level Packaging with a Twist<br />

By Steve Berry, Contributing Editor [saberry@electronictrendpubs.com] and<br />

Sandra Winkler, Contributing Editor [slwinkler@electronictrendpubs.com]<br />

Wafer-level packages (WLPs)<br />

are IC packages created on<br />

full wafers, rather than on<br />

individual die. Thus, WLPs have the distinction<br />

of being truly die-sized.<br />

WLPs are ideal for handheld products<br />

which require small form factors and<br />

light weight.<br />

However, because they are die-size,<br />

WLPs are not a standard size. Fortunately,<br />

many handheld products frequently<br />

change the design, which lessens the<br />

impact when the package size shrinks<br />

after a die shrink.<br />

Benefits of a WLP<br />

Given that WLPs are created on the face<br />

of the die, they boast the shortest electrical<br />

path. Because WLPs are a tested part<br />

when completed, the devices can also be<br />

used in modules as known good die.<br />

In addition to excellent electrical performance,<br />

reduced cost is a driving<br />

force behind wafer-level packaging. The<br />

cost for packaging the devices on a<br />

given wafer does not change with the<br />

number of die per wafer; generally, all<br />

processes are additive and subtractive<br />

steps performed with mask steps.<br />

As a result of the benefits of WLPs,<br />

their numbers will continue to grow<br />

rapidly, as illustrated in the figure.<br />

Where Are WLPs Found?<br />

IC products that contain WLPs include<br />

Continued on page 101 >><br />

<strong>Chip</strong> <strong>Scale</strong> <strong>Review</strong> ■ <strong>July</strong> <strong>2007</strong> ■ [<strong>Chip</strong><strong>Scale</strong><strong>Review</strong>.com] 13

innovation<br />

Finding new ways to solve problems—whether it’s new<br />

obstacles that arise or the usual process challenges—<br />

we’re here to offer a unique combination of strengths.<br />

Recent example: our award-winning printable phase change material.<br />

Honeywell’s ongoing research and development in chemistry, metallurgy,<br />

and the processes that bring them together—from our new packaging<br />

R&D facility in Spokane, Washington, to our technology center in Shanghai, China—ensure that<br />

wherever challenges arise, we’ll continue to create solutions that solve them. And as a partner to<br />

most of the top semiconductor houses worldwide, our technology portfolio is consistently at the<br />

forefront of invention, empowering the global leaders of innovation. Honeywell Electronic Materials—<br />

helping the manufacturers of today navigate the future.<br />

Contact Honeywell for solutions to your puzzle…<br />

visit www.honeywell.com/sm/em or call 1-408-962-2000.<br />

© <strong>2007</strong> Honeywell International Inc. All rights reserved.

INDUSTRY NEWS<br />

Singapore’s Flextronics to Acquire<br />

Solectron, Milpitas, for $3.6 Billion<br />

Singapore—The shrinking world of EMS<br />

providers will become smaller still with the<br />

proposed acquisition of giant Solectron,<br />

Milpitas, Calif., by competitor Flextronics,<br />

Singapore.<br />

The acquisition has already been approved<br />

by both boards. Flextronics will pay $3.6<br />

billion, based on the June 1 closing price of<br />

the company’s common stock.<br />

SEMICON West XXXVII<br />

Our Annual Rite-of-Passage<br />

‘Glory Days’ Are Gone!<br />

“No surprise there! The glory days of non-<br />

Asia-based EMS companies such as<br />

Solectron are long gone,” said Dr. Subash<br />

Khadpe, president of the Semiconductor<br />

Technology Center, Neffs, Pa., responding<br />

to the acquisition news.<br />

“The future is with Hon Hai Precision<br />

(Foxconn), Flextronics, et al.”<br />

Continued on page 17 >><br />

Panasonic’s Grand Opening<br />

Was Truly a First-of-Its-Kind<br />

Buffalo Grove, Ill.—Attendance exceeded<br />

160 on June 7, when the doors opened to<br />

Panasonic’s new Advanced Packaging Lab<br />

for Microelectronics, a significant event<br />

for North American chipmakers and electronics<br />

designers and producers.<br />

Panasonic Factory Solutions Co. Ltd.<br />

(PFSC) President Katsutoshi Kanzaki, and<br />

Director Neal Okuda of Panasonic Factory<br />

Solutions Co., Osaka,<br />

Japan, handled the<br />

opening remarks.<br />

PFSC has long been a<br />

major player in IC<br />

package development,<br />

and now it’s opening<br />

the new lab to those<br />

Gene Dunn<br />

Continued on page 20 >><br />

INSIDE NEWS<br />

• SEMI Says Q1 Billings for Equipment Reached<br />

$10.75 Billion page 104<br />

This is a view looking down from the escalator in the second floor of West Hall, the newest<br />

building at Moscone Center. (<strong>Chip</strong> <strong>Scale</strong> <strong>Review</strong>)<br />

By Ron Iscoff, Editor<br />

San Francisco—SEMICON West, the semiconductor equipment industry’s<br />

annual rite of passage in <strong>July</strong> is upon us.<br />

When you hear someone say, en passant, “This will be my first SEMICON<br />

West.” You can’t contain a secret snicker; an ungracious chortle, way down<br />

deep in your throat; you know you can’t! It is, to crib a line from Charles<br />

Dickens’ Tale of Two Cities, “The Best of Shows, the Worst of Shows!”<br />

Continued on page 17 >><br />

<strong>Chip</strong> <strong>Scale</strong> <strong>Review</strong> ■ <strong>July</strong> <strong>2007</strong> ■ [<strong>Chip</strong><strong>Scale</strong><strong>Review</strong>.com] 15

Synergetix ®<br />

Test Sockets...<br />

No small<br />

accomplishments.<br />

When you zoom in, the<br />

picture of what makes our<br />

Synergetix ®<br />

Test Sockets superior<br />

becomes very clear ... IDI probe<br />

technology. We introduced spring probe technology in test<br />

sockets over two decades ago. In 1996, we introduced the<br />

first 1.0 mm pitch three-piece probe design, an accomplishment<br />

that set new standards, both mechanically and electrically. Our<br />

engineers continued to meet smaller and smaller<br />

pitch requirements by taking our flagship three-piece<br />

design to the 0.4 mm level, pictured here in the eye<br />

of a needle. Today, our technology continues to<br />

give you the biggest advantage on the test floor<br />

with innovations like XACT, the first selfadjusting<br />

test socket. Take a closer look online.<br />

See why Synergetix Brand Test Sockets offer<br />

you the most advanced interconnect available.<br />

Visit us at www.synergetix .com<br />

Visit us at www.synergetix.com<br />

INTERCONNECT DEVICES, INC.<br />

SPRING CONTACT PROBES • CONNECTORS • INTERFACES • SYNERGETIX ® TEST SOCKETS<br />

5101 Richland Avenue • Kansas City, KS 66106 • FAX: (913) 342-7043 • PHONE: (913) 342-5544<br />

E-MAIL: info@idinet.com • WEB: www.idinet.com

INDUSTRY NEWS<br />

SEMICON West Continued from page 15 >><br />

A person’s first SEMICON West is a<br />

rite akin to a Bar Mitzvah held in the sandy<br />

trenches of the Gaza Strip with artillery<br />

rounds buzzing overhead; or a Baptism<br />

conducted on a burning funeral pyre in<br />

the humanity-swollen Ganges River.<br />

I have been to more SEMICON West<br />

shows than I have fingers and toes, a lot<br />

more. This will be the thirty-seventh<br />

running of this nearly indescribable<br />

event, which means the first—which I<br />

did not attend—took place in 1970.<br />

The Fairgrounds Remembered, Fondly<br />

In past issues, we have repeated our fond<br />

recollections of SEMICON West at the<br />

San Mateo County Fairgrounds.<br />

We have also noted our many trips to<br />

the Convention Center in San Jose to<br />

observe the shenanigans of the backend<br />

equipment displays; and we have intermittently<br />

chided our good friends at<br />

SEMI for the continuing on/off San<br />

Francisco agglutination.<br />

We will, as we have done for lo these<br />

many years, give you our impressions of<br />

SEMICON West XXXVII in due course,<br />

after the show is finished, the lights<br />

turned off at Moscone, and the displays<br />

placed in moth balls for another year.<br />

But this year, I decided to let you tell<br />

me how you feel about SEMICON West.<br />

Continued on page 23 >><br />

THERE ARE NO SHORTCUTS<br />

TO A 5-MIL DOT<br />

Micro-volume dispensing requires three core<br />

technologies. Without them, you can forget<br />

about accurate volumes and placement:<br />

• DL Micro Valve with brushless<br />

servo motor dispenses micro<br />

volumes of material in precise,<br />

repeatable patterns.<br />

This was the way it looked, circa 1985, from outside<br />

the Fairground gates. (SEMI photo)<br />

Flextronics Continued from page 15 >><br />

Combined, the companies will operate<br />

in 35 countries with a workforce of<br />

200,000, which includes about 4000<br />

design engineers.<br />

Total annual revenues are expected to<br />

exceed $30 billion.<br />

In its news release, Flextronics’ CFO<br />

is quoted as saying, “While some synergies<br />

will be achieved in the first 12 months<br />

after closing, it could take up to 18-24<br />

months to fully integrate this acquisition<br />

and realize the full synergy potential,<br />

which we estimate to be at least $200<br />

million after-tax.”<br />

Flextronics reported fiscal year <strong>2007</strong><br />

revenues of $18.9 billion. Solectron<br />

reported sales from continuing operations<br />

in fiscal 2006 of $10.6 billion.<br />

[flextronics.com] ■<br />

• DL carbide auger and cartridge<br />

combine for exceptional material<br />

flow. Easily extracted for<br />

rapid cleaning.<br />

For dot sizes less than 10-mil, there is one<br />

product line that is proven and trusted –<br />

by manufacturers in semiconductor packaging,<br />

electronics assembly, medical device, and<br />

electro-mechanical assembly the world over.<br />

R<br />

• DL custom dispensing needles<br />

precision machined from<br />

solid stainless steel.<br />

Conically chamfered tip<br />

facilitates material release.<br />

216 River Street<br />

Haverhill, MA 01832 USA<br />

Phone: 978-374-6451<br />

Fax: 978-372-4889<br />

www.dltechnology.com<br />

Micro Valve is a trademark of DL Technology LLC. DL Technology is a registered trademark of DL Technology LLC.<br />

<strong>Chip</strong> <strong>Scale</strong> <strong>Review</strong> ■ <strong>July</strong> <strong>2007</strong> ■ [<strong>Chip</strong><strong>Scale</strong><strong>Review</strong>.com] 17

INDUSTRY NEWS<br />

Corona, Calif.—Ron Sheets, Tamarack<br />

Scientific founder,<br />

president and CEO,<br />

has retired after 41<br />

years. He will be<br />

replaced as president<br />

and CEO by Steven<br />

Thompson,former<br />

vice president of<br />

Steven Thompson engineering.<br />

PEOPLE IN THE NEWS<br />

Tamarack Scientific Founder Retires; Promotes Thompson and Souter<br />

Thompson, who joined the company<br />

27 years ago, has been in charge of engineering<br />

for development of the company’s<br />

photolithography and laser ablation<br />

systems.<br />

Matt Souter, who joined the company<br />

six years ago, has been promoted to vice<br />

president of sales and marketing.<br />

In a letter to customers, Sheets wrote,<br />

“While I may be stepping back from the<br />

JCET Establishes North American Operations in California<br />

Fremont, Calif.—Jiangsu Changdian<br />

Electronics Technology Co., (JCET),<br />

and its subsidiary, Jiangsu Changdian<br />

Advanced Packaging Co., (JCAP),have<br />

established operations in Fremont.<br />

Dr. Weiping (Bill) Li is the general<br />

manager and is tasked with sales and<br />

marketing activities for North America.<br />

Founded in 1972, JCET/JCAP is the<br />

leading packaging provider in China,<br />

According to Dr. Li.<br />

In the last five years, the company has<br />

grown about 30 percent CAGR, with<br />

2006 revenue reaching $240 million.<br />

JCET’s Fremont office is at 41341<br />

Joyce Ave., Fremont, CA 94539, phone<br />

510.573.3612. [jcet-us.com]<br />

day-to-day management<br />

of Tamarack, I<br />

will continue to pursue<br />

my passion—<br />

developing creative,<br />

best-in-class equipment<br />

that satisfies<br />

our customers’<br />

needs.” [tamsci.com]<br />

Matt Souter<br />

Farrell Replaces Conlon as<br />

CEO of XSIL Ltd., Dublin<br />

Dublin, Ireland—Brian Farrell has<br />

replaced Peter Conlon as CEO of XSIL<br />

Ltd., a maker of laser micro-machining<br />

systems. Conlon has assumed the company’s<br />

chairmanship.<br />

Farrell is an XSIL founder and has<br />

been vice president of engineering since<br />

the company began in April 2000.<br />

[xsil.com]<br />

SuperButton and SuperSpring Contact Elements<br />

High current, high frequency, low inductance<br />

Flexible Design for All Your Engineering Needs • No NRE for Custom Footprints<br />

SuperButton Connector Technology<br />

SuperSpring Connector Technology<br />

Board-to-Board<br />

or Board-to-Flex<br />

Custom Interposers<br />

Land Grid Array<br />

Package-to-Board<br />

Sockets<br />

Engineering Programming & Test Sockets<br />

• Connector free—lengths down to 1.0mm<br />

• Array counts over 2,000<br />

• Pitches down to 0.5mm<br />

• Mating against BGA, LGA, QFN, CSP or flex<br />

sales@hcdcorp.com www.hcdcorp.com (408) 743-9700 x331<br />

Copyright © 2006 High Conection Density, Inc. All rights reserved. Information is subject to change without notice. “SuperSpring” and “SuperButton” are trademarks of High Connection Density, Inc.<br />

18<br />

<strong>Chip</strong> <strong>Scale</strong> <strong>Review</strong> ■ <strong>July</strong> <strong>2007</strong> ■ [<strong>Chip</strong><strong>Scale</strong><strong>Review</strong>.com]

We keep it real.<br />

Not all vision inspection is created equal.<br />

Especially when it comes to 3D. Some<br />

technologies emphasize speed, while others<br />

focus on accuracy.<br />

But SolVision’s 3D is the real deal.<br />

No implied measurements. No toll on speed.<br />

Just true 3D metrology and inspection<br />

at industry-leading throughputs.<br />

Get true 3D vision inspection today...<br />

And keep the competition guessing.<br />

WAFER • IC PACKAGING • FC SUBSTRATE<br />

VISIT US AT SEMICON WEST <strong>2007</strong><br />

JULY 17-19, MOSCONE CENTER, SF<br />

BOOTH 8527 • WEST HALL • LEVEL 2<br />

Global Headquarters<br />

50 De Lauzon Street, Suite 100<br />

Boucherville, QC, Canada J4B 1E6<br />

T: 514.679.9542<br />

F: 514.679.9477<br />

E: sales@solvision.net<br />

SolVision Singapore<br />

205 Woodlands Avenue 9<br />

06-54 Woodlands Spectrum 2<br />

Singapore 738957<br />

T: +65 6759.8858<br />

F: +65 6755.2272<br />

E: sales-asia@solvision.net<br />

© <strong>2007</strong> SolVision inc.

INDUSTRY NEWS<br />

Panasonic Continued from page 15 >><br />

seeking device packaging and inspection<br />

systems guidance.<br />

Panasonic is a huge company with<br />

over 320,000 employees in the group!<br />

Impressive Talent<br />

That is an impressive amount of talent<br />

to back-up any effort, existing or new.<br />

When we hear Panasonic say the new<br />

U.S. process lab is unmatched anywhere,<br />

you have to believe they are serious.<br />

In May <strong>2007</strong>, Panasonic opened a<br />

process lab in Germany in collaboration<br />

with Fraunhofer IZM. They also have<br />

labs in Japan and Singapore, but the<br />

North American lab is said to be the<br />

Cutting the ribbon for the new lab are, left to right,<br />

Neal Okuda, director of Panasonic Factory Solutions<br />

Co. (PFSC); President Katsutoshi Kanzaki, PFSC;<br />

Frank Barney, marketing and communications group<br />

manager, Panasonic Factory Solutions Co. of America;<br />

Bill Brimm, Buffalo Grove Village manager; and Alex<br />

Shimada, president, PFSCA. (Panasonic photo)<br />

most comprehensive yet.<br />

Genn Dunn, PFSA engineering manager<br />

for microelectronics, was as proud<br />

of the lab as a new father.<br />

He said, “Because the cleanroom is<br />

complete with state-of-the-art equipment,<br />

we’re able to offer customers a hands-on<br />

experience for developing truly productive<br />

microelectronics product systems.<br />

For the first time in North America,<br />

customers can qualify their samples on<br />

high-volume production equipment,<br />

not semi-automatic tools.”<br />

Partnership Approach<br />

Dunn stressed Panasonic’s partnership<br />

approach for anyone who needs to<br />

develop a chip package<br />

and/or verify<br />

process integrity.<br />

Unlike the usual<br />

grand openings, this<br />

one had unusual<br />

depth. We heard<br />

some excellent technical<br />

presentations Jan Vardaman<br />

on packaging topics,<br />

including “New Developments and<br />

Trends in SiPs” by Jan Vardaman,<br />

TechSearch International; “Package<br />

Stacking: The Next Dimension in<br />

System Board Design” by Moody Dreiza<br />

Continued on page 23 >><br />

20<br />

<strong>Chip</strong> <strong>Scale</strong> <strong>Review</strong> ■ <strong>July</strong> <strong>2007</strong> ■ [<strong>Chip</strong><strong>Scale</strong><strong>Review</strong>.com]

SENJU SOLDER<br />

Working to Make Lead-Free Virtually<br />

“Pain-Free”<br />

Senju Comtek Corp.<br />

20300 Stevens Creek Blvd. #300<br />

Cupertino, CA 95014<br />

phone: (408) 446-7866 fax: (408) 253-2140<br />

email: sales@senjucomtek.com<br />

www.senjucomtek.com<br />

SMIC<br />

Senju Comtek Corp.

INDUSTRY NEWS<br />

SEMICON West Continued from page 17 >><br />

Japanese sawing machine giant Disco occupied a prominent spot in West Hall at last year’s SEMICON West.<br />

Of course, you’ll be telling SEMI, too.<br />

Exactly to that end, I sent out many,<br />

many e-mails to people in the industry<br />

whom I know and people whom I<br />

don’t. I was surprised at how quickly<br />

responses starting coming back.<br />

I also asked people how they felt<br />

about SEMICON West moving to Las<br />

Vegas. This has been a backburner item<br />

at SEMI for at least a decade. Vegas<br />

draws certain people like a moth to a<br />

flame. (And you know what happens<br />

when a moth is drawn into a flame!)<br />

APEX, as you probably know by now,<br />

has abandoned Los Angeles after one<br />

year and will meet in Vegas next year.<br />

Is the same fate in store for SEMICON<br />

West?<br />

Love/Hate Relationship<br />

Most of us have a love/hate relationship<br />

with SEMICON West. Why is that? I<br />

wondered. Since I didn’t know the<br />

answer, I decided to consult a doctor.<br />

Dr. Phil was not available, so I immediately<br />

thought of Dr. Ken Gilleo, chemist,<br />

MEMS specialist, bon viver and author<br />

of many books. Dr. Ken responded:<br />

We in the Boston area are clueless<br />

about West Coast stuff. Some think that<br />

everything west of the Mississippi is just<br />

grand. Others are sure that there’s nothing<br />

but wasteland once you get past Lake<br />

Woebegone.<br />

I’ve always had a good time at SEMICON<br />

West and didn’t know there was a bad<br />

Continued on page 25 >><br />

Panasonic Continued from page 20 >><br />

of Amkor<br />

Technology, and<br />

“Case Studies in<br />

Electronics Assembly<br />

Solutions” by Tom<br />

Baggio of Panasonic<br />

Factory Solutions<br />

America.<br />

Moody Dreiza I left the grand<br />

opening convinced<br />

that PSFC was both serious and capable<br />

of delivering microelectronics solutions<br />

from chips to wafers.<br />

It is clear Panasonic, with its own systems<br />

and those of partners, is addressing<br />

the needs of board-level through IC<br />

and wafer-level device packaging.<br />

The grand opening ceremony included<br />

the annual joint meeting of trade organizations<br />

IMAPS Chicago/Milwaukee and<br />

SMTA Great Lakes. [panasonicfa.com] ■<br />

–Terry Thompson, Senior Editor<br />

<strong>Chip</strong> <strong>Scale</strong> <strong>Review</strong> ■ <strong>July</strong> <strong>2007</strong> ■ [<strong>Chip</strong><strong>Scale</strong><strong>Review</strong>.com] 23

INDUSTRY NEWS<br />

Amkor and UTAC Sign Cross-License Contract<br />

Workers at Amkor’s Pudong, China, factory inspect leadframes. Amkor and UTAC have agreed to crosslicense<br />

each other on certain package types. (Amkor Technology Inc.)<br />

Chandler, Ariz.—Amkor Technology<br />

Inc., Chandler, and United Test and<br />

Assembly Center Ltd. (UTAC),<br />

Singapore, have signed a multi-year,<br />

package cross-licensing agreement.<br />

Amkor will license its MicroLeadFrame<br />

(MLF) patents to UTAC and UTAC will<br />

license its QFN patents to Amkor.<br />

The contract covers the licensing of<br />

intellectual property rights and the<br />

transfer of associated packaging technologies.<br />

The MLF package is Amkor’s version<br />

of a QFN leadframe-based, near-chipscale<br />

package. The package features an<br />

exposed die paddle and leads on the<br />

bottom.<br />

Amkor says it has shipped about five<br />

billion MLF packages since their introduction<br />

in the late 1990s. [amkor.com]<br />

SEMICON West Continued from page 23 >><br />

side. Well, maybe the long walk between<br />

the front end and backend of the line is<br />

an issue unless you have a golf cart. Or<br />

did they every figure out how to merge<br />

the two ends?<br />

Their website was semi-disabled when<br />

I went to check if it was still a two-town<br />

event. Maybe everyone was surfing the<br />

site on a Sunday afternoon, but let’s hope<br />

not, so it looks like I did find something<br />

to rap about: low bandwidth, or corrupted<br />

scrip or whatever. Maybe the site is only<br />

accessible using San Francisco Wi-Fi.<br />

But if the front end and backend shows<br />

have not yet merged, there’s a solution on<br />

Gregg Taran (left) and Helmut Rutterschmidt of<br />

Datacon, were among major SEMICON West exhibitors<br />

in West Hall last year. (<strong>Chip</strong> <strong>Scale</strong> <strong>Review</strong>)<br />

the way. As Wafer-Level Packaging (WLP)<br />

takes over, the front and backend processes<br />

Continued on page 26 >><br />

<strong>Chip</strong> <strong>Scale</strong> <strong>Review</strong> ■ <strong>July</strong> <strong>2007</strong> ■ [<strong>Chip</strong><strong>Scale</strong><strong>Review</strong>.com] 25

INDUSTRY NEWS<br />

SEMICON West Continued from page 26 >><br />

will merge and that should simplify<br />

SEMICON West.<br />

These responses, for the most part,<br />

have only been edited when someone<br />

became too long-winded or profane;<br />

otherwise, they are verbatim.<br />

From Newport News, Va., on our great<br />

Eastern shores, Gerald Steinwasser of<br />

equipment-maker and SEMICON West<br />

exhibitor Mühlbauer [muhlbauer.com],<br />

wrote:<br />

In my opinion, it was a mistake to<br />

“re-unite”’ the backend in SF. The heart<br />

of the semiconductor industry is in the<br />

valley, and that’s where the show belongs.<br />

A move to Las Vegas would only help the<br />

city of Las Vegas, but not the industry or<br />

SEMICON West.<br />

From the Midwest, Mike Fedde,<br />

president of Ironwood Electronics<br />

[ironwoodelectronics.com], one of our<br />

favorite test and burn-in socket makers,<br />

e-mailed:<br />

Attendees found the lounges outside the second and third floors of West Hall provided a spot to relax and<br />

meet colleagues. (<strong>Chip</strong> <strong>Scale</strong> <strong>Review</strong>)<br />

Don’t move to Vegas, please. We<br />

already have trouble getting customers to<br />

come. None will be in Vegas—they are<br />

engineers. Love/hate info maybe later.<br />

We know our pal, Dr. Skip Fehr, packaging<br />

consultant extraordinaire in San Jose,<br />

is always good for a comment, so he was<br />

one of the first people we contacted. And<br />

he didn’t disappoint this time either:<br />

Why I like SEMICON: It is a chance to<br />

see the new products in a short period<br />

Continued on page 27 >><br />

26<br />

<strong>Chip</strong> <strong>Scale</strong> <strong>Review</strong> ■ <strong>July</strong> <strong>2007</strong> ■ [<strong>Chip</strong><strong>Scale</strong><strong>Review</strong>.com]

INDUSTRY NEWS<br />

Rohm and Haas Opens New Korean R&D Center<br />

Company executives and local officials cut the ribbon dedicating the new Rohm and Haas Electronic<br />

Material Chonan, Korea, Research and Development Center. Participants at the Center’s grand opening were,<br />

from left: H.S. Chung, president, Rohm and Haas Electronic Materials Korea; I.H. Lee, GM; Y.H. Kim, GM,<br />

Samsung Electronics; S.C. Moon, director, Hynix; Y.H. Kwon, deputy mayor of Chonan City; J.S. Lee, Chonan<br />

fire station; J.H. Park, director, Chonan customhouse; and G.H. Kwag, plant manager, Rohm and Haas<br />

Electronic Materials.<br />

Chonan, Korea—Rohm and Haas<br />

Electronic Materials has opened a new<br />

five-story R&D Center in Chonan in<br />

west S. Korea.<br />

The Center represents part of a recent<br />

$30 million expansion of the company’s<br />

Microelectronic Technologies site in<br />

Chonan.<br />

Among other tasks, the Center will<br />

perform research on 193-nm photoresists<br />

as well as organic and silicon-based<br />

anti-reflectants. Now in place, according<br />

to the company, are 193- and 248-nm<br />

lithography clusters, as well as leadingedge<br />

defect and metrology tools.<br />

Further growth of the R&D and engineering<br />

resources will continue throughout<br />

the year, as Rohm and Haas ramps<br />

to meet local and global demand for<br />

next-generation semiconductor materials.<br />

[rohmhaas.com]<br />

SEMICON West Continued from page 26 >><br />

of time, particularly those I do not<br />

presently use. My normal vendors keep<br />

us informed, but the others (of course)<br />

do not. A second reason is that of meeting<br />

and talking to people that I usually see<br />

only at the shows. It’s a great chance to<br />

renew relationships. I always hope to find<br />

that one new product or vendor that<br />

makes being at the show worthwhile.<br />

Why I dislike the SEMICON show: The<br />

biggest issue for me has always been the<br />

parking. If you don’t get to the show<br />

early, the spaces are full and it is difficult<br />

to find a place. I have not found the buses<br />

Klaus Ruhmer (left) of SUSS MicroTec talks with<br />

Fernando Mendez of Image Technology at last<br />

year’s SEMICON West. (<strong>Chip</strong> <strong>Scale</strong> <strong>Review</strong>)<br />

they furnish to be handy enough,<br />

although many do use them. I think the<br />

Continued on page 28 >><br />

<strong>Chip</strong> <strong>Scale</strong> <strong>Review</strong> ■ <strong>July</strong> <strong>2007</strong> ■ [<strong>Chip</strong><strong>Scale</strong><strong>Review</strong>.com] 27

INDUSTRY NEWS<br />

SEMICON West Continued from page 27 >><br />

organizers do a great job once you are in<br />

the show.<br />

Heck No! We Won’t Go (to Vegas)!<br />

Skip also voted against moving the<br />

show to Vegas, as did most people.<br />

Lonny Plummer of Kinesys Software<br />

[kinesyssoftware.com], is content having<br />

the show in San Francisco.<br />

“No” on the move to Vegas; stay in<br />

SFO,Lonny says.<br />

I hate that it has become such a business<br />

and that the show seams to be more<br />

focused on making a dollar than a showcase<br />

for the companies that exhibit. I have<br />

been going to the show for 25 years and<br />

the days of the meadowlands were the<br />

best in terms of focus and results, when<br />

equipment venders actually sold<br />

machines at the show.<br />

That time has come and gone. Now the<br />

show has evolved or degraded into a meetand-greet<br />

for venders. The level of actual<br />

Joel Camarda visited the Antares Advanced Test Technologies booth to discuss sockets with Selina Gonzales.<br />

customers coming to the show to see new<br />

technology in the backend is very limited.<br />

I love the show because it is in SFO<br />

and it is a great time out to meet and<br />

spend some time with old friends.<br />

Martin Hart, president of Mirror<br />

Semiconductor Inc. [mirrorsemi.com],<br />

in Irvine, Calif., admits to being a<br />

“betweener.”<br />

Continued on page 30 >><br />

Your die sorting speed in another dimension<br />

50% higher throughput with the new DS 15000<br />

full flip chip capability at a maximum<br />

throughput of up to 15,000 uph<br />

minimized material change-over times<br />

due to a optional two index track<br />

high speed sorting of dice (especially<br />

WLCSP) at smallest footprint<br />

Highest placement accuracy of ± 30 µm at<br />

die sizes from 0.5 x 0.5 to 7.0 x 7.0 mm<br />

100% online quality inspection and 100%<br />

inkless manufacturing by wafer mapping<br />

Handling of 8'' and optional 12'' wafers<br />

Mühlbauer is a global, independent consultant and manufacturer of turnkey automation solutions for the Smart Card, Smart Label, Semiconductor<br />

Backend and Vision industries. In addition, the company is active in the areas of enrollment and verification of personal data. With more than<br />

1,600 employees in 26 locations on five continents, Mühlbauer is a leading supplier of production equipment for the Smart Card and Smart<br />

Label industry. Mühlbauer solutions enable clients to manufacture any type of chip card, including ID Cards, ePassports, eVisa, Contact and<br />

Contactless Cards, Dual Interface as well as Multimedia Cards and Smart Labels for access control, supply chain management, tracking of<br />

textiles and applications for the retail industry.<br />

TECURITY<br />

R<br />

- Complete Solutions setting the new Standards<br />

Mühlbauer AG<br />

Josef-Mühlbauer-Platz 1<br />

93426 Roding, Germany<br />

Phone: +49 9461 952 - 0<br />

Fax: +49 9461 952 - 1101<br />

Email: info@muehlbauer.de<br />

Internet: www.muehlbauer.de<br />

28<br />

<strong>Chip</strong> <strong>Scale</strong> <strong>Review</strong> ■ <strong>July</strong> <strong>2007</strong> ■ [<strong>Chip</strong><strong>Scale</strong><strong>Review</strong>.com]

INDUSTRY NEWS<br />

Forecast Predicts IC Unit Shipments Will Grow by 9.5% CAGR<br />

San Jose—Industry analyst Electronic<br />

Trend Publications predicts IC unit<br />

shipments will grow from 137 billion<br />

last year to 216 billion units in 2011, a<br />

compound annual growth rate (CAGR)<br />

of 9.5 percent.<br />

Additionally, revenue growth should<br />

nearly equal unit growth from 2006-2011,<br />

as long as the industry is cautious about<br />

adding capacity.<br />

The forecast is made in ETP’s annual<br />

Worldwide IC Packaging Market study,<br />

which also predicts CSPs—including DFNs,<br />

FBGAs/DSBGAs, QFNs and wafer-level<br />

packages—will show the highest growth<br />

rates over the forecast period.<br />

The report also predicts total IC<br />

assembly revenue, based on the estimates<br />

of independent packaging<br />

foundries.<br />

If all packages<br />

had been<br />

assembled by<br />

non-captive<br />

vendors, total<br />

assembly revenue<br />

would<br />

have been $27<br />

billion in<br />

2006. This<br />

will expand,<br />

ETP says, to<br />

nearly $41<br />

billion by<br />

2011, a CAGR of 8.4 percent.<br />

Revenue growth for IC packaging,<br />

however, will trail unit growth over the<br />

next five years, ETP believes, because<br />

competition between vendors will push<br />

ASPs down slightly.<br />

‘Solid Increase’ in Units<br />

Some 43.8 billion ICs were assembled<br />

by packaging foundries last year, ETP<br />

estimates, representing a “solid increase”<br />

from 2005. With overall IC volume up<br />

sharply since the 2001 recession, contractors<br />

have become “very busy again.”<br />

IC packaging revenue was pegged at<br />

$10 billion in 2006 by ETP. This figure<br />

will grow to $19 billion in 2011, a<br />

CAGR of 13.3 percent. This is slightly<br />

above package unit growth.<br />

Much of the recent packaging<br />

foundry volume increases have been in<br />

low-I/O packages. Future growth, says<br />

ETP, should “show a slight increase in<br />

average I/O count” and ASPs.<br />

Last year, independent packaging<br />

foundries were responsible for some 32<br />

percent of the world’s total packages,<br />

nearly 44 billion, essentially unchanged<br />

from 2005.<br />

ETP predicts that contractor volumes<br />

Forecast by Package Family<br />

Units (M) 2006 <strong>2007</strong> 2008 2009 2010 2011 CAGR<br />

DIP 7830 7928 8531 8513 8896 9905 4.8%<br />

SOT 13,870 14,103 16,013 17,076 19,167 21,532 9.2%<br />

SO 35,965 36,123 38,605 38,947 41,979 45,811 5.0%<br />

TSOP 17,926 18,419 19,576 18,798 19,757 20,741 3.0%<br />

DFN 3143 3814 5134 6168 7575 8911 23.2%<br />

CC 865 847 798 692 640 696 -4.3%<br />

QFP 13,267 14,017 15,334 15,570 17,111 18,771 7.2%<br />

QFN 6594 8102 10,202 11,748 14,062 16,401 20.0%<br />

PGA 147 151 150 147 151 155 1.0%<br />

BGA 10,725 11,890 13,615 14,115 15,539 17,063 9.7%<br />

FBGA/DSBGA 14,590 17,521 21,055 23,332 27,245 31,261 16.5%<br />

WLP 3649 3909 4898 6010 7448 9814 21.9%<br />

DCA 8790 9981 11,628 12,158 13,410 14,807 11.0%<br />

Total 137,361 146,807 165,538 173,273 192,979 215,866 9.5%<br />

(Source: ETP)<br />

will grow to 78 billion packages in 2011,<br />

or 36 percent of the total, a CAGR of<br />

12.3 percent.<br />

The report says recent business outcomes<br />

of various packaging foundries<br />

show there are three keys to success:<br />

1. A broad package portfolio; 2. An<br />

extremely lean cost structure; and 3.<br />

Close relations with major wafer<br />

foundries and IDMs.<br />

[electronictrendpubs.com]<br />

Dage Precision Industries Names New Sales Rep<br />

Fremont, Calif.—Dage Precision Industries has appointed Electronic Assembly Products Inc. to represent<br />

its x-ray inspection systems and bond test equipment throughout Colorado, Utah and Costa Rica.<br />

<strong>Chip</strong> <strong>Scale</strong> <strong>Review</strong> ■ <strong>July</strong> <strong>2007</strong> ■ [<strong>Chip</strong><strong>Scale</strong><strong>Review</strong>.com] 29

INDUSTRY NEWS<br />

SEMICON West Continued from page 28 >><br />

SEMICON West is a conundrum. I am<br />

a “betweener,” and I neither love, nor hate<br />

SEMICON West. So why should my<br />

opinion be heard? Am I just one of the<br />

silent majority, who cringes each year and<br />

is numb from the discomfort of having to<br />

deal with flying into SFO and Moscone<br />

Center? If forced to vote between San<br />

Francisco in <strong>July</strong> and the heat of Las<br />

Vegas in <strong>July</strong>, I would opt to continue<br />

with San Francisco.<br />

Of course, if you were to tease me with<br />

the prospect of returning the “backend”<br />

exhibits to their recent home in San<br />

Disco and Synova Join on Hybrid Singulation Saw<br />

Lausanne, Switzerland—Swiss manufacturer<br />

Synova says it will co-develop a<br />

hybrid dicing tool with Disco Hi-Tec<br />

Europe, Munich, Germany, a subsidiary<br />

of Japan’s Disco Corp.<br />

The companies will combine Synova’s<br />

patented Laser MicroJet technology with<br />

Disco’s newest blade-saw dicing systems<br />

to develop a hybrid dicing tool.<br />

The resulting saw, according to the<br />

companies, “will enable semiconductor<br />

manufacturers to meet their dual need<br />

for higher throughput and minimal<br />

damage to silicon wafers.”<br />

The initial tools are scheduled for<br />

introduction late this year.<br />

Both companies will contribute to the<br />

manufacturing of the hybrid saw and<br />

will share marketing and sales tasks.<br />

Synova’s technology combines a laser<br />

beam and a water jet, where a hair-thin wafer<br />

jet guides the laser beam onto the wafer.<br />

Employing the difference in the<br />

refractive indices of air and water, the<br />

technology creates a laser beam that is<br />

completely reflected at the air-water<br />

interface, similar in principle to optical<br />

fiber. [disco.co.jp]<br />

Jose, I would definitely opt for that.<br />

Bottom line, the benefits of attending<br />

the show still outweigh petty arguments<br />

involving its location. Place it<br />

where you will. I still vow to make the<br />

annual trek to SEMICON West.<br />

Mark Sullivan, marcom director at<br />

Kulicke & Soffa [kns.com], Horsham,<br />

Pa., wisely avoided the Las Vegas part of<br />

our question. But he had this to say<br />

about the show:<br />

SEMICON West has evolved into an<br />

industry-positioning event for all its<br />

exhibitors and attendees.<br />

At this three-day exhibition, companies<br />

create dialogs between semiconductors<br />

management leaders and the financial<br />

world to review and discuss the most current<br />

trends and future emerging<br />

roadmaps.<br />

The show is becoming less about just<br />

showing chip equipment and materials,<br />

Continued on page 32 >><br />

30<br />

<strong>Chip</strong> <strong>Scale</strong> <strong>Review</strong> ■ <strong>July</strong> <strong>2007</strong> ■ [<strong>Chip</strong><strong>Scale</strong><strong>Review</strong>.com]

INDUSTRY NEWS<br />

SEMICON West Continued from page 30 >><br />

and more about building closer relationships<br />

within the market. With so much of<br />

our semiconductor industry moving to<br />

Asia, companies located in the United<br />

States utilize SEMICON West as a key<br />

gathering place to meet and get the pulse<br />

on our chip industry.<br />

The show also provides an important<br />

forum to review new technology roadmaps<br />

and difficult industry challenges. Bottomline:<br />

SEMICON West is changing just like<br />

our industry is changing. It is not becoming<br />

obsolete to anyone.<br />

never stop. Also the number of vendors<br />

who purchase exhibitor lists and then<br />

spend weeks trying to sell spurious marketing<br />

programs…anyone had a call from<br />

Alabama recently?<br />

The food could be a lot better. And<br />

what’s with Smart Booths? There seems<br />

to be a constant push to upsell exhibitors<br />

for a show that has seen dramatic declines<br />

in attendance in recent years, traffic for<br />

2006 was basically the same as 2005. Yes,<br />

we would vote for Vegas—better hotels,<br />

more fun and cheaper to fly to.<br />

Vegas or Bust!<br />

Chris Goodrich at DCC in Ivyland, Pa.<br />

weighed in on the side of Vegas:<br />

We love SEMICON West simply for the<br />

very efficient way logistics are handled.<br />

We hate SEMICON West for the stupid<br />

layout—second floor of Moscone Center<br />

West gets slim traffic. Also for the barrage<br />

of emails that start ten months ahead and<br />

Conclusion<br />

In five years, will we be fondly reminiscing<br />

about the “Good Ol’ Days,”<br />

when SEMICON West was in San<br />

Francisco, as the rat-a-tat-a-tat of a<br />

large slot machine liberating its treasure<br />

sounds off in the Vegas background?<br />

We don’t know, but stranger things<br />

have happened! ■<br />

Tessera Announces Wafer-Level Camera Technology<br />

San Jose—Tessera<br />

Technologies has<br />

announced OptiMC<br />

WLC,a new,waferlevel<br />

camera technology<br />

designed to<br />

advance the integration<br />

of miniaturized<br />

cameras in mobile<br />

phones, personal<br />

computers, security<br />

cameras and other<br />

electronics.<br />

The technology<br />

makes it possible to<br />

manufacture the<br />

camera module at the wafer level,<br />

reducing the size and total bill of<br />

materials.<br />

Tessera says its solution is designed<br />

to overcome the cost, size, and manufacturing<br />

roadblocks facing the industry<br />

as cameras become pervasive in electronics.<br />

Tessera’s OptiMC WLC camera module reduces the size of camera modules<br />

by up to half, the company says. (Tessera)<br />

The OptiML WLC reduces the size of<br />

the camera to a minimum, delivering<br />

up to 50 percent size reductions over<br />

camera modules used in current camera<br />

phones. Tessera will license the technology<br />

to the global electronics industry.<br />

[tessera.com]<br />

32<br />

<strong>Chip</strong> <strong>Scale</strong> <strong>Review</strong> ■ <strong>July</strong> <strong>2007</strong> ■ [<strong>Chip</strong><strong>Scale</strong><strong>Review</strong>.com]

INDUSTRY NEWS<br />

IWLPC Morning Panels Will Address Hot Topics in IC Packaging<br />

San Jose—Experts<br />

on two morning<br />

panels, one on<br />

INTERNATIONAL WAFER-LEVEL PACKAGING CONFERENCE<br />

Tuesday, Sep. 18 and<br />

one on Wednesday,<br />

Sep. 19, will tackle current trends in<br />

wafer-level packaging at the fourth<br />

Annual International Wafer-Level<br />

Packaging Conference.<br />

The Tuesday panel will address “The<br />

Business and Marketing of WLPs, ICs<br />

and Novel Devices.” Last year, this session<br />

attracted a standing-room only<br />

audience.<br />

Panelists are Larry<br />

Gilg of the Die<br />

Products Consortium;<br />

David Hays of Amkor<br />

Technology Inc.; Jan<br />

Vardaman of TechSearch<br />

International; and<br />

Jim Walker of<br />

Larry Gilg Gartner Dataquest.<br />

SA N JOSE, CALIFO R NIA<br />

S E P T E M B E R 1 7-1 9, 2 0 0 7<br />

Vardaman and<br />

Walker will address<br />

specific market<br />

trends from their<br />

viewpoints as industry<br />

analysts. Gilg and<br />

Hays bring “from the<br />

trenches” perspectives<br />

Joe Fjelstad to the program that<br />

begins at 8 a.m.<br />

Wednesday’s 8 a.m. opening session<br />

will focus on “WLP, 3D/Stacked and<br />

other Micro/Nano-<strong>Scale</strong> Packaging<br />

Strategies—Merging, Crashing or<br />

Complimenting?<br />

Panelists include Joe Fjelstad of<br />

SiliconPipe; Dr. Ken Gilleo of ET-Trends<br />

LLC and Paul Siblerud of SEMITOOL<br />

Inc. and the new EMC3D wafer-level<br />

interconnect consortium.<br />

The Conference begins on Sep. 17<br />

with five, half-day workshops presented<br />

by internationally known experts.<br />

INTRODUCING<br />

A New Material Solution for Key<br />

Microprocessor Test Socket Applications<br />

Piper Plastics’ ceramic-filled VICTREX ® PEEK grade<br />

(EPM-2204U-W) offers excellent dimensional stability and<br />

tolerance control across a broad range of temperature and<br />

humidity conditions, making it ideal for high performance<br />

test socket components. Competitive advantages include:<br />

On Sep. 18 and 19, the Conference<br />

will present two days of panels. In addition,<br />

a special keynote dinner will be held<br />