Energy harvesting: a thin film approach - EE Times Europe

Energy harvesting: a thin film approach - EE Times Europe

Energy harvesting: a thin film approach - EE Times Europe

Create successful ePaper yourself

Turn your PDF publications into a flip-book with our unique Google optimized e-Paper software.

CCD and CMOS features. They facilitate, however, the mitigation<br />

of each technology’s limitations as illustrated in the following<br />

sections.<br />

A true merge of CCD and CMOS<br />

A major advantage of epc’s BSI concept is the optical detectors’<br />

100% fill factor, independent of the numbers of transistors<br />

in the pixel. Looking at the common requirement of global<br />

shuttering, these advantages become evident. CMOS requires<br />

additional transistors in each pixel in order to realize global<br />

shuttering. This usually comes at a loss in fill factor with adverse<br />

effects on device responsivity. In the Espros Photonic CMOS<br />

process, shuttering is completely implemented in the charge<br />

domain and can be controlled in very short timeframes. What’s<br />

more, repetitive shuttering with frame-store functionality in dedicated<br />

frame buffers is also possible. However, the full CMOS<br />

analogue design features including high voltage transistors and<br />

<strong>EE</strong>PROM blocks remain available for the pixel architecture – all<br />

of which come with no compromise in the fill factor. Responsivity<br />

also benefits from the availability of low power high gain<br />

CMOS amplifiers. And the previously mentioned quantum<br />

efficiency advantage plays a vital supporting role in this respect<br />

by providing higher charges in the first place.<br />

Dealing with noise<br />

When dealing with noise performance, the most suitable design<br />

measures from both worlds can be applied in a complementary<br />

way. Traditionally, CMOS used to be much more prone to noise,<br />

not in the least due to restrictions resulting from limited real<br />

estate inside the pixel. Source follower geometries are limited<br />

by size and complex architectures such as multiple read out<br />

stages compromise the requirement to keep noise levels low.<br />

Although, one has to admit that with recent developments in<br />

CMOS process technology, the differences are dwindling. In<br />

a mixed-process environment, the design engineer can apply<br />

CCD pixel designs with all the noise advantages. In-pixel source<br />

followers do not suffer size restrictions due to BSI and CMOS<br />

readout and amplification stages can be deployed where they<br />

deliver the best performance (e.g. in high gain amplifiers). As a<br />

consequence, the dynamic range will benefit from the ability to<br />

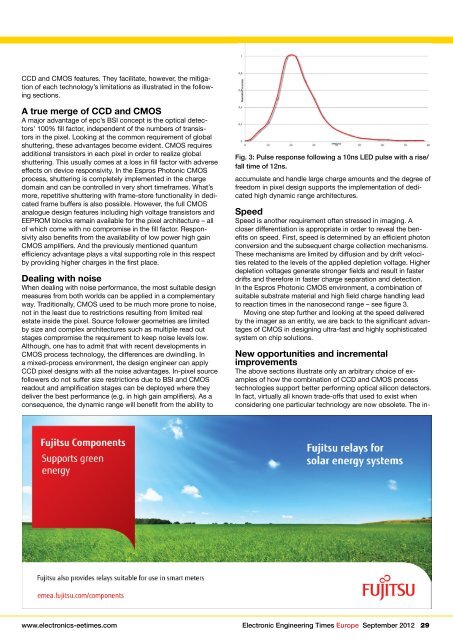

Fig. 3: Pulse response following a 10ns LED pulse with a rise/<br />

fall time of 12ns.<br />

accumulate and handle large charge amounts and the degree of<br />

freedom in pixel design supports the implementation of dedicated<br />

high dynamic range architectures.<br />

Speed<br />

Speed is another requirement often stressed in imaging. A<br />

closer differentiation is appropriate in order to reveal the benefits<br />

on speed. First, speed is determined by an efficient photon<br />

conversion and the subsequent charge collection mechanisms.<br />

These mechanisms are limited by diffusion and by drift velocities<br />

related to the levels of the applied depletion voltage. Higher<br />

depletion voltages generate stronger fields and result in faster<br />

drifts and therefore in faster charge separation and detection.<br />

In the Espros Photonic CMOS environment, a combination of<br />

suitable substrate material and high field charge handling lead<br />

to reaction times in the nanosecond range – see figure 3.<br />

Moving one step further and looking at the speed delivered<br />

by the imager as an entity, we are back to the significant advantages<br />

of CMOS in designing ultra-fast and highly sophisticated<br />

system on chip solutions.<br />

New opportunities and incremental<br />

improvements<br />

The above sections illustrate only an arbitrary choice of examples<br />

of how the combination of CCD and CMOS process<br />

technologies support better performing optical silicon detectors.<br />

In fact, virtually all known trade-offs that used to exist when<br />

considering one particular technology are now obsolete. The in-<br />

www.electronics-eetimes.com Electronic Engineering <strong>Times</strong> <strong>Europe</strong> September 2012 29