PCIE Validation Methodology

PCIE Validation Methodology

PCIE Validation Methodology

Create successful ePaper yourself

Turn your PDF publications into a flip-book with our unique Google optimized e-Paper software.

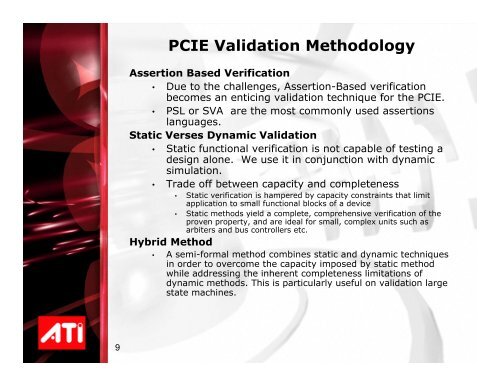

<strong>PCIE</strong> <strong>Validation</strong> <strong>Methodology</strong><br />

Assertion Based Verification<br />

• Due to the challenges, Assertion-Based verification<br />

becomes an enticing validation technique for the <strong>PCIE</strong>.<br />

• PSL or SVA are the most commonly used assertions<br />

languages.<br />

Static Verses Dynamic <strong>Validation</strong><br />

• Static functional verification is not capable of testing a<br />

design alone. We use it in conjunction with dynamic<br />

simulation.<br />

• Trade off between capacity and completeness<br />

• Static verification is hampered by capacity constraints that limit<br />

application to small functional blocks of a device<br />

• Static methods yield a complete, comprehensive verification of the<br />

proven property, and are ideal for small, complex units such as<br />

arbiters and bus controllers etc.<br />

Hybrid Method<br />

• A semi-formal method combines static and dynamic techniques<br />

in order to overcome the capacity imposed by static method<br />

while addressing the inherent completeness limitations of<br />

dynamic methods. This is particularly useful on validation large<br />

state machines.<br />

9