An Introduction to the Ericsson Transport Network Architecture ...

An Introduction to the Ericsson Transport Network Architecture ...

An Introduction to the Ericsson Transport Network Architecture ...

You also want an ePaper? Increase the reach of your titles

YUMPU automatically turns print PDFs into web optimized ePapers that Google loves.

86<br />

The control signals, which come from <strong>the</strong><br />

Vertical Control Board (VCB), are distributed<br />

<strong>to</strong> all SMBs. In addition, HCB collects<br />

external alarms, e.g. temperature, fans,<br />

etc.<br />

The VCB is <strong>the</strong> core of <strong>the</strong> control functions<br />

in <strong>the</strong> AXD 4/1. Packet handling and<br />

control of <strong>the</strong> Switch plane are <strong>the</strong> two<br />

main tasks performed by <strong>the</strong> VCB, which<br />

contains <strong>the</strong> Unit Processor (UP). The<br />

packet handling is performed by a Router.<br />

The Router continuously looks for a packet<br />

<strong>to</strong> be routed and keeps track of <strong>the</strong> packet<br />

load.<br />

The UP handles <strong>the</strong> control of <strong>the</strong> entire<br />

Switch plane by controlling <strong>the</strong> Device Processors<br />

(DP) located on <strong>the</strong> respective<br />

boards in <strong>the</strong> Switching Cabinet.<br />

The Distribution Matrix Board (DMB) terminates<br />

four incoming SNI-4s from Devices,<br />

and separates <strong>the</strong> traffic part of <strong>the</strong> signal<br />

from <strong>the</strong> control information carried in<br />

<strong>the</strong> internal overhead of <strong>the</strong> SNI-4. The<br />

traffic signals are distributed <strong>to</strong> all <strong>the</strong><br />

Switching Matrix Boards (SMB) in <strong>the</strong> cabinet.<br />

The VCB handles <strong>the</strong> separated control<br />

information for routing. One SWC can<br />

be equipped with up <strong>to</strong> sixteen DMBs.<br />

The SMB is <strong>the</strong> heart of <strong>the</strong> Switch. It contains<br />

<strong>the</strong> Switch for four outgoing SNI-4<br />

signals. In addition, four outputs used for<br />

expansion are located at <strong>the</strong> SMB. These<br />

ports are used <strong>to</strong> interconnect two SWCs<br />

when expanding <strong>the</strong> switch. Each SMB is<br />

connected <strong>to</strong> all DMBs in <strong>the</strong> cabinet. Up<br />

<strong>to</strong> sixteen SMBs can be accommodated in<br />

one SWC.<br />

Each board is equipped with a microprocessor<br />

for board supervision (DP).<br />

Devices<br />

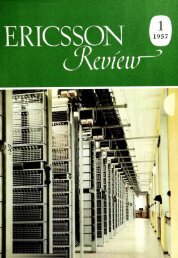

TAU 140, Figs. 6 and 7, interfaces<br />

140 Mbit/s plesiochronous line signals according<br />

<strong>to</strong> CCITT G.703. TAU 140 can be<br />

set <strong>to</strong> different modes, which allows for<br />

branching at 2, 34, and 140 Mbit/s level<br />

and makes switching at <strong>the</strong>se levels possible.<br />

TAU 140 contains five different types of<br />

ASIC. Toge<strong>the</strong>r <strong>the</strong>y handle CMI-decoding<br />

of 140 Mbit/s line signals, framing and<br />

maintenance at <strong>the</strong> 140,34,8 and 2 Mbit/s<br />

levels, buffering and frequency justification<br />

between line signals, synchronisation,<br />

generation of <strong>the</strong> synchronous IVC-4<br />

frame and sending of SNI-4 <strong>to</strong> all three<br />

switch planes. TAU 140 has <strong>the</strong> corresponding<br />

functionality in <strong>the</strong> transmit direction,<br />

completed with majority vote for data<br />

and clock signals from three switch planes.<br />

TAU 140 contains approximately 1.5 Million<br />

used gates, processor block with<br />

256 kWord-PROM, 512 kWord-RAM,<br />

DC/DC converters and a number of analog<br />

high speed blocks.<br />

TAU STM-1E interfaces 155 Mbit/s electric<br />

line signals belonging <strong>to</strong> <strong>the</strong> Synchronous<br />

Digital Hierarchy, and performs demap-<br />

Fig.6<br />

TAU 140<br />

ERICSSON REVIEW No. 3.1992