Part 4 JPL Chips - Eric Fossum

Part 4 JPL Chips - Eric Fossum

Part 4 JPL Chips - Eric Fossum

You also want an ePaper? Increase the reach of your titles

YUMPU automatically turns print PDFs into web optimized ePapers that Google loves.

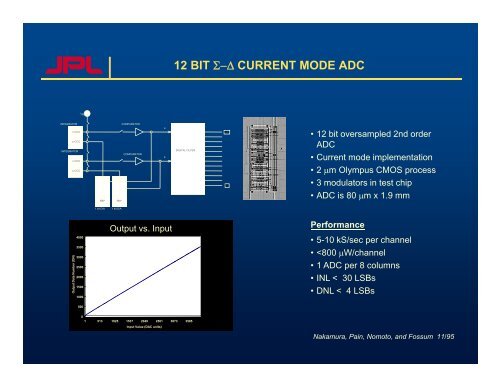

12 BIT Σ−Δ CURRENT MODE ADC<br />

I IN<br />

INTEGRATOR<br />

n-CCC<br />

p-CCC<br />

INTEGRATOR<br />

n-CCC<br />

COMPARATOR<br />

COMPARATOR<br />

a<br />

b<br />

DIGITAL FILTER<br />

D11<br />

• 12 bit oversampled 2nd order<br />

ADC<br />

• Current mode implementation<br />

p-CCC<br />

• 2 μm m Olympus CMOS process<br />

D0<br />

• 3 modulators in test chip<br />

I<br />

REF<br />

I<br />

REF<br />

• ADC is 80 μm x 1.9 mm<br />

1 bit D/A 1 bit D/A<br />

er (DN)<br />

Output Data Numb<br />

4000<br />

3500<br />

3000<br />

2500<br />

2000<br />

1500<br />

1000<br />

Output vs. Input<br />

Performance<br />

• 5-10 kS/sec per channel<br />

•