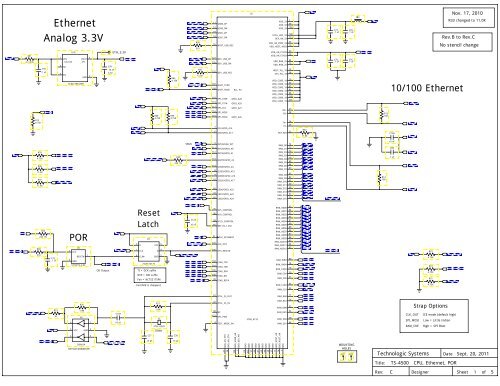

TS-4500 Schematic Revision C - Technologic Systems

TS-4500 Schematic Revision C - Technologic Systems

TS-4500 Schematic Revision C - Technologic Systems

You also want an ePaper? Increase the reach of your titles

YUMPU automatically turns print PDFs into web optimized ePapers that Google loves.

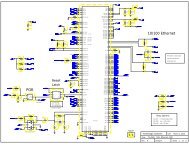

POWER<br />

R91<br />

4.7 ohm<br />

R72<br />

4.75K<br />

Ethernet<br />

Analog 3.3V<br />

C92<br />

.1 uF<br />

32KHZ<br />

U16<br />

3<br />

1 VIN<br />

VOUT<br />

5<br />

1.8-6.0V 2%<br />

XC6221B332MR<br />

GND<br />

2<br />

ETH_3.3V<br />

ETH_3.3V<br />

C28<br />

10 uF<br />

6.3V<br />

3.3V<br />

TW_CLK<br />

TW_DAT<br />

3.3V<br />

DEBUG_RXD<br />

R68<br />

4.75K<br />

R63<br />

4.75K<br />

R69<br />

4.75K<br />

HOSTA_USB_P<br />

HOSTA_USB_M<br />

HOSTB_USB_P<br />

HOSTB_USB_M<br />

R38<br />

510<br />

DEV_USB_P<br />

DEV_USB_M<br />

R45<br />

12.0K<br />

DEBUG_TXD<br />

GPIO_A28<br />

GPIO_A29<br />

CPU_SPI_CLK<br />

CPU_SPI_MOSI<br />

CPU_SPI_MISO<br />

11 USB0_DP<br />

12 USB0_DM<br />

19 USB1_DP<br />

18 USB1_DM<br />

16 HOST_USB_RES<br />

127 DEV_USB_DP<br />

126 DEV_USB_DM<br />

125 DEV_USB_RES<br />

107 UART_TXD0<br />

108 UART_RXD0 Res. PU<br />

118<br />

119<br />

SPI_CS0#<br />

SPI_CS1#<br />

GPIO_A28<br />

GPIO_A29<br />

117 SPI_CLK GPIO_A27<br />

116 SPI_MOSI<br />

115 SPI_MISO GPIO_A26<br />

7 SCL/GPIO_A14<br />

6 SDA/GPIO_A13<br />

U2<br />

2<br />

39<br />

103<br />

128<br />

123<br />

33<br />

13<br />

23<br />

29<br />

64<br />

75<br />

15<br />

38<br />

20<br />

32<br />

47<br />

82<br />

98<br />

109<br />

121<br />

27<br />

28<br />

24<br />

25<br />

22<br />

R32<br />

11.5K<br />

3.3V<br />

2.5V<br />

1.8V<br />

C77<br />

.1 uF<br />

C75<br />

.1 uF<br />

C78<br />

.1 uF<br />

C76<br />

.1 uF<br />

FB3<br />

ETH_3.3V<br />

3.3V<br />

R13<br />

100<br />

10/100 Ethernet<br />

C104<br />

ETH_RX+<br />

VDD_33<br />

VDD_33<br />

VDD_33<br />

VCCA_U2O_33<br />

DEV_AN_33<br />

VDD_AN_POW_33<br />

VDD_HOST_AN33<br />

VDD_AN_ETH33<br />

VDD_AN_ETH33<br />

VDD_RAM_25<br />

VDD_RAM_25<br />

HOST_PLL_18<br />

SYS_PLL_18<br />

VDD_CORE_18<br />

VDD_CORE_18<br />

VDD_CORE_18<br />

VDD_CORE_18<br />

VDD_CORE_18<br />

VDD_CORE_18<br />

VDD_CORE_18<br />

RX+<br />

RX-<br />

TX+<br />

TX-<br />

REF_RES<br />

ETH_RX-<br />

ETH_CT<br />

Nov. 17, 2010<br />

R33 changed to 11.0K<br />

Rev.B to Rev.C<br />

No stencil change<br />

3.3V<br />

EXT_RESET#<br />

3.3V<br />

R70<br />

4.75K<br />

R36<br />

11.5K<br />

R37<br />

11.5K<br />

R39<br />

510<br />

FPGA_25MHZ<br />

R23<br />

226 1%<br />

3.3V<br />

C72<br />

.1 uF<br />

R19<br />

30<br />

CPU_JTAG_TCK<br />

CPU_JTAG_TMS<br />

CPU_JTAG_TDI<br />

POR<br />

2 VCC<br />

1<br />

RESET#<br />

3 GND<br />

6<br />

5<br />

VCC<br />

U5<br />

ST1001S-2.9V<br />

R26<br />

1.0M<br />

U9<br />

GND<br />

1<br />

2<br />

3.3V<br />

UN-RESET<br />

LOW_VOLT#<br />

OD Output<br />

C103<br />

10 nF<br />

FPGA_JTAG_TCK<br />

Reset<br />

Latch<br />

U3<br />

6 CLR# GND<br />

2<br />

3 D<br />

VCC<br />

5<br />

1 CLK<br />

Q<br />

4<br />

74LVC1G175<br />

TI = DCK suffix<br />

NXP = GW suffix<br />

Fair = NC7SZ175P6<br />

Fairchild is cheapest<br />

R27<br />

1.0M<br />

Y2<br />

XTAL-HC49<br />

25MHz<br />

VBUS INT28<br />

GPIO_A0<br />

GPIO_A1<br />

R20<br />

226 1%<br />

GPIO_A3<br />

GPIO_A15<br />

GPIO_A16<br />

GPIO_A17<br />

GPIO_A22<br />

GPIO_A23<br />

FPGA_JTAG_TDO<br />

CONTROL_25<br />

1.2V<br />

C122<br />

10 nF<br />

32KHZ<br />

CPU_CLKOUT<br />

OFF_BD_RESET#<br />

CPU_JTAG_TCK<br />

CPU_JTAG_TMS<br />

CPU_JTAG_TDI<br />

CPU_JTAG_TDO<br />

LOW_VOLT#<br />

5 INT28/USB_INT<br />

RAM_D0<br />

74<br />

111 INT29/GPIO_A0<br />

RAM_D1<br />

73<br />

72<br />

112 RAM_D2<br />

INT30/GPIO_A1<br />

71<br />

RAM_D3<br />

70<br />

113 RAM_D4<br />

UART0/GPIO_A2<br />

69<br />

RAM_D5<br />

68<br />

114 RAM_D6<br />

I2SDR/GPIO_A3<br />

67<br />

RAM_D7<br />

8 I2SSD/GPIO_A15<br />

63<br />

9 RAM_D8<br />

I2SWS/GPIO_A16<br />

62<br />

RAM_D9<br />

10 I2SCK/GPIO_A17<br />

61<br />

RAM_D10<br />

76<br />

RAM_BA1<br />

42 XTAL_25_IN<br />

RAM_D11<br />

60<br />

59<br />

43 RAM_D12<br />

LED0/GPIO_A22<br />

58<br />

RAM_D13<br />

44 LED1/GPIO_A23<br />

57<br />

RAM_D14<br />

80<br />

RAM_WR#<br />

104 JTAG_TCK<br />

78<br />

RAM_RAS#<br />

101 JTAG_TMS<br />

79<br />

RAM_CAS#<br />

105 JTAG_DIN<br />

50<br />

100<br />

RAM_CS#<br />

45 LED2/GPIO_A24<br />

RAM_D15<br />

56<br />

35<br />

RAM_ADD0<br />

95<br />

V25_CONTROL<br />

RAM_ADD1<br />

94<br />

36 V18_CONTROL RAM_ADD2<br />

93<br />

RAM_ADD3<br />

92<br />

34 V125_CONTROL<br />

RAM_ADD4<br />

91<br />

90<br />

66 RAM_ADD5<br />

REF_IN_1.25V<br />

89<br />

RAM_ADD6<br />

JTAG_DO<br />

JTAG_RST#<br />

99<br />

RAM_CKE<br />

51<br />

RAM_ADD7<br />

88<br />

31<br />

RAM_ADD8<br />

87<br />

CLK_32768KHZ<br />

RAM_ADD9<br />

86<br />

120 CLK_OUT<br />

84<br />

RAM_ADD11<br />

RAM_ADD10<br />

85<br />

106<br />

83<br />

RAM_ADD12<br />

SYS_RESET#<br />

RAM_CLK#<br />

52<br />

RAM_CLK<br />

53<br />

41 XTAL_25_OUT<br />

RAM_BA0<br />

77<br />

RAM_DM0<br />

55<br />

30 NC<br />

RAM_DM1<br />

54<br />

122 VFS_PGM<br />

STAR_8132<br />

RAM_QS0<br />

49<br />

4 TEST_MODE_EN<br />

RAM_QS1<br />

48<br />

DATA_00<br />

DATA_01<br />

DATA_02<br />

DATA_03<br />

DATA_04<br />

DATA_05<br />

DATA_06<br />

DATA_07<br />

DATA_08<br />

DATA_09<br />

DATA_10<br />

DATA_11<br />

DATA_12<br />

DATA_13<br />

DATA_14<br />

DATA_15<br />

ADD_00<br />

ADD_01<br />

ADD_02<br />

ADD_03<br />

ADD_04<br />

ADD_05<br />

ADD_06<br />

ADD_07<br />

ADD_08<br />

ADD_09<br />

ADD_10<br />

ADD_11<br />

ADD_12<br />

RAM_WR#<br />

RAM_RAS#<br />

RAM_CAS#<br />

RAM_CS#<br />

RAM_CKE<br />

RAM_CLK#<br />

RAM_CLK<br />

RAM_BA0<br />

RAM_BA1<br />

RAM_DM0<br />

RAM_DM1<br />

RAM_QS0<br />

RAM_QS1<br />

DATA_[00:15]<br />

ADD_[00:12]<br />

R14<br />

100<br />

10 nF<br />

C89<br />

.1 uF<br />

ETH_CT<br />

ETH_TX+<br />

ETH_TX-<br />

R73<br />

3.3V<br />

CPU_CLKOUT<br />

4.75K<br />

R74<br />

CPU_SPI_MOSI<br />

4.75K<br />

R75<br />

UN-RESET<br />

4.75K<br />

Strap Options<br />

CLK_OUT ICE mode (default high)<br />

SPI_MOSI Low = Little Indian<br />

RAM_CKE High = SPI Boot<br />

SD_POWER#<br />

4<br />

3<br />

DUAL04<br />

SN74LVC2G04DCKR<br />

EN_SD_POWER<br />

C37<br />

15 pF<br />

C38<br />

15 pF<br />

21 GND_AN_ETH<br />

26 GND_AN_ETH<br />

124 GND_USBD_AN<br />

1 GND_DEV_AN<br />

110 GND<br />

102 GND<br />

97 GND<br />

96 GND<br />

81 GND<br />

65 GND<br />

46 GND<br />

40 GND<br />

37 GND<br />

17 GND_HOST_AN<br />

14 GND_HOST_AN<br />

3 GND<br />

MOUNTING<br />

HOLES<br />

MT1<br />

MT2<br />

<strong>Technologic</strong> <strong>Systems</strong><br />

Date<br />

Sept. 20, 2011<br />

Title:<br />

<strong>TS</strong>-<strong>4500</strong> CPU, Ethernet, POR<br />

Rev: C Designer Sheet 1 of<br />

5

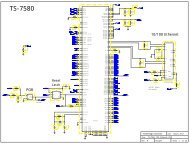

Boot Straps<br />

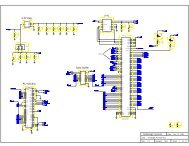

FPGA with 5000 LUTs<br />

XP2-5 has:<br />

5K LU<strong>TS</strong> 2 PLLs<br />

9 blocks of 1Kx18 Block RAM<br />

12 18x18 Multipliers<br />

100 I/O with 144 pin package<br />

"instant ON" = about 1.5 mS<br />

input PLL clock = 10 MHz min<br />

Mode 1 Mode 2 Boots from<br />

R56<br />

3.3V<br />

1 1 NAND Flash<br />

1 0<br />

SD Card<br />

Pins 87 and 88 must be read<br />

prior to UN-RESET being pulsed<br />

2.00K<br />

R34<br />

11.5K<br />

R35<br />

11.5K<br />

0 1<br />

0 0<br />

MODE1 and MODE2 states<br />

and Board ID bits<br />

must be latched prior to<br />

UN_RESET# pulsed<br />

Off-board Flash<br />

Off-board Flash<br />

MODE1 and MODE2<br />

have PU resistors<br />

Use 1K ohm resistor<br />

to GND to set low<br />

Differences from <strong>TS</strong>-7500/7550/7551/7552<br />

ETH LEDs are inverted<br />

Console path not used<br />

<strong>TS</strong>-7500<br />

<strong>TS</strong>-7550<br />

WM-7551<br />

<strong>TS</strong>-7552<br />

<strong>TS</strong>-<strong>4500</strong><br />

Board ID bits<br />

Pin 54 Pin 138<br />

(weak PU)<br />

(weak PD)<br />

1 1<br />

1 1<br />

0 0<br />

1 0<br />

0 0<br />

Pin 71<br />

1<br />

0<br />

1<br />

1<br />

0<br />

Pin 37<br />

<strong>TS</strong>-7553 1 0 0<br />

1<br />

<strong>TS</strong>-7554 0 0 0<br />

1<br />

<strong>TS</strong>-7555 0 1 0<br />

1<br />

1<br />

1<br />

1<br />

1<br />

0<br />

Pins 54 and 138 must be read<br />

prior to UN-RESET being pulsed<br />

Hex<br />

F<br />

B<br />

C<br />

D<br />

9<br />

8<br />

A<br />

0<br />

GPIO_A22<br />

LED0<br />

FPGA_JTAG_TMS<br />

FPGA_JTAG_TDI<br />

GPIO_A23<br />

LED1<br />

LED0 shows both<br />

Activity and Link<br />

R21<br />

226 1%<br />

R22<br />

226 1%<br />

FPGA_JTAG_TDO<br />

FPGA_JTAG_TDI<br />

FPGA_JTAG_TCK<br />

DIO_50<br />

DIO_49<br />

DIO_19<br />

CPU_SPI_CLK<br />

CPU_SPI_MOSI<br />

CPU_SPI_MISO<br />

GPIO_A0<br />

Interrupts<br />

GPIO_A1<br />

SPI_CS0# GPIO_A28<br />

SPI_CS1# GPIO_A29<br />

GPIO_A3<br />

GPIO_A15<br />

I2S<br />

GPIO_A16<br />

GPIO_A17<br />

INT28<br />

DIO_36<br />

DIO_37<br />

DIO_38<br />

DIO_39<br />

DIO_22<br />

DIO_44<br />

DIO_45<br />

DIO_46<br />

DIO_47<br />

DIO_40<br />

DIO_41<br />

DIO_42<br />

FPGA_25MHZ<br />

DIO_51<br />

R55<br />

2.00K<br />

R64<br />

3.3V<br />

4.75K<br />

37 IO<br />

13 OUT_CSSPIN<br />

46 IO<br />

28 91<br />

136 122<br />

IO_CLK CLK+<br />

IO<br />

DIO_23<br />

3.3V<br />

VCCO_0<br />

IO<br />

128 29<br />

VCCO_0<br />

IO<br />

15 133<br />

IO IO<br />

SPI_CLK<br />

30 99<br />

IO_CLK CLK-<br />

IO<br />

DIO_48 SPI_CS#<br />

112 129<br />

VCCO_1<br />

IO<br />

39 93<br />

IO<br />

IO<br />

SPI_MISO<br />

102<br />

IO<br />

137 58<br />

IO IO_CLK<br />

SPI_MOSI<br />

95 19<br />

VCCO_2<br />

IO<br />

96<br />

78 IP<br />

DIO_00<br />

DIO_[00:49]<br />

105 98<br />

VCCO_2<br />

IO<br />

IO_CLK<br />

17 104<br />

IO<br />

IO<br />

DIO_01<br />

120<br />

32 IO_CLK<br />

IO<br />

16<br />

IO_CCLK<br />

DIO_02<br />

76 VCCO_3<br />

27 21<br />

IO<br />

IO_CLK<br />

100<br />

IO<br />

DIO_03<br />

36<br />

IO<br />

38 63 IO<br />

VCCO_4<br />

35<br />

IO<br />

40 IO<br />

101<br />

IO<br />

DIO_04<br />

90 42 31<br />

IO<br />

VCCO_5<br />

IO<br />

103<br />

IO<br />

DIO_05<br />

7 49 22<br />

IN_PROGRAM#<br />

VCCO_5<br />

IO_CLK<br />

107<br />

IO<br />

DIO_06<br />

20<br />

IO_INIT#<br />

9 108<br />

IN_CFG1<br />

IO<br />

DIO_35<br />

33 44<br />

VCCO_6<br />

IO<br />

72 IO<br />

110<br />

IO<br />

DIO_08<br />

50 IO<br />

109<br />

IO<br />

DIO_09<br />

4 VCCO_7<br />

94 IO<br />

113<br />

124<br />

IO<br />

DIO_10<br />

14 VCCO_7<br />

IO<br />

114<br />

52<br />

IO_CLK<br />

DIO_11<br />

IO<br />

123 IO<br />

66<br />

IO<br />

56 IO_CLK<br />

115<br />

IO<br />

DIO_12<br />

11 IN_CSSPIS<br />

116<br />

5<br />

IO_CLK<br />

DIO_13<br />

IO<br />

57 23 IO<br />

VCC_AUX1<br />

119<br />

6<br />

IO_CLK<br />

DIO_14<br />

IO<br />

60 VCC_AUX2<br />

45<br />

8<br />

IO<br />

DIO_17<br />

IO_DONE<br />

85 VCC_AUX3<br />

1 10<br />

IO IO<br />

132<br />

117<br />

IO<br />

VCC_AUX4<br />

2<br />

ETH_LEFT_LED<br />

IO<br />

73<br />

142<br />

IO<br />

IO<br />

141<br />

ETH_RIGHT_LED<br />

IO<br />

89<br />

143<br />

IO<br />

IO<br />

125 83 IO<br />

77<br />

SDCARD_CMD<br />

VCC_JTAG<br />

62<br />

IO_CLK<br />

R18<br />

IO_CLK<br />

SDCARD_CLK<br />

121<br />

30<br />

IO<br />

SDCARD_D0<br />

140 VCC_PLL_0<br />

65 70<br />

IO<br />

IO<br />

SDCARD_D1<br />

67 VCC_PLL_1<br />

69<br />

IO<br />

SDCARD_D2<br />

144 18<br />

IO<br />

IO<br />

134<br />

IO<br />

SDCARD_D3<br />

43<br />

IO<br />

71 130<br />

IO IO<br />

61<br />

IO_CLK<br />

DIO_20<br />

24 55<br />

1.2V<br />

VCC_INT1<br />

IO<br />

54<br />

IO<br />

59 VCC_INT2<br />

92<br />

53<br />

IO<br />

RTC_SDA<br />

IO<br />

84 VCC_INT3<br />

26 127<br />

R52<br />

48<br />

CFG0 IO<br />

RTC_SCL<br />

IO<br />

2.00K<br />

118 VCC_INT4<br />

25 138<br />

47<br />

TOE<br />

IO<br />

DIO_21<br />

IO<br />

82 JTAG_DOUT<br />

80 JTAG_DIN<br />

81 JTAG_CLK<br />

IO_CLK<br />

IO_CLK<br />

IO<br />

88<br />

87<br />

74<br />

U8<br />

LATTICE_XP2_144<br />

DIO_24<br />

R53<br />

2.00K<br />

DIO_26<br />

DIO_25<br />

MODE1<br />

MODE2<br />

IO<br />

131<br />

DIO_43<br />

UN-RESET<br />

EXT_RESET#<br />

EN_SD_POWER<br />

DIO_07<br />

DIO_16<br />

DIO_15<br />

NAND_RD#<br />

NAND_WR#<br />

NAND_ALE<br />

NAND_CLE<br />

NAND_CS#<br />

NAND_BUSY#<br />

DIO_52<br />

NAND_D0<br />

NAND_D1<br />

NAND_D2<br />

NAND_D3<br />

NAND_D4<br />

NAND_D5<br />

NAND_D6<br />

NAND_D7<br />

DIO_27<br />

DIO_28<br />

DIO_29<br />

DIO_30<br />

DIO_31<br />

DIO_32<br />

DIO_33<br />

DIO_34<br />

DIO_18<br />

GREEN_LED#<br />

RED_LED#<br />

EXT_RESET# must<br />

be Open Drain<br />

used for WD reset<br />

NAND_D[0:7]<br />

FPGA_JTAG_TMS<br />

79 JTAG_TMS<br />

7552 and 7553 FPGA pin 93 = MISO<br />

R65<br />

4.75K<br />

R66<br />

4.75K<br />

R67<br />

4.75K<br />

3 GND1<br />

12 GND2<br />

34 GND3<br />

41 GND4<br />

51 GND5<br />

64 GND6<br />

68 GND7<br />

75 GND8<br />

86 GND9<br />

97 GND10<br />

106 GND11<br />

111 GND12<br />

126 GND13<br />

135 GND14<br />

139 GND15<br />

3.3V<br />

UN-RESET rising edge, deasserts CPU Reset<br />

(Must be careful at start up)<br />

It has a PD resistor -- always idle low<br />

EN_SD_POWER should initialize high<br />

During JTAG Flash programming<br />

the PROGRAM# pin should be high<br />

else it can inhibit Flash --> SRAM<br />

DONE likewise must be high<br />

These do have weak PU resistors<br />

Set CONFIG_MODE to NONE<br />

This allows all pins to be used<br />

Pull-up and pull-down resistors<br />

are 6 to 30K ohms<br />

PROGRAM#, DONE, and INIT# are<br />

dedicated configuration pins when<br />

CFG0 is low. When CFG0 is high<br />

they are "general purpose I/O"<br />

Page 4 of TN1141<br />

Page 37 of Data Sheet (Hot Socketing)<br />

Power Supplies can be sequenced in any order<br />

but must be monotonic<br />

All I/O lines are tri-stated during power cycling<br />

<strong>Technologic</strong> <strong>Systems</strong><br />

Date Sept. 20, 2011<br />

Title: <strong>TS</strong>-<strong>4500</strong> FPGA<br />

Rev: C Designer RLM Sheet 2 of 5

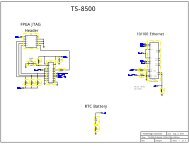

Micro SD Card Socket<br />

SDCARD_D0<br />

SDCARD_D1<br />

SDCARD_D2<br />

SDCARD_D3<br />

SDCARD_CMD<br />

SDCARD_CLK<br />

SD_POWER#<br />

3 COMMAND<br />

FRM1<br />

9<br />

7 DATA_0<br />

VDD<br />

4<br />

8 DATA_1<br />

1 DATA_2<br />

2<br />

6<br />

GND<br />

DATA_3<br />

5 CLK<br />

R46<br />

12.0K<br />

CN7<br />

CONN_MICRO_SD<br />

3.3V<br />

FRM2<br />

FRM3<br />

FRM4<br />

512 Mbyte<br />

NAND Flash<br />

1<br />

C49<br />

G<br />

.1 uF<br />

10<br />

11<br />

12<br />

2<br />

3<br />

S<br />

D<br />

C67<br />

DMP2305<br />

Q1<br />

C48<br />

.1 uF<br />

R54<br />

2.00K<br />

SDCARD_3.3V<br />

ADD_[00:12]<br />

ADD_00<br />

ADD_01<br />

ADD_02<br />

ADD_03<br />

ADD_04<br />

ADD_05<br />

ADD_06<br />

ADD_07<br />

ADD_08<br />

ADD_09<br />

ADD_10<br />

ADD_11<br />

ADD_12<br />

RAM_CKE<br />

2.5V<br />

RAM_CLK#<br />

R51<br />

2.00K<br />

1.2V<br />

R15<br />

100<br />

64 Mbyte<br />

DDR1 SDRAM<br />

C82<br />

.1 uF<br />

RAM_BA0<br />

RAM_BA1<br />

RAM_DM0<br />

RAM_DM1<br />

RAM_RAS#<br />

RAM_CAS#<br />

RAM_WR#<br />

RAM_CS#<br />

U10<br />

49 1<br />

VREF VCCINT<br />

19 18<br />

DNU VCCINT<br />

50 33<br />

DNU VCCINT<br />

14 3<br />

NC VCCIO<br />

53 9<br />

NC VCCIO 55<br />

VCCIO 61<br />

VCCIO<br />

15<br />

VCCIO<br />

29 A0<br />

30 A1<br />

31 25<br />

A2<br />

NC<br />

32 43<br />

A3<br />

NC<br />

35 A4<br />

36 A5<br />

37 16<br />

A6<br />

LDQS<br />

38 A7<br />

39 51<br />

A8<br />

UDQS<br />

40 A9<br />

28 A10<br />

41 A11<br />

42 2<br />

A12<br />

DQ0<br />

17 4<br />

NC/A13 DQ1 5<br />

DQ2 7<br />

DQ3<br />

26 8<br />

BA0<br />

DQ4 10<br />

DQ5<br />

27 11<br />

BA1<br />

DQ6 13<br />

DQ7<br />

20 LDM<br />

47 54<br />

UDM<br />

DQ8 56<br />

DQ9 57<br />

DQ10 59<br />

DQ11<br />

23 60<br />

RAS# DQ12 62<br />

DQ13<br />

22 63<br />

CAS# DQ14 65<br />

DQ15<br />

21 WE#<br />

6<br />

GNDIO<br />

44 12<br />

CKE<br />

GNDIO<br />

52<br />

GNDIO 58<br />

GNDIO<br />

46 64<br />

CLK# GNDIO<br />

45<br />

CLK<br />

34<br />

GND 48<br />

GND<br />

24 66<br />

CS# GND<br />

C120<br />

10 nF<br />

R11<br />

100<br />

C61<br />

.1 uF<br />

R12<br />

100<br />

C62<br />

.1 uF<br />

1.2V<br />

RAM_QS0<br />

RAM_QS1<br />

C63<br />

.1 uF<br />

C64<br />

.1 uF<br />

DATA_07<br />

DATA_06<br />

DATA_05<br />

DATA_04<br />

DATA_03<br />

DATA_02<br />

DATA_01<br />

DATA_00<br />

DATA_08<br />

DATA_09<br />

DATA_10<br />

DATA_11<br />

DATA_12<br />

DATA_13<br />

DATA_14<br />

DATA_15<br />

C65<br />

.1 uF<br />

DATA_[00:15]<br />

C66<br />

.1 uF<br />

2.5V<br />

.1 uF<br />

RAM_CLK<br />

DDR1_RAM<br />

NAND_RD#<br />

NAND_WR#<br />

NAND_CS#<br />

NAND_ALE<br />

NAND_CLE<br />

NAND_BUSY#<br />

OFF_BD_RESET#<br />

R71<br />

3.3V<br />

4.75K<br />

U13<br />

12<br />

VCC1<br />

37<br />

8 VCC2<br />

RD#<br />

29<br />

18 D0<br />

WR#<br />

30<br />

D1<br />

31<br />

9 D2<br />

CS#<br />

32<br />

D3<br />

17 ALE<br />

41<br />

D4<br />

16 42<br />

CMD D5<br />

43<br />

D6<br />

7 BUSY# 44<br />

D7<br />

6<br />

GND1<br />

19 13<br />

WP# GND2 36<br />

GND3<br />

NAND_FLASH2<br />

3.3V<br />

NAND_D[0:7]<br />

NAND_D0<br />

NAND_D1<br />

NAND_D2<br />

NAND_D3<br />

NAND_D4<br />

NAND_D5<br />

NAND_D6<br />

NAND_D7<br />

DDR RAM Notes<br />

The DDR clock differential pair is the most critical trace on the entire board<br />

The data lines in each byte lane can be swapped on the RAM chip for optimal layout<br />

Example: D0 and D5 can be swapped, but not D7 and D8<br />

The trace length of each data line (in a single byte lane) and the respective<br />

QS and DM signals must be matched to within 2.5 mm<br />

Address and Command signals can be grouped together, but must be isolated<br />

from data and M_DSQ and M_DM signals (by at least .5 mm)<br />

Or run them on different layer<br />

3.3V<br />

R60<br />

4.75K<br />

R61<br />

4.75K<br />

RTC<br />

U12<br />

RTC_SCL<br />

RTC_SDA<br />

Y1<br />

1 4<br />

6 SCL<br />

8<br />

VCC<br />

5 SDA<br />

7 OUT<br />

3<br />

BAT<br />

1 XIN<br />

2 4<br />

XOUT GND<br />

3.3V<br />

C83<br />

.1 uF<br />

V_BAT<br />

12 pF<br />

2 3<br />

XTAL_SMT_8X3<br />

M41T00S<br />

Maxim has RTC<br />

with same pin-out<br />

<strong>Technologic</strong> <strong>Systems</strong><br />

Date<br />

Sept. 20, 2011<br />

728-1005-2-ND<br />

12.5 pF Xtal<br />

Title: <strong>TS</strong>-<strong>4500</strong> RAM, RTC, Flash, SD socket<br />

Rev: C Designer Sheet 3 of<br />

5

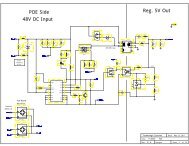

3.3V Power Supply up to 1000 mA<br />

POWER<br />

C50<br />

.1 uF<br />

FB1<br />

10 uF<br />

6.3V<br />

C20<br />

U6<br />

6 EN PGND<br />

2<br />

5 VIN<br />

SW<br />

3<br />

4 PIN<br />

0.8V FB<br />

1<br />

AGND<br />

L1<br />

COIL3.3UH<br />

R82<br />

15K<br />

3.32V nominal<br />

10 uF<br />

6.3V<br />

C21<br />

10 uF<br />

6.3V<br />

C22<br />

C70<br />

.1 uF<br />

C71<br />

.1 uF<br />

C100<br />

10 nF<br />

C101<br />

10 nF<br />

3.3V<br />

C102<br />

10 nF<br />

3.3V<br />

C56<br />

.1 uF<br />

C57<br />

.1 uF<br />

C58<br />

.1 uF<br />

C59<br />

.1 uF<br />

C114<br />

10 nF<br />

C116<br />

10 nF<br />

C119<br />

10 nF<br />

POWER<br />

C90<br />

.1 uF<br />

C91<br />

.1 uF<br />

FAN2002<br />

7<br />

DFN package<br />

R62<br />

4.75K<br />

3.3V<br />

Needs 320 mV headroom at<br />

L1 = LQH44PN3R3<br />

300 mA load - Room temp<br />

Max. current = 1.7 Amps<br />

C79<br />

.1 uF<br />

C84<br />

.1 uF<br />

C85<br />

.1 uF<br />

C86<br />

.1 uF<br />

C87<br />

.1 uF<br />

C88<br />

.1 uF<br />

C112<br />

C113<br />

C121<br />

C124<br />

C105<br />

10 nF<br />

10 nF<br />

10 nF<br />

10 nF<br />

10 nF<br />

LOW_VOLT#<br />

2<br />

1<br />

3.3V<br />

U14<br />

VCC<br />

GND<br />

5<br />

4<br />

3<br />

R50<br />

2.00K<br />

3.3V<br />

1.2V Regulator<br />

Measured 57 mA with<br />

R47<br />

12.0K<br />

R84<br />

15K<br />

1.8V<br />

200 mA max load<br />

400 mV drop out<br />

25 uS Turn-on<br />

LDO<br />

4 ECO<br />

EN<br />

2% FT<br />

3% LP<br />

U11<br />

3<br />

1 VIN<br />

VOUT<br />

5<br />

1.5-6.0V 1.20V<br />

Low = LP<br />

NCP584-1.2V<br />

GND<br />

2<br />

C27<br />

FPGA 2K LUTs running<br />

10 uF<br />

R41<br />

0.20<br />

C74<br />

.1 uF<br />

C51<br />

.1 uF<br />

C117<br />

10 nF<br />

1.2V<br />

1.2V<br />

C73<br />

.1 uF C106 C107<br />

10 nF 10 nF<br />

C108<br />

10 nF<br />

Temp Sensor<br />

4 2<br />

SCL<br />

U4<br />

TW_CLK<br />

GND<br />

5 ALERT VCC<br />

3<br />

TW_DAT<br />

6<br />

1<br />

ADD<br />

SDA<br />

LM73<br />

LM73CIMK-0<br />

3.3V<br />

Zero suffix has<br />

address at 100 1001<br />

Best to Reset after<br />

all power cycles<br />

Set PD bit, Wait 50 mS<br />

Then clear PD bit<br />

NC7SZ125<br />

2.5V Regulator<br />

1.8V Regulator<br />

3.3V<br />

R98<br />

1 ohm<br />

POWER<br />

C68<br />

FB2<br />

.1 uF<br />

C23<br />

10 uF<br />

U7<br />

6 EN PGND<br />

2<br />

5 VIN<br />

SW<br />

3<br />

4 PIN<br />

0.8V FB<br />

1<br />

AGND<br />

L2<br />

COIL3.3UH<br />

C24<br />

10 uF<br />

1.84V nominal<br />

C25<br />

10 uF<br />

R83<br />

15K<br />

C80<br />

.1 uF<br />

C81<br />

.1 uF<br />

C109<br />

10 nF<br />

C110<br />

10 nF<br />

C111<br />

10 nF<br />

C53<br />

.1 uF<br />

Measured 420 mA load<br />

C54<br />

.1 uF<br />

C55<br />

.1 uF<br />

C115<br />

10 nF<br />

1.8V<br />

CONTROL_25<br />

R10<br />

100<br />

1<br />

2<br />

3<br />

Q2<br />

C26<br />

10 uF<br />

C69<br />

.1 uF<br />

Est. 100 mA load<br />

C52<br />

.1 uF<br />

C118<br />

10 nF<br />

C60<br />

.1 uF<br />

2.5V<br />

3.3V<br />

R31<br />

11.5K<br />

FAN2002<br />

DFN package<br />

7<br />

R42<br />

0.20<br />

FAN2002<br />

R33<br />

11.0K<br />

10uF 6.3V = PCC2225TR-ND -- 4 cents<br />

1.3 MHz freq. 50 uA quiescent<br />

Vout = 800mV * [1+ Rtop/Rbot]<br />

> 90% eff. at 100-400 mA load<br />

1000 mA max load<br />

0805 package<br />

<strong>Technologic</strong> <strong>Systems</strong><br />

Date Sept. 20, 2011<br />

Title: <strong>TS</strong>-<strong>4500</strong> Power Supplies, Temp Sensor<br />

Rev: C Designer RLM Sheet 4 of<br />

5

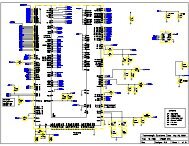

Two 100-pin Off-board Connectors<br />

"POWER" pins supply all power to the module<br />

Apply 3.8V to 5.5V to these pins<br />

EXT_RESET# is an Input<br />

used to reboot the CPU<br />

Current drain is approximately 400 mA<br />

(less than 2 Watts)<br />

Left<br />

CN1<br />

Do not drive active high<br />

(use open drain)<br />

Right<br />

CN2<br />

OFF_BD_RESET# is an Output<br />

used to reset all peripherals<br />

FPGA<br />

JTAG<br />

DIO_[00:49]<br />

FPGA DIO<br />

FPGA_JTAG_TMS<br />

FPGA_JTAG_TCK<br />

FPGA_JTAG_TDO<br />

FPGA_JTAG_TDI<br />

OFF_BD_RESET#<br />

POWER<br />

POWER<br />

POWER<br />

DIO_14<br />

DIO_13<br />

DIO_12<br />

DIO_11<br />

DIO_10<br />

DIO_09<br />

DIO_08<br />

DIO_35<br />

DIO_06<br />

DIO_05<br />

DIO_04<br />

DIO_03<br />

DIO_02<br />

DIO_01<br />

DIO_00<br />

DIO_23<br />

1<br />

3<br />

5<br />

7<br />

9<br />

11<br />

13<br />

15<br />

17<br />

19<br />

21<br />

23<br />

25<br />

27<br />

29<br />

31<br />

33<br />

35<br />

37<br />

39<br />

41<br />

43<br />

45<br />

47<br />

49<br />

51<br />

53<br />

55<br />

57<br />

59<br />

61<br />

63<br />

65<br />

67<br />

69<br />

71<br />

73<br />

75<br />

77<br />

79<br />

81<br />

83<br />

85<br />

87<br />

89<br />

91<br />

93<br />

95<br />

97<br />

99<br />

2<br />

4<br />

6<br />

8<br />

10<br />

12<br />

14<br />

16<br />

18<br />

20<br />

22<br />

24<br />

26<br />

28<br />

30<br />

32<br />

34<br />

36<br />

38<br />

40<br />

42<br />

44<br />

46<br />

48<br />

50<br />

52<br />

54<br />

56<br />

58<br />

60<br />

62<br />

64<br />

66<br />

68<br />

70<br />

72<br />

74<br />

76<br />

78<br />

80<br />

82<br />

84<br />

86<br />

88<br />

90<br />

92<br />

94<br />

96<br />

98<br />

100<br />

EXT_RESET#<br />

DIO_07<br />

SDCARD_D2<br />

SDCARD_D3<br />

SDCARD_CMD<br />

SDCARD_3.3V<br />

SDCARD_CLK<br />

POWER<br />

SDCARD_D0<br />

SDCARD_D1<br />

V_BAT<br />

NAND_D7<br />

NAND_D6<br />

NAND_D5<br />

NAND_D4<br />

NAND_D3<br />

NAND_D2<br />

NAND_D1<br />

NAND_D0<br />

EN_USB_5V<br />

SD Card<br />

DIO_34<br />

DIO_33<br />

DIO_32<br />

DIO_31<br />

DIO_30<br />

DIO_29<br />

DIO_28<br />

DIO_27<br />

DIO_26<br />

DIO_25<br />

DIO_24<br />

SD card signals on connector<br />

are wired in parallel with<br />

SD card socket. Only one<br />

can be populated with SD card<br />

Maximum off-board load<br />

on 3.3V pin is 300 mA<br />

USB<br />

Ports<br />

Max. off-board load<br />

on 2.5V, 1.8V, 1.2V<br />

pins is 10 mA each<br />

Pin 79 = CPU JTAG Vcc<br />

SPI Bus<br />

Not 3.3V on some modules<br />

Max. load = 20 mA<br />

Ethernet<br />

Console<br />

CAN<br />

C123<br />

10 nF<br />

SPI_CS#<br />

CAN_TXD<br />

CAN_RXD<br />

ETH_RX+<br />

ETH_CT<br />

ETH_TX+<br />

ETH_RX-<br />

ETH_TX-<br />

ETH_CT<br />

DEV_USB_M<br />

DEV_USB_P<br />

HOSTA_USB_M<br />

HOSTA_USB_P<br />

HOSTB_USB_M<br />

HOSTB_USB_P<br />

DIO_48<br />

SPI_MOSI<br />

SPI_MISO<br />

SPI_CLK<br />

3.3V<br />

2.5V<br />

3.3V<br />

1.8V<br />

1.2V<br />

3.3V<br />

DEBUG_TXD<br />

DEBUG_RXD<br />

DIO_15<br />

DIO_16<br />

1<br />

3<br />

5<br />

7<br />

9<br />

11<br />

13<br />

15<br />

17<br />

19<br />

21<br />

23<br />

25<br />

27<br />

29<br />

31<br />

33<br />

35<br />

37<br />

39<br />

41<br />

43<br />

45<br />

47<br />

49<br />

51<br />

53<br />

55<br />

57<br />

59<br />

61<br />

63<br />

65<br />

67<br />

69<br />

71<br />

73<br />

75<br />

77<br />

79<br />

81<br />

83<br />

85<br />

87<br />

89<br />

91<br />

93<br />

95<br />

97<br />

99<br />

2<br />

4<br />

6<br />

8<br />

10<br />

12<br />

14<br />

16<br />

18<br />

20<br />

22<br />

24<br />

26<br />

28<br />

30<br />

32<br />

34<br />

36<br />

38<br />

40<br />

42<br />

44<br />

46<br />

48<br />

50<br />

52<br />

54<br />

56<br />

58<br />

60<br />

62<br />

64<br />

66<br />

68<br />

70<br />

72<br />

74<br />

76<br />

78<br />

80<br />

82<br />

84<br />

86<br />

88<br />

90<br />

92<br />

94<br />

96<br />

98<br />

100<br />

ETH_LEFT_LED<br />

ETH_RIGHT_LED<br />

RED_LED#<br />

GREEN_LED#<br />

TW_CLK<br />

TW_DAT<br />

CPU_JTAG_TMS<br />

CPU_JTAG_TCK<br />

CPU_JTAG_TDI<br />

CPU_JTAG_TDO<br />

DIO_50<br />

DIO_51<br />

DIO_52<br />

DIO_43<br />

DIO_49<br />

DIO_17<br />

DIO_18<br />

DIO_19<br />

DIO_20<br />

DIO_21<br />

DIO_36<br />

DIO_37<br />

DIO_38<br />

DIO_39<br />

DIO_22<br />

DIO_44<br />

DIO_45<br />

DIO_46<br />

DIO_47<br />

DIO_40<br />

DIO_41<br />

DIO_42<br />

I2C<br />

CPU<br />

JTAG<br />

DIO_20, DIO_21, DIO_50<br />

and DIO_51 have a 2K<br />

ohm resistor to GND<br />

(initializes to a logic "0")<br />

Serial Ports<br />

or DIO<br />

DIO_36 = UART0_TXD<br />

DIO_37 = UART0_RXD<br />

TYCO_100PIN<br />

DIO_[00:49]<br />

TYCO_100PIN<br />

DIO_38 = UART1_TXD<br />

DIO_39 = UART1_RXD<br />

CAN port and all UARTs<br />

DIO_22 = UART2_TXD<br />

Mode 1 Mode 2 Boots from<br />

1 1 NAND Flash<br />

1 0<br />

SD Card<br />

0 1<br />

Off-board Flash<br />

0 0<br />

Off-board Flash<br />

MODE1 and MODE2 states<br />

MODE1 and MODE2<br />

and Board ID bit states<br />

have PU resistors<br />

are latched prior to<br />

DIO_26 = MODE1<br />

DIO_25 = MODE2<br />

On some other modules, there is a<br />

16-bit bus for static memory<br />

type devices. But the <strong>TS</strong>-<strong>4500</strong><br />

does not support this functionality<br />

The <strong>TS</strong>-<strong>4500</strong> uses these<br />

"Bus signals" as DIO only.<br />

can all be changed<br />

to simple DIO lines<br />

DIO_44 = UART2_RXD<br />

DIO_45 = UART3_TXD<br />

DIO_46 = UART3_RXD<br />

DIO_47 = UART4_TXD<br />

DIO_40 = UART4_RXD<br />

DIO_41 = UART5_TXD<br />

DIO_42 = UART5_RXD<br />

OFF_BD_RESET# deasserted<br />

Use 1K ohm resistor<br />

SPI Flash is Boot source<br />

when MODE1 is low.<br />

to GND to set low<br />

<strong>Technologic</strong> <strong>Systems</strong><br />

Title: <strong>TS</strong>-<strong>4500</strong> 100-pin Off-Board Connectors<br />

Date Sept. 20, 2011<br />

Rev:<br />

C<br />

Designer<br />

RLM Sheet 5<br />

of<br />

5