- Page 1 and 2:

CCS C Compiler Manual PCB / PCM / P

- Page 3 and 4:

Table of Contents Overview ........

- Page 5 and 6:

Table of Contents PreProcessor ....

- Page 7 and 8:

Table of Contents enable_interrupts

- Page 9 and 10:

Table of Contents read_bank( ) ....

- Page 11 and 12:

Table of Contents spi_init() ......

- Page 13 and 14:

OVERVIEW C Compiler PCB, PCM and PC

- Page 15 and 16:

Overview Directories The compiler w

- Page 17 and 18:

Overview debug file. +FS Select SXC

- Page 19 and 20:

Overview Menu All of the IDE's func

- Page 21 and 22:

Overview Debugging Windows Debugger

- Page 23 and 24:

PROGRAM SYNTAX Overall Structure A

- Page 25 and 26:

Program Syntax Sequence Same as ??=

- Page 27 and 28:

STATEMENTS Statements STATEMENT if

- Page 29 and 30:

Statements The expression is evalua

- Page 31 and 32:

Statements goto goto The goto state

- Page 33:

Statements ; Statement: ; Example:

- Page 36 and 37:

Identifiers ABCDE ID[X] ID[X][X] ID

- Page 38 and 39:

expr&expr Left to Right expr^expr L

- Page 40 and 41:

Structures & Unions typedef Named R

- Page 42 and 43:

Enumerated Types enum enumeration t

- Page 44 and 45:

SEE ALSO: Declarations, Type Specif

- Page 46 and 47:

Using Program Memory for Data CCS C

- Page 49 and 50:

FUNCTION DEFINITION Function Defini

- Page 51 and 52:

Function Definition Default Paramet

- Page 53 and 54:

FUNCTIONAL OVERVIEW I2C I2C is a po

- Page 55 and 56:

Functional Overview #DEVICE ADC=10

- Page 57 and 58:

Functional Overview can_enable_rtr(

- Page 59 and 60:

Functional Overview Relevant Prepro

- Page 61 and 62:

Functional Overview Configuration M

- Page 63 and 64:

Functional Overview Writes N bytes

- Page 65 and 66:

Functional Overview External Memory

- Page 67 and 68:

Functional Overview Relevant Interr

- Page 69 and 70:

Functional Overview be treated as a

- Page 71 and 72:

Functional Overview psp_input_full(

- Page 73 and 74:

Functional Overview Program Eeprom

- Page 75 and 76:

Functional Overview None Relevant I

- Page 77 and 78:

Functional Overview printf() or fpr

- Page 79 and 80:

Functional Overview to be enabled.

- Page 81 and 82:

Functional Overview configure the s

- Page 83 and 84:

Functional Overview Relevant Interr

- Page 85 and 86:

Functional Overview None Relevant I

- Page 87 and 88:

Functional Overview USB Universal S

- Page 89 and 90:

Functional Overview Relevant Interr

- Page 91 and 92:

Functional Overview WDT or Watch Do

- Page 93 and 94:

Functional Overview variables/const

- Page 95 and 96:

PREPROCESSOR PRE-PROCESSOR DIRECTOR

- Page 97 and 98:

PreProcessor { int8 a; int16 b; } t

- Page 99 and 100:

PreProcessor ASR.B f,W W0 = f >> 1a

- Page 101 and 102:

PreProcessor DEC Wa,Wd Wd = Wa â

- Page 103 and 104:

PreProcessor MUL.SU Wa,lit5,Wd {Wd+

- Page 105 and 106:

PreProcessor SUBR Wa,lit5,Wd Wd = l

- Page 107 and 108:

PreProcessor The compiler will set

- Page 109 and 110:

PreProcessor Examples: #byte status

- Page 111 and 112:

PreProcessor #define isequal(a,b) (

- Page 113 and 114:

PreProcessor NORETFIE to interrupt

- Page 115 and 116:

PreProcessor Note: you may NOT use

- Page 117 and 118:

PreProcessor void TimerTask(void) {

- Page 119 and 120:

PreProcessor Some processors allow

- Page 121 and 122:

PreProcessor to see if the specifie

- Page 123 and 124:

PreProcessor #INCLUDE "filename" El

- Page 125 and 126:

PreProcessor #INT_IC2QEI Input Capt

- Page 127 and 128:

PreProcessor Files: Also See: enabl

- Page 129 and 130:

PreProcessor #line Syntax: Elements

- Page 131 and 132:

PreProcessor Purpose: Stops inserti

- Page 133 and 134:

PreProcessor object file. It is an

- Page 135 and 136:

PreProcessor SCK2 SSDMA Transmit (a

- Page 137 and 138:

PreProcessor #priority Syntax: Elem

- Page 139 and 140:

PreProcessor #rom Syntax: Elements:

- Page 141 and 142:

PreProcessor the serial number. lis

- Page 143 and 144:

PreProcessor __time__ Syntax: Eleme

- Page 145 and 146:

PreProcessor #use capture Syntax: E

- Page 147 and 148:

PreProcessor type=speed option the

- Page 149 and 150:

PreProcessor SLOW RESTART_WDT FORCE

- Page 151 and 152:

PreProcessor remappable pin to firs

- Page 153 and 154:

PreProcessor MULTI_MASTER the RCV p

- Page 155 and 156:

PreProcessor not used. Purpose: Thi

- Page 157 and 158:

PreProcessor CLOCK_HIGH=n High time

- Page 159 and 160:

PreProcessor TICK=xx Sets the desir

- Page 161 and 162:

PreProcessor Examples: #USE TOUCHPA

- Page 163 and 164:

BUILT-IN FUNCTIONS BUILT-IN FUNCTIO

- Page 165 and 166:

Built-in Functions isspace(char) st

- Page 167 and 168:

Built-in Functions rtc_alarm_write(

- Page 169 and 170:

Built-in Functions Domain error occ

- Page 171 and 172:

Built-in Functions Returns: Functio

- Page 173 and 174:

Built-in Functions atoi( ) atol( )

- Page 175 and 176:

Built-in Functions bit_test( ) Synt

- Page 177 and 178:

Built-in Functions calloc( ) Syntax

- Page 179 and 180:

Built-in Functions clc1_setup_input

- Page 181 and 182:

Built-in Functions . cog_restart( )

- Page 183 and 184:

Built-in Functions delay_cycles( )

- Page 185 and 186:

Built-in Functions output_low(PIN_B

- Page 187 and 188:

Built-in Functions should have been

- Page 189 and 190:

Built-in Functions If "errno.h" is

- Page 191 and 192:

Built-in Functions Examples: printf

- Page 193 and 194:

Built-in Functions Availability: Re

- Page 195 and 196:

Built-in Functions putc( ) putchar(

- Page 197 and 198:

Built-in Functions frexp( ) Syntax:

- Page 199 and 200:

Built-in Functions Li f,g or e Matc

- Page 201 and 202:

Built-in Functions Requires: Exampl

- Page 203 and 204:

Built-in Functions Example Files: A

- Page 205 and 206:

Built-in Functions get_tris_x( ) Sy

- Page 207 and 208:

Built-in Functions INT:iiiii ID DEV

- Page 209 and 210:

Built-in Functions SPIxDO SPIxCLK E

- Page 211 and 212:

Built-in Functions ready to be read

- Page 213 and 214:

Built-in Functions i2c_poll( ) Synt

- Page 215 and 216:

Built-in Functions i2c_speed( ) Syn

- Page 217 and 218:

Built-in Functions i2c_write( ) Syn

- Page 219 and 220:

Built-in Functions Availability: Re

- Page 221 and 222:

Built-in Functions clear_interrupt,

- Page 223 and 224:

Built-in Functions Returns: Functio

- Page 225 and 226:

Built-in Functions Parameters: Retu

- Page 227 and 228:

Built-in Functions Examples: byte C

- Page 229 and 230: Built-in Functions Requires: #INCLU

- Page 231 and 232: Built-in Functions make32( ) Syntax

- Page 233 and 234: Built-in Functions n is a count of

- Page 235 and 236: Built-in Functions Also See: memcpy

- Page 237 and 238: Built-in Functions } void main() {

- Page 239 and 240: Built-in Functions take much longer

- Page 241 and 242: Built-in Functions Parameters: Retu

- Page 243 and 244: Built-in Functions Function: Availa

- Page 245 and 246: Built-in Functions Parameters: Stri

- Page 247 and 248: Built-in Functions Availability: Re

- Page 249 and 250: Built-in Functions putc_send( ); fp

- Page 251 and 252: Built-in Functions pwm_set_duty() S

- Page 253 and 254: Built-in Functions qei_status( ) Sy

- Page 255 and 256: Built-in Functions Function: Availa

- Page 257 and 258: Built-in Functions Parameters: Retu

- Page 259 and 260: Built-in Functions at 0 and the ran

- Page 261 and 262: Built-in Functions · ADC_START_ONL

- Page 263 and 264: Built-in Functions Function: Availa

- Page 265 and 266: Built-in Functions Examples: Exampl

- Page 267 and 268: Built-in Functions Availability: Re

- Page 269 and 270: Built-in Functions Examples: Exampl

- Page 271 and 272: Built-in Functions rtos_disable( )

- Page 273 and 274: Built-in Functions rtos_run( ) The

- Page 275 and 276: Built-in Functions program will con

- Page 277 and 278: Built-in Functions Example Files: A

- Page 279: Built-in Functions n Assigns the nu

- Page 283 and 284: Built-in Functions set_open_drain_c

- Page 285 and 286: Built-in Functions Returns: Functio

- Page 287 and 288: Built-in Functions setup_sd_adc_cal

- Page 289 and 290: Built-in Functions Function: Availa

- Page 291 and 292: Built-in Functions Parameters: Retu

- Page 293 and 294: Built-in Functions ADC_CLOCK_DIV_3

- Page 295 and 296: Built-in Functions CCP_SHUTDOWN_ON_

- Page 297 and 298: Built-in Functions Returns: Functio

- Page 299 and 300: Built-in Functions Examples: Exampl

- Page 301 and 302: Built-in Functions Function: Availa

- Page 303 and 304: Built-in Functions LCD_DISABLED, L

- Page 305 and 306: Built-in Functions setup_opamp1( )

- Page 307 and 308: Built-in Functions increment/decrem

- Page 309 and 310: Built-in Functions Examples: Exampl

- Page 311 and 312: Built-in Functions Parameters: Opti

- Page 313 and 314: Built-in Functions SDADC_GAIN_1

- Page 315 and 316: Built-in Functions TB_DIV_32, TB_DI

- Page 317 and 318: Built-in Functions Returns: Functio

- Page 319 and 320: Built-in Functions T5_DIV_BY_1, T5_

- Page 321 and 322: Built-in Functions Also See: #FUSES

- Page 323 and 324: Built-in Functions // This shifts 8

- Page 325 and 326: Built-in Functions spi_data_is_in(

- Page 327 and 328: Built-in Functions will be clocked

- Page 329 and 330: Built-in Functions spi_write( ) spi

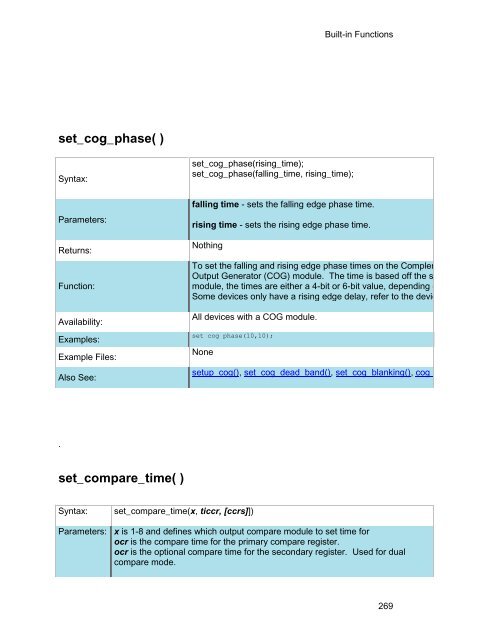

- Page 331 and 332:

Built-in Functions Parameters: Retu

- Page 333 and 334:

Built-in Functions Returns: Functio

- Page 335 and 336:

Built-in Functions Availability: Re

- Page 337 and 338:

Built-in Functions Requires: Nothin

- Page 339 and 340:

Built-in Functions Note: If the sta

- Page 341 and 342:

Built-in Functions void main(void)

- Page 343 and 344:

Built-in Functions Examples: int fo

- Page 345 and 346:

Built-in Functions Availability: Re

- Page 347 and 348:

STANDARD C INCLUDE FILES errno.h er

- Page 349 and 350:

Standard C Include Files CHAR_MIN:

- Page 351 and 352:

ERROR MESSAGES Compiler Error Messa

- Page 353 and 354:

Error Messages Expect comma Expect

- Page 355 and 356:

Error Messages In the meantime if t

- Page 357 and 358:

Error Messages A function and all o

- Page 359:

Error Messages USE parameter value

- Page 362 and 363:

Function never called Function not

- Page 365 and 366:

COMMON QUESTIONS & ANSWERS How are

- Page 367 and 368:

Common Questions & Answers How can

- Page 369 and 370:

Common Questions & Answers This exa

- Page 371 and 372:

Common Questions & Answers } set_tr

- Page 373 and 374:

Common Questions & Answers How does

- Page 375 and 376:

Common Questions & Answers RAM is a

- Page 377 and 378:

Common Questions & Answers What is

- Page 379 and 380:

Common Questions & Answers Why does

- Page 381:

Common Questions & Answers If nothi

- Page 384 and 385:

A stand-alone application that need

- Page 386 and 387:

Serial boot loader program for chip

- Page 388 and 389:

Simulates an I2C serial EEPROM show

- Page 390 and 391:

Serial EEPROM functions 24256.C Ser

- Page 392 and 393:

Standard C error handling for math

- Page 394 and 395:

#include #endif #use delay(clock=2

- Page 396 and 397:

} } shift_left(cmd, 2,0); output_hi

- Page 398 and 399:

} printf("RTOS has been terminated\

- Page 400 and 401:

#use rs232(baud=9600,xmit=PIN_C6,rc

- Page 402 and 403:

#use delay(clock=20000000) #use rs2

- Page 405 and 406:

SOFTWARE LICENSE AGREEMENT SOFTWARE

- Page 407 and 408:

INDEX # #ASM ......................

- Page 409 and 410:

Index Continue ....................

- Page 411 and 412:

Index LIST ........................

- Page 413 and 414:

Index setup_power_pwm .............