Virtex-5 FPGA XtremeDSP Design Considerations User Guide - Xilinx

Virtex-5 FPGA XtremeDSP Design Considerations User Guide - Xilinx

Virtex-5 FPGA XtremeDSP Design Considerations User Guide - Xilinx

Create successful ePaper yourself

Turn your PDF publications into a flip-book with our unique Google optimized e-Paper software.

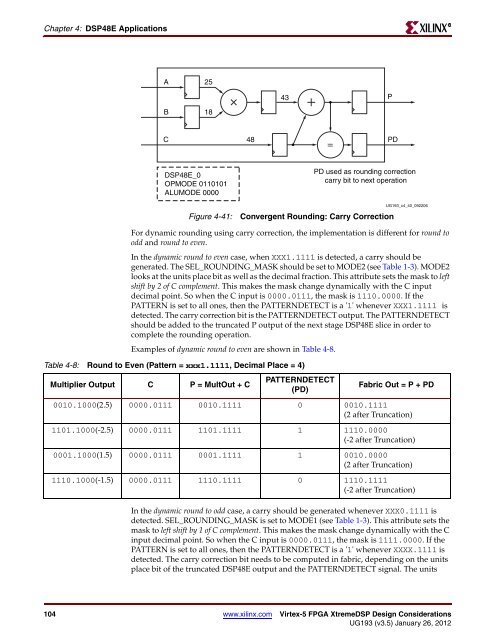

Chapter 4: DSP48E Applications<br />

A<br />

B<br />

C<br />

25<br />

DSP48E_0<br />

OPMODE 0110101<br />

ALUMODE 0000<br />

Figure 4-41: Convergent Rounding: Carry Correction<br />

UG193_c4_40_092206<br />

For dynamic rounding using carry correction, the implementation is different for round to<br />

odd and round to even.<br />

In the dynamic round to even case, when XXX1.1111 is detected, a carry should be<br />

generated. The SEL_ROUNDING_MASK should be set to MODE2 (see Table 1-3). MODE2<br />

looks at the units place bit as well as the decimal fraction. This attribute sets the mask to left<br />

shift by 2 of C complement. This makes the mask change dynamically with the C input<br />

decimal point. So when the C input is 0000.0111, the mask is 1110.0000. If the<br />

PATTERN is set to all ones, then the PATTERNDETECT is a '1' whenever XXX1.1111 is<br />

detected. The carry correction bit is the PATTERNDETECT output. The PATTERNDETECT<br />

should be added to the truncated P output of the next stage DSP48E slice in order to<br />

complete the rounding operation.<br />

Examples of dynamic round to even are shown in Table 4-8.<br />

Table 4-8: Round to Even (Pattern = xxx1.1111, Decimal Place = 4)<br />

18<br />

48<br />

In the dynamic round to odd case, a carry should be generated whenever XXX0.1111 is<br />

detected. SEL_ROUNDING_MASK is set to MODE1 (see Table 1-3). This attribute sets the<br />

mask to left shift by 1 of C complement. This makes the mask change dynamically with the C<br />

input decimal point. So when the C input is 0000.0111, the mask is 1111.0000. If the<br />

PATTERN is set to all ones, then the PATTERNDETECT is a '1' whenever XXXX.1111 is<br />

detected. The carry correction bit needs to be computed in fabric, depending on the units<br />

place bit of the truncated DSP48E output and the PATTERNDETECT signal. The units<br />

104 www.xilinx.com <strong>Virtex</strong>-5 <strong>FPGA</strong> <strong>XtremeDSP</strong> <strong>Design</strong> <strong>Considerations</strong><br />

UG193 (v3.5) January 26, 2012<br />

43<br />

=<br />

PD used as rounding correction<br />

carry bit to next operation<br />

Multiplier Output C P = MultOut + C<br />

PATTERNDETECT<br />

(PD)<br />

Fabric Out = P + PD<br />

0010.1000(2.5) 0000.0111 0010.1111 0 0010.1111<br />

(2 after Truncation)<br />

1101.1000(-2.5) 0000.0111 1101.1111 1 1110.0000<br />

(-2 after Truncation)<br />

0001.1000(1.5) 0000.0111 0001.1111 1 0010.0000<br />

(2 after Truncation)<br />

1110.1000(-1.5) 0000.0111 1110.1111 0 1110.1111<br />

(-2 after Truncation)<br />

P<br />

PD<br />

R