Virtex-5 FPGA XtremeDSP Design Considerations User Guide - Xilinx

Virtex-5 FPGA XtremeDSP Design Considerations User Guide - Xilinx

Virtex-5 FPGA XtremeDSP Design Considerations User Guide - Xilinx

Create successful ePaper yourself

Turn your PDF publications into a flip-book with our unique Google optimized e-Paper software.

Chapter 1: DSP48E Description and Specifics<br />

C<br />

CEC<br />

RSTC<br />

D<br />

EN<br />

RST<br />

Figure 1-8: C Port Logic<br />

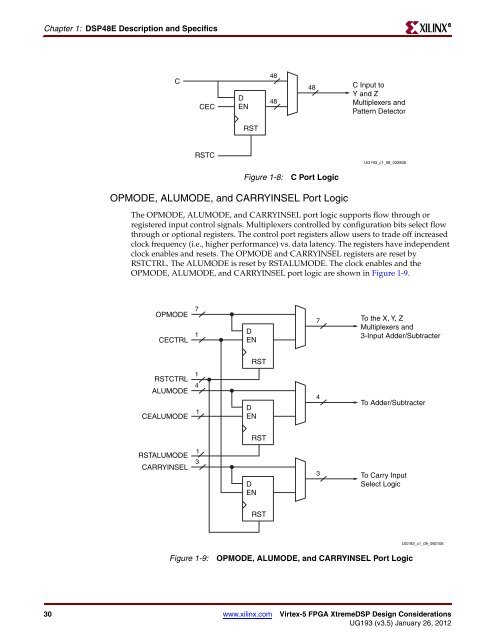

OPMODE, ALUMODE, and CARRYINSEL Port Logic<br />

C Input to<br />

Y and Z<br />

Multiplexers and<br />

Pattern Detector<br />

The OPMODE, ALUMODE, and CARRYINSEL port logic supports flow through or<br />

registered input control signals. Multiplexers controlled by configuration bits select flow<br />

through or optional registers. The control port registers allow users to trade off increased<br />

clock frequency (i.e., higher performance) vs. data latency. The registers have independent<br />

clock enables and resets. The OPMODE and CARRYINSEL registers are reset by<br />

RSTCTRL. The ALUMODE is reset by RSTALUMODE. The clock enables and the<br />

OPMODE, ALUMODE, and CARRYINSEL port logic are shown in Figure 1-9.<br />

OPMODE<br />

CECTRL<br />

RSTCTRL<br />

ALUMODE<br />

CEALUMODE<br />

RSTALUMODE<br />

CARRYINSEL<br />

7<br />

1<br />

1<br />

4<br />

1<br />

1<br />

3<br />

D<br />

EN<br />

D<br />

EN<br />

D<br />

EN<br />

30 www.xilinx.com <strong>Virtex</strong>-5 <strong>FPGA</strong> <strong>XtremeDSP</strong> <strong>Design</strong> <strong>Considerations</strong><br />

UG193 (v3.5) January 26, 2012<br />

RST<br />

RST<br />

RST<br />

48<br />

48<br />

48<br />

UG193_c1_08_032806<br />

To the X, Y, Z<br />

Multiplexers and<br />

3-Input Adder/Subtracter<br />

Figure 1-9: OPMODE, ALUMODE, and CARRYINSEL Port Logic<br />

7<br />

4<br />

3<br />

To Adder/Subtracter<br />

To Carry Input<br />

Select Logic<br />

UG193_c1_09_092106<br />

R