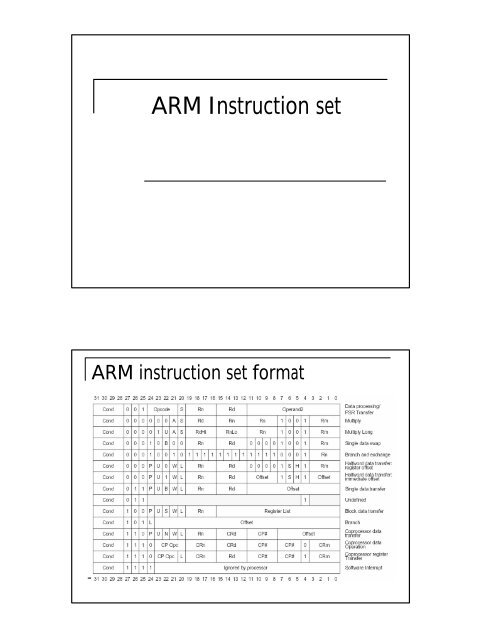

ARM Instruction set

ARM Instruction set

ARM Instruction set

You also want an ePaper? Increase the reach of your titles

YUMPU automatically turns print PDFs into web optimized ePapers that Google loves.

<strong>ARM</strong> <strong>Instruction</strong> <strong>set</strong><strong>ARM</strong> instruction <strong>set</strong> format

<strong>ARM</strong> instruction <strong>set</strong> (1)<strong>ARM</strong> instruction <strong>set</strong> (2)

Condition Code Branch <strong>Instruction</strong>s• Branch and Branch with Link (B,BL)B{L}{}

Branch <strong>Instruction</strong>s• Example (Data Processing<strong>Instruction</strong>s)

(Data Processing<strong>Instruction</strong>s)(Data Processing<strong>Instruction</strong>s)• {cond}{S} Rd, qMOVMVN• {cond} Rn, qCMP,CMN,TEQ,TST ()• {cond}{S} Rd, Rn, qAND,EOR,SUB,RSB,ADD,ADC,SBC,RSC,ORR,BIC

(Data Processing<strong>Instruction</strong>s)• Immediate Operand=1• Exampleq MOV R0, #100 //R0=100q CMP R1, #200 // R1 200q ADD R0, R1, #0x0ff //R0 = R1 + 0x0ff(Data Processing<strong>Instruction</strong>s)• Immediate Operand=0q Shift

(Data Processing<strong>Instruction</strong>s)q (Logical Shift Left, LSL)(Data Processing<strong>Instruction</strong>s)q (Logical Shift Right, LSR)

(Data Processing<strong>Instruction</strong>s)q (Arithmetic Shift Right, ASR)(Data Processing<strong>Instruction</strong>s)q (Rotate Right, ROR)

(Data Processing<strong>Instruction</strong>s)• Exampleq MOV R0, R1, LSR #3 //R0 = R1>>3q SUB R0, R1, R2, LSL #5 //R0 = R1 – (R27)q MOV R3, R4, LSL R5 //R5(Rs)//R4PSR Transfer (MRS, MSR)• MRS: Move register from SPSR orSPSR_

(PSR)• MRS- PSR registerq MRS{cond} Rd, q Example:• MRS R1, CPSR //R1= CPSR• MRS R2, SPSR //R2 = SPSR• MSR- register PSRq MSR{cond} , Rmq Example:• MSR SPSR, R0 // SPSR= R0(PSR)• MSR- register PSRqqMSR{cond} , RmExample:• MSR CPSR_c, R3//CPSR[7:0] = R3[7:0]• MSR-PSRqqMSR{cond} , Example:• MSR CPSR_f, #0xe0000000 //CPSR[31:28]=0b1110

(Block Data Transferinstructions)(Block Data Transferinstructions)• {cond}Rn{!}, {^}qqqRn{}{R0R1-R7R8}{!} !(W=1)(W=0)

(Block Data Transferinstructions)• Addressing mode names• Increment after

• Increment after• Increment before

• Increment after• decrement after

• decrement after• decrement before

• decrement before(Coprocessor <strong>Instruction</strong>s)• Coprocessor Register Transfer <strong>Instruction</strong>sq MCR (Move to Coprocessor from <strong>ARM</strong> Register)q MRC (Move to <strong>ARM</strong> Register from Coprocessor)

(Coprocessor RegisterTransfer <strong>Instruction</strong>s)(Coprocessor RegisterTransfer <strong>Instruction</strong>s)• {cond}p#,,Rd,cn,cm{,}qqqqqqqqMRCCoprocessor <strong>ARM</strong>MCR<strong>ARM</strong>Coprocessor{cond}p# CoprocessorCP OpcRd <strong>ARM</strong>cn and cm CoprocessorCP

(Coprocessor RegisterTransfer <strong>Instruction</strong>s)• Exampleq MRC p15, 2, R2, c1, c2, 3// 15 (CP15)//opcode 1=2, opcode 2= 3//CP15 source register 1 and 2//transfer data to <strong>ARM</strong> register, R2