Create successful ePaper yourself

Turn your PDF publications into a flip-book with our unique Google optimized e-Paper software.

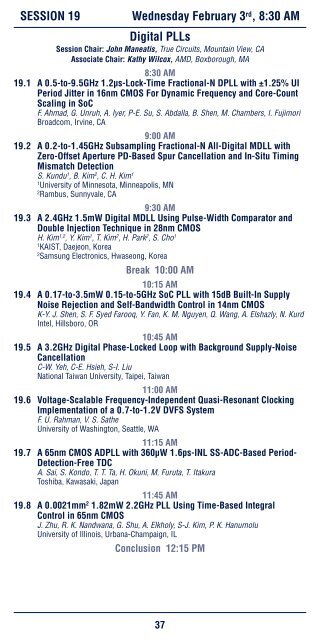

SESSION 19<br />

Wednesday February 3 rd , 8:30 AM<br />

Digital PLLs<br />

Session Chair: John Maneatis, True Circuits, Mountain View, CA<br />

Associate Chair: Kathy Wilcox, AMD, Boxborough, MA<br />

8:30 AM<br />

19.1 A 0.5-to-9.5GHz 1.2µs-Lock-Time Fractional-N DPLL with ±1.25% UI<br />

Period Jitter in 16nm CMOS For Dynamic Frequency and Core-Count<br />

Scaling in SoC<br />

F. Ahmad, G. Unruh, A. Iyer, P-E. Su, S. Abdalla, B. Shen, M. Chambers, I. Fujimori<br />

Broadcom, Irvine, CA<br />

9:00 AM<br />

19.2 A 0.2-to-1.45GHz Subsampling Fractional-N All-Digital MDLL with<br />

Zero-Offset Aperture PD-Based Spur Cancellation and In-Situ Timing<br />

Mismatch Detection<br />

S. Kundu 1 , B. Kim 2 , C. H. Kim 1<br />

1<br />

University of Minnesota, Minneapolis, MN<br />

2<br />

Rambus, Sunnyvale, CA<br />

9:30 AM<br />

19.3 A 2.4GHz 1.5mW Digital MDLL Using Pulse-Width Comparator and<br />

Double Injection Technique in 28nm CMOS<br />

H. Kim 1,2 , Y. Kim 1 , T. Kim 2 , H. Park 2 , S. Cho 1<br />

1<br />

KAIST, Daejeon, Korea<br />

2<br />

Samsung Electronics, Hwaseong, Korea<br />

Break 10:00 AM<br />

10:15 AM<br />

19.4 A 0.17-to-3.5mW 0.15-to-5GHz SoC PLL with 15dB Built-In Supply<br />

Noise Rejection and Self-Bandwidth Control in 14nm CMOS<br />

K-Y. J. Shen, S. F. Syed Farooq, Y. Fan, K. M. Nguyen, Q. Wang, A. Elshazly, N. Kurd<br />

Intel, Hillsboro, OR<br />

10:45 AM<br />

19.5 A 3.2GHz Digital Phase-Locked Loop with Background Supply-Noise<br />

Cancellation<br />

C-W. Yeh, C-E. Hsieh, S-I. Liu<br />

National Taiwan University, Taipei, Taiwan<br />

11:00 AM<br />

19.6 Voltage-Scalable Frequency-Independent Quasi-Resonant Clocking<br />

Implementation of a 0.7-to-1.2V DVFS System<br />

F. U. Rahman, V. S. Sathe<br />

University of Washington, Seattle, WA<br />

11:15 AM<br />

19.7 A 65nm CMOS ADPLL with 360μW 1.6ps-INL SS-ADC-Based Period-<br />

Detection-Free TDC<br />

A. Sai, S. Kondo, T. T. Ta, H. Okuni, M. Furuta, T. Itakura<br />

Toshiba, Kawasaki, Japan<br />

11:45 AM<br />

19.8 A 0.0021mm 2 1.82mW 2.2GHz PLL Using Time-Based Integral<br />

Control in 65nm CMOS<br />

J. Zhu, R. K. Nandwana, G. Shu, A. Elkholy, S-J. Kim, P. K. Hanumolu<br />

University of Illinois, Urbana-Champaign, IL<br />

Conclusion 12:15 PM<br />

37