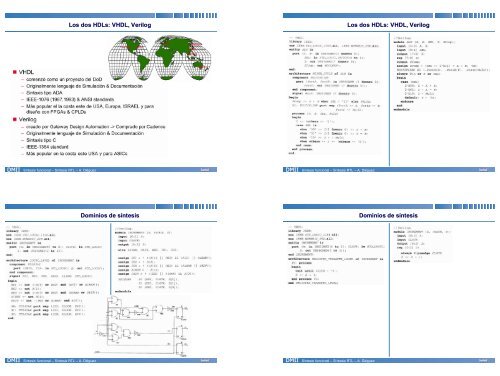

Los dos HDLs: VHDL, Verilog Los dos HDLs: VHDL, Verilog ...

Los dos HDLs: VHDL, Verilog Los dos HDLs: VHDL, Verilog ...

Los dos HDLs: VHDL, Verilog Los dos HDLs: VHDL, Verilog ...

You also want an ePaper? Increase the reach of your titles

YUMPU automatically turns print PDFs into web optimized ePapers that Google loves.

DMII Síntesis funcional – Síntesis RTL – A. Diéguez<br />

DMII Síntesis funcional – Síntesis RTL – A. Diéguez<br />

<strong>Los</strong> <strong>dos</strong> <strong>HDLs</strong>: <strong>HDLs</strong>:<br />

<strong>VHDL</strong>, <strong>Verilog</strong><br />

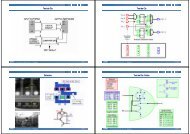

Dominios de síntesis ntesis<br />

DMII Síntesis funcional – Síntesis RTL – A. Diéguez<br />

DMII Síntesis funcional – Síntesis RTL – A. Diéguez<br />

<strong>Los</strong> <strong>dos</strong> <strong>HDLs</strong>: <strong>HDLs</strong>:<br />

<strong>VHDL</strong>, <strong>Verilog</strong><br />

Dominios de síntesis ntesis

DMII Síntesis funcional – Síntesis RTL – A. Diéguez<br />

DMII Síntesis funcional – Síntesis RTL – A. Diéguez<br />

Dominios de síntesis ntesis<br />

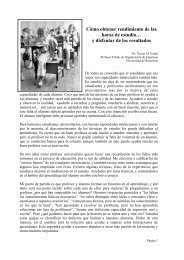

¿Por Por qué qu diseñar dise ar en alto nivel? nivel<br />

DMII Síntesis funcional – Síntesis RTL – A. Diéguez<br />

DMII Síntesis funcional – Síntesis RTL – A. Diéguez<br />

Dominios de síntesis ntesis<br />

¿Por Por qué qu diseñar dise ar en alto nivel?<br />

nivel

DMII Síntesis funcional – Síntesis RTL – A. Diéguez<br />

DMII Síntesis funcional – Síntesis RTL – A. Diéguez<br />

Síntesis ntesis funcional<br />

Síntesis ntesis funcional: funcional:<br />

Scheduling<br />

DMII Síntesis funcional – Síntesis RTL – A. Diéguez<br />

DMII Síntesis funcional – Síntesis RTL – A. Diéguez<br />

Síntesis ntesis funcional: funcional:<br />

Scheduling<br />

Síntesis ntesis funcional: funcional:<br />

ALU Allocation

DMII Síntesis funcional – Síntesis RTL – A. Diéguez<br />

DMII Síntesis funcional – Síntesis RTL – A. Diéguez<br />

Síntesis ntesis funcional: funcional:<br />

ALU Allocation<br />

Síntesis ntesis funcional: funcional:<br />

Register Allocation<br />

DMII Síntesis funcional – Síntesis RTL – A. Diéguez<br />

DMII Síntesis funcional – Síntesis RTL – A. Diéguez<br />

Síntesis ntesis funcional: funcional:<br />

Register Allocation<br />

Síntesis ntesis funcional: funcional:<br />

Scheduling

Síntesis ntesis de Alto nivel/behavioral/arquitectura/funcional<br />

Especificationes<br />

DMII Síntesis funcional – Síntesis RTL – A. Diéguez<br />

DMII Síntesis funcional – Síntesis RTL – A. Diéguez<br />

Flujo de síntesis ntesis de alto nivel<br />

Schedulling: asignación de cada operación a un intervalo de tiempo correspondiente a un ciclo de reloj o intervalo<br />

Resource Allocation: Selección del tipo de harware y el número de componentes<br />

Module binding: Asignación de operaciones a los componentes harware<br />

Síntesis del control: Diseño del estilo de control y estrategia de reloj<br />

Entrada<br />

Especificación funcional<br />

Criterios de diseño (timing, prestaciones, coste, consumo, #pines, etc)<br />

Una función de optimización<br />

Una librería de módulos representando las funciones disponibles<br />

Objetivos<br />

Generar un diseño RTL que<br />

Implemente la función especificada<br />

Satisfaga los criterios de diseño<br />

Conduzca a una optimización de la función coste<br />

Coste= a · Area + b · Tiempo_ejecución + …<br />

Salida<br />

Estructura RTL<br />

Controlador (capturado normalmente simbólicamente como FSM)<br />

Otros atributos, tales como información geométrica, que guíen a las<br />

siguientes tareas<br />

DMII Síntesis funcional – Síntesis RTL – A. Diéguez<br />

DMII Síntesis funcional – Síntesis RTL – A. Diéguez<br />

Síntesis ntesis de Alto Nivel<br />

Scheduling

DMII Síntesis funcional – Síntesis RTL – A. Diéguez<br />

DMII Síntesis funcional – Síntesis RTL – A. Diéguez<br />

Scheduling: Scheduling:<br />

Ejemplo<br />

Scheduling: Scheduling:<br />

Ejemplo<br />

DMII Síntesis funcional – Síntesis RTL – A. Diéguez<br />

DMII Síntesis funcional – Síntesis RTL – A. Diéguez<br />

Scheduling: Scheduling:<br />

Ejemplo<br />

Allocation y binding<br />

Allocation : determinación del tipo y número de recursos<br />

Elementos funcionales<br />

Elementos de almacenamiento<br />

Conexiones, busses<br />

Binding : Asignación de recursos a componentes<br />

Operaciones a componentes funcionales<br />

Valores a almacenar a componentes de almacenamiento<br />

Transferencias de datos a buses/líneas<br />

Puntos clave:<br />

Compartición de recursos<br />

Objetivos en la optimización<br />

Minimizar coste total de recursos, interconexiones<br />

Cumplir los criterios de retraso (restricciones en caminos críticos)<br />

Técnicas<br />

Constructivas: comenzar con un datapath vacio y añadir componentes funcionales, de almacenamiento<br />

e interconexiones a medida que se necesitan de acuerdo al scheduling.<br />

Algoritmos tipo Greedy: realizar allocation para un paso de tiempo a la vez<br />

Basa<strong>dos</strong> en reglas: usa<strong>dos</strong> para seleccionar el tipo y número de unidades funcionales,<br />

especialmente antes del scheduling<br />

Basadas en teoría de grafos: las sub-tareas se asocian a problemas bien defini<strong>dos</strong> en la teoría de grafos<br />

Clique partitioning<br />

Algoritmo Left-edge

DMII Síntesis funcional – Síntesis RTL – A. Diéguez<br />

DMII Síntesis funcional – Síntesis RTL – A. Diéguez<br />

Clique-partitioning<br />

Clique partitioning<br />

Síntesis ntesis de lógica gica/RTL /RTL<br />

Especificationes<br />

DMII Síntesis funcional – Síntesis RTL – A. Diéguez<br />

Independiente Tecnología<br />

DMII Síntesis funcional – Síntesis RTL – A. Diéguez<br />

DMII<br />

Librería<br />

Dependiente Tecnología<br />

Left-edge Left edge algorithm<br />

Flujo de síntesis ntesis lógica gica<br />

Descripción RTL (<strong>Verilog</strong>, <strong>VHDL</strong>)<br />

Optimización Lógica<br />

Red Booleana<br />

Technology Mapping<br />

Gate-level Netlist<br />

Minimizar # de literales<br />

Factorización<br />

Extracción el. Comunes<br />

Opt. temporal (reestructurar red)<br />

Estimar coste<br />

Velocidad<br />

Area<br />

Consumo<br />

La Síntesis Lógica se divide en <strong>dos</strong> partes:<br />

Optimización independiente de la tecnología<br />

· Determinación de la estructura lógica<br />

· Estimación de coste (indep. de la tecnología)<br />

Optimización dependiente de la tecnología (technology mapping)<br />

· Asociación a puertas de la librería<br />

· Modelo detallado de coste específico para la tecnología

Suma de productos:<br />

x = A D F + A E F + B D F + B E F + C D F + C E F + G<br />

6 AND3 + 1 OR7 (podría no existir!)<br />

25 cables (19 literales + 6 líneas internas)<br />

A<br />

D 1<br />

F<br />

A<br />

E 2<br />

F<br />

B<br />

D 3<br />

F<br />

B<br />

E<br />

F<br />

C<br />

D<br />

F<br />

C<br />

E<br />

F<br />

G<br />

4<br />

5<br />

6<br />

Two-Level Two Level vs. Multi-Level Multi Level Logic Synthesis<br />

Minimizar # términos producto.<br />

Quine-McCluskey.<br />

Espresso (SOP)<br />

DMII Síntesis funcional – Síntesis RTL – A. Diéguez<br />

t 1 = d + e;<br />

t 2 = b + h;<br />

t 3 = at 2 + c;<br />

t 4 = t 1t 3 + fgh;<br />

F = t 4’;<br />

f<br />

g<br />

d<br />

e<br />

h<br />

b<br />

a<br />

c<br />

DMII Síntesis funcional – Síntesis RTL – A. Diéguez<br />

7<br />

x<br />

A<br />

B<br />

C<br />

D<br />

E<br />

F<br />

G<br />

Necesaria para SCs, Gas, FPGAs<br />

1<br />

2 3<br />

Forma factorizada (SOP(SOP(…))):<br />

x = (A + B + C) (D + E) F + G<br />

1 OR3 + 2 OR2 + 1 AND3<br />

10 cables (7 literales + 3 líneas internas)<br />

Minimizar # literales, puertas, retraso.<br />

Factorización algebraica.<br />

SIS (forma factorizada)<br />

Technology mapping: Cual es el problema?<br />

problema<br />

F<br />

inv(1) nand2(2)<br />

nand3 (3)<br />

nor(2)<br />

aoi21 (3)<br />

xor (5)<br />

4<br />

x<br />

nor3 (3)<br />

oai22 (4)<br />

t 1 t 3 + fgh<br />

F<br />

t t4’ 4’<br />

at 2 +c<br />

d+e b+h<br />

DMII Síntesis funcional – Síntesis RTL – A. Diéguez<br />

f<br />

g<br />

t1 = d + e;<br />

d<br />

t2 = b + h;<br />

t3 = at2 + c; e<br />

t4 = t1t3 + fgh;<br />

F = t4’; h<br />

b<br />

a<br />

Coste total = 23<br />

c<br />

f<br />

g<br />

t1 = d + e;<br />

d<br />

t2 = b + h;<br />

t3 = at2 + c; e<br />

t4 = t1t3 + fgh;<br />

F = t4’; h<br />

b<br />

a<br />

Area total = 19 c<br />

and2(3)<br />

or2(3)<br />

or2(3)<br />

nand2(2)<br />

inv(1)<br />

DMII Síntesis funcional – Síntesis RTL – A. Diéguez<br />

Technology mapping<br />

d’ e’<br />

a<br />

F<br />

c<br />

f<br />

b’ h’<br />

g<br />

h<br />

Technology mapping (área ( rea)<br />

nand2(2)<br />

aoi22(4)<br />

F<br />

F<br />

t 1 = d + e;<br />

t 2 = b + h;<br />

t 3 = at2 + c;<br />

t 4 = t1t3 + fgh;<br />

F = t 4 ’;<br />

Area total = 15<br />

inv(1) nand2(2)<br />

nand3 (3)<br />

f<br />

g<br />

d<br />

e<br />

h<br />

b<br />

a<br />

c<br />

nor(2)<br />

aoi21 (3)<br />

xor (5)<br />

oai21 (3)<br />

oai21(3)<br />

inv(1)<br />

nand3(3)<br />

nand2(2)<br />

nor3 (3)<br />

oai22 (4)<br />

and2(3)<br />

F

Area<br />

INV (1)<br />

NAND2 (2)<br />

NAND3 (3)<br />

AOI21 (3)<br />

NAND4 (4)<br />

DMII Síntesis funcional – Síntesis RTL – A. Diéguez<br />

Area<br />

INV (1)<br />

NAND2 (2)<br />

NAND3 (3)<br />

AOI21 (3)<br />

NAND4 (4)<br />

DMII Síntesis funcional – Síntesis RTL – A. Diéguez<br />

Load-Dependent Delay<br />

INV (1) NAND2 (2) NAND3 (3)<br />

AOI21 NAND4<br />

INV (2) NAND2 (4) NAND3 (5)<br />

AOI21 NAND4<br />

INV (3) NAND2 (5) NAND3 (7)<br />

AOI21 NAND4<br />

INV (3) NAND2 (4) NAND3 (7)<br />

AOI21 NAND4<br />

INV (5) NAND2 (9) NAND3 (12)<br />

AOI21 NAND4<br />

Technology mapping (delay)<br />

Load-Dependent Delay<br />

INV (1) NAND2 (2) NAND3 (3)<br />

AOI21 NAND4<br />

INV (2) NAND2 (4) NAND3 (5)<br />

AOI21 NAND4<br />

INV (3) NAND2 (5) NAND3 (7)<br />

AOI21 NAND4<br />

INV (3) NAND2 (4) NAND3 (7)<br />

AOI21 NAND4<br />

INV (5) NAND2 (9) NAND3 0(12)<br />

AOI21 NAND40<br />

0<br />

0<br />

0<br />

0<br />

0<br />

0<br />

0<br />

0<br />

3<br />

2 2 + 2 = 4<br />

7<br />

MAX (7,3) + 7 = 14<br />

NAND3<br />

MAX (4,0,0) + 4 = 8<br />

MAX (8,0) + 5 = 13<br />

NAND3<br />

Area<br />

INV (1)<br />

NAND2 (2)<br />

NAND3 (3)<br />

AOI21 (3)<br />

NAND4 (4)<br />

DMII Síntesis funcional – Síntesis RTL – A. Diéguez<br />

Technology mapping (delay)<br />

Load-Dependent Delay<br />

INV (1) NAND2 (2) NAND3 (3)<br />

AOI21 NAND4<br />

INV (2) NAND2 (4) NAND3 (5)<br />

AOI21 NAND4<br />

INV (3) NAND2 (5) NAND3 (7)<br />

AOI21 NAND4<br />

2<br />

INV (3) NAND2 (4) NAND3 (7)<br />

AOI21 NAND4 0<br />

0<br />

0<br />

INV (5) NAND2 (9) NAND3 (12)<br />

AOI21 NAND4<br />

0<br />

0<br />

0<br />

0<br />

0<br />

0<br />

0<br />

0<br />

0<br />

0<br />

0<br />

0<br />

DMII Síntesis funcional – Síntesis RTL – A. Diéguez<br />

2<br />

2 + 1 = 3 MAX(3,0) + 2 = 5<br />

1<br />

1<br />

2 + 1 = 3<br />

3<br />

Síntesis ntesis física sica<br />

MAX( 5,1) + 2 = 7<br />

8<br />

MAX (3,0,0) + 3 = 6<br />

MAX( 8,0) + 2 =10<br />

MAX (3,1,0) + 3 = 6<br />

MAX (6,0) + 2 = 8

DMII Síntesis funcional – Síntesis RTL – A. Diéguez<br />

DMII Síntesis funcional – Síntesis RTL – A. Diéguez<br />

Particionado<br />

Algorítmos<br />

Algor tmos de biparticionado<br />

DMII Síntesis funcional – Síntesis RTL – A. Diéguez<br />

DMII Síntesis funcional – Síntesis RTL – A. Diéguez<br />

Particionado recursivo: recursivo:<br />

min-cut min cut<br />

Algorítmos<br />

Algor tmos de biparticionado

DMII Síntesis funcional – Síntesis RTL – A. Diéguez<br />

DMII Síntesis funcional – Síntesis RTL – A. Diéguez<br />

Algorítmos<br />

Algor tmos de biparticionado:<br />

biparticionado:<br />

Ejemplo K-L<br />

Floorplanning<br />

DMII Síntesis funcional – Síntesis RTL – A. Diéguez<br />

DMII Síntesis funcional – Síntesis RTL – A. Diéguez<br />

Floorplanning<br />

Floorplanning

DMII Síntesis funcional – Síntesis RTL – A. Diéguez<br />

Placement<br />

Mal placement Buen placement<br />

DMII Síntesis funcional – Síntesis RTL – A. Diéguez<br />

Placement iterativo: iterativo:<br />

Simulated annealing<br />

DMII Síntesis funcional – Síntesis RTL – A. Diéguez<br />

DMII Síntesis funcional – Síntesis RTL – A. Diéguez<br />

Placement iterativo: iterativo:<br />

Simulated annealing<br />

Estrategia clásica<br />

Placement iterativo: iterativo:<br />

Simulated annealing<br />

Recocido simulado

DMII Síntesis funcional – Síntesis RTL – A. Diéguez<br />

DMII Síntesis funcional – Síntesis RTL – A. Diéguez<br />

Routing<br />

Maze Routing<br />

Lee’s Algorithm<br />

DMII Síntesis funcional – Síntesis RTL – A. Diéguez<br />

DMII Síntesis funcional – Síntesis RTL – A. Diéguez<br />

Routing<br />

Routing detallado:<br />

detallado:<br />

Definiciones y modelos de asignación asignaci de capas<br />

• Entrada:<br />

– Dos vectores de la misma longitud que<br />

representan los pines en ambs la<strong>dos</strong> del<br />

canal.<br />

– Número de capas y modelo de conexión.<br />

• Salida:<br />

– Conexión de pines.<br />

– Minimización de la anchura del canal.<br />

– Minimización del número de vias.<br />

Ejemplo: (13002110)<br />

(30120300)<br />

(0 = no terminal)<br />

Channel routing<br />

+<br />

Switchbox routing<br />

1. Fix the terminals between A & B<br />

2. Route B, C, then D (channel)<br />

3. Route A (switchbox)

Left-Edge Algorithm<br />

DMII Síntesis funcional – Síntesis RTL – A. Diéguez<br />

Left-Edge Left Edge Channel Routing Algorithm<br />

Constrained Left-Edge Algorithm