You also want an ePaper? Increase the reach of your titles

YUMPU automatically turns print PDFs into web optimized ePapers that Google loves.

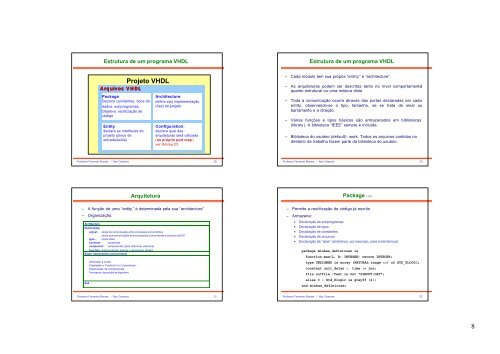

Estrutura de um programa <strong>VHDL</strong><br />

Estrutura de um programa <strong>VHDL</strong><br />

Projeto <strong>VHDL</strong><br />

Arquivos <strong>VHDL</strong><br />

Package:<br />

Declara constantes, tipos de<br />

dados, subprogramas.<br />

Objetivo: reutilização de<br />

código<br />

Entity:<br />

declara as interfaces do<br />

projeto (pinos de<br />

entrada/saída)<br />

Architecture:<br />

define a(s) implementação<br />

(ões) do projeto<br />

Configuration:<br />

declara qual das<br />

arquiteturas será utilizada<br />

(no próprio port map)<br />

ver lâmina 23<br />

– Cada módulo tem sua própria “entity” e “architecture”.<br />

– As arquiteturas podem ser descritas tanto no nível comportamental<br />

quanto estrutural ou uma mistura disto.<br />

– Toda a comunicação ocorre através das portas declaradas em cada<br />

entity, observando-se o tipo, tamanho, se se trata de sinal ou<br />

barramento e a direção.<br />

– Várias funções e tipos básicos são armazenados em bibliotecas<br />

(library). A biblioteca “IEEE” sempre é incluída.<br />

– Biblioteca do usuário (default): work. Todos os arquivos contidos no<br />

diretório de trabalho fazem parte da biblioteca do usuário.<br />

Professor Fernando Moraes / Ney Calazans<br />

29<br />

Professor Fernando Moraes / Ney Calazans<br />

30<br />

Arquitetura<br />

Package (1/3)<br />

– A função de uma “entity ” é determinada pela sua “architecture”<br />

– Organização:<br />

Architecture<br />

Declarações<br />

signal - sinais de comunicação entre processos concorrentes<br />

sinais que comunicação entre processos concorrentes e os pinos de E/S<br />

type - novos tipos<br />

constant - constantes<br />

component - componentes (para descrever estrutura)<br />

function - Subprogramas ( apenas a declaração destes)<br />

Begin (declarações concorrentes)<br />

End<br />

Atribuição a sinais<br />

Chamadas a “functions” e a “ procedures”<br />

Instanciação de Componentes<br />

Processos: descrição de algoritmo<br />

– Permite a reutilização de código já escrito<br />

– Armazena:<br />

• Declaração de subprogramas<br />

• Declaração de tipos<br />

• Declaração de constantes<br />

• Declaração de arquivos<br />

• Declaração de “alias” (sinônimos, por exemplo, para mnemônicos)<br />

package minhas_definicoes is<br />

function max(L, R: INTEGER) return INTEGER;<br />

type UNSIGNED is array (NATURAL range ) of STD_ULOGIC;<br />

constant unit_delay : time := 1ns;<br />

file outfile :Text is Out "SIMOUT.DAT";<br />

alias C : Std_Ulogic is grayff (2);<br />

end minhas_definicoes;<br />

Professor Fernando Moraes / Ney Calazans<br />

31<br />

Professor Fernando Moraes / Ney Calazans<br />

32<br />

8