Programa Completo del Curso

Programa Completo del Curso

Programa Completo del Curso

- No tags were found...

You also want an ePaper? Increase the reach of your titles

YUMPU automatically turns print PDFs into web optimized ePapers that Google loves.

1<strong>Programa</strong> de MaestríaUniversidad Nacional de Entre RíosFacultad de IngenieríaOro Verde, E. R.República ArgentinaMaestría en Ingeniería BiomédicaCarrera: Maestría en Ingeniería Biomédica<strong>Curso</strong> de Posgrado: Tópicos de electrónica e informática aplicadas a la Ingeniería Biomédica:<strong>Programa</strong>ción de dispositivos lógicos programables FPGA mediante el lenguaje VHDLCarga Horaria 1 : 90 horasDocente/s a cargo: Alfredo Rosado MuñozSemestre: 1º Año: 2010Modalidad 2 : <strong>Curso</strong> teórico-prácticoCarácter 3 : específico/optativo<strong>Programa</strong> Analítico<strong>Programa</strong>ción de dispositivos lógicos programables FPGA mediante el lenguaje VHDLTema 1. Introducción al VHDL y los dispositivos FPGA. Elementos de concepción <strong>del</strong> diseño, tipos de datos, instruccioneselementales. Tipos de dispositivos.Laboratorio: Primera sesión práctica, con un ejemplo muy sencillo que permita conocer el flujo de diseño de un sistema lógicoprogramables, desde el diseño VHDL a la implementación en placa hardware.Tema 2. Introducción al VHDL II. Posibilidades que ofrece el lenguaje: sintaxis, instrucciones, simulación.Laboratorio: Práctica 1. Diseño y simulación. Se conocerá el procedimiento necesario para el diseño y simulación, sinnecesidad de disponer de hardware asociado.Tema 3. VHDL para síntesis. Introducción de conceptos de VHDL. Código sintetizable. Pautas de diseño para facilitar laimplementados en hardware.Laboratorio: Práctica 2. Síntesis de un sistema secuencial.Tema 4. VHDL para síntesis II. Conocimientos necesarios para la síntesis mediante descripciones VHDL. Estructuras típicasde VHDL orientadas a la generación específica de Hardware.Laboratorio: Práctica 3. Se realiza una práctica sencilla para asentar las bases de VHDL para síntesis: entradas bidireccionales,triestado, memoria interna RAM/ROM, etc.Tema 5. Práctica 4. Sesión completa dedicada a la implementación de un sistema complejo donde es necesaria la comunicacióncon otros dispositivos electrónicos, un conversor A/D y un D/A.Tema 6. Implementación de Sistemas en FPGA basados en entornos de diseño de alto nivel. Descripción este tipo de entornos.Ventajas e inconvenientes.Sesión práctica: Utilización de Xilinx EDK para generación y programación <strong>del</strong> microprocesador Microblaze.Tema 7. Propuestas de proyectos. Una vez familiarizados con VHDL, síntesis e implementación, se proponen proyectos para

desarrollar de forma individual o de a dos alumnos. Esta jornada se dedica a la definición <strong>del</strong> proyecto mediante reunionesindividuales de aprox. 20 minutos por cada proyecto.Tema 8. Trabajo de proyecto. Se dedica a trabajar sobre la propuesta, diseñando y verificando el sistema a implementar.Tema 9. Trabajo de proyecto. Se dedica a trabajar sobre la propuesta, diseñando y verificando el sistema a implementar. Serealiza una verificación <strong>del</strong> cumplimiento de los objetivos.Tema 10. Presentación de los trabajos. Cada trabajo será presentado al profesor y al resto de la clase, con una exposición oral yposterior demostración práctica de los resultados obtenidos.2Universidad Nacional deEntre RíosFacultad de IngenieríaOro Verde, E. R.República ArgentinaBIBLIOGRAFIA1. Abramovici, M.; Brever, M.; Friedman, A.: "Digital Systems Testing and Testable Design". IEEE Press. 1990.2. Alfonso-Pérez, S.; Soto, E.; Fernández, S.: “Diseño de sistemas digitales con VHDL”. Thomson-Paraninfo, 2002.3. Altera. Data Book. 1995. http://www.altera.com/literature/lit-index.html4. Deschamps, J.P.: "Síntesis de circuitos digitales. Un enfoque algorítmico". Thomson-Paraninfo, 2002.5. Deschamps, J.P.: "Diseño de circuitos integrados de aplicación específica ASIC". Paraninfo, 1993.6. Fabricius, E.: "Introduction to VLSI Design". McGraw Hill, 1990.7. Floyd, T.L.: "Fundamentos de Sistemas Digitales.". Prentice Hall, 1997.8. Lipsett-Schaefer-Ussery: "VHDL: Hardware Description And Design". Kluwer Academic, 1989.9. Mandado, E.; Jacobo Álvarez, L.; Valdés M. D.: "Dispositivos Lógicos <strong>Programa</strong>bles y sus aplicaciones". Thomson-Paraninfo, 2002.10. Oldfield, J. ; Dorf, R. "Field Programmable Gate Array". John Wiley. 1995.11. Pardo, F.; Boluda, J.A. “VHDL: Lenguaje para síntesis y mo<strong>del</strong>ado de circuitos”. Rama, 1999.12. Pucknell, D.; Eshraghian, K. "Basic VLSI Design". Prentice-Hall. 1994.13. Schilling-Belove. "Circuitos electrónicos discretos e integrados". Mc Graw-Hill, 1993.14. The Programmable Logic Jump Station. http://www.optimagic.com15. Wakerly, J.P. "Diseño Digital: Principios y Prácticas". Prentice Hall, 1992.16. Xilinx. "The Programmable Logic Data Book". 1995. http://www.xilinx.com/partinfo/databook.htm17. Zeidman, B. “Designing with FPGA & CPLD”. CMP Books. 2002.18. Zwolinski, M. “Digital System Design with VHDL”. Pearson Education. 2000.

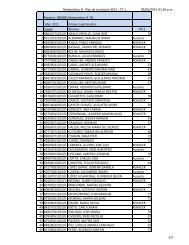

3Universidad Nacional deEntre RíosFacultad de IngenieríaOro Verde, E. R.República ArgentinaPLANIFICACIÓN DEL CURSOObjetivos Generales:- Que el estudiante pueda diseñar de forma autónoma sistemas de complejidad media en un FPGA.- Que el estudiante sea capaz de comprender los recursos de VHDL para conseguir los objetivos necesarios de un buen diseñológico.Objetivos Particulares:- Aprender el lenguaje VHDL.- Conocer las FPGA y las aplicaciones que se pueden realizar con ellas.- Utilizar de forma práctica el hardware FPGA, programando y verificando la programación realizada bajo PC.- Emplear un dispositivo FPGA para realizar tareas de interconexión entre dispositivos electrónicos, realizando diversaslabores de interfaz entre ellos.Metodología de Trabajo:Eminentemente práctica, 80% <strong>del</strong> tiempo se emplea en el laboratorio, con un sistema de aprendizaje de “aprenderhaciendo” (learn by doing), con explicaciones teóricas continuamente apoyadas en la realización práctica de ejemplos. Losalumnos deberán realizar un trabajo final que irán avanzando entre las clases mostrando avances y consultando las dudas entrecada una de las clases. Esta actividad le demandará 50 horas de trabajo.Equipo docente:Dr. Alfredo Rosado Muñoz y colaboradoresCronograma <strong>del</strong> <strong>Curso</strong>:La organización <strong>del</strong> curso está pensada en 10 sesiones de 4 horas de duración a lo largo de dos semanas y media,cuatro días durante las dos primeras semanas, y dos días la última semana. Comienzo <strong>del</strong> curso: 23 de Agosto de 2010.Días de dictado: lunes, martes, jueves y viernes de 17 a 21 hs.Condiciones de Regularidad y Promoción:El curso se aprobará con la presentación de los trabajos y una asistencia al 70% de las clases. Cada trabajo serápresentado al profesor y al resto de la clase, con una exposición oral y posterior demostración práctica de los resultadosobtenidos. El trabajo final será presentado en la última clase.Infraestructura necesaria:El curso está enfocado de una forma eminentemente práctica, con un uso intensivo <strong>del</strong> laboratorio, por lo que lapráctica totalidad de sesiones se desarrollarían en un laboratorio con un equipamiento típico de electrónica (generador deseñales, osciloscopio, fuente de alimentación, etc.) y PC con software Xilinx ISE versión 9 o superior, y Xilinx EDK.