Digitale electronica en processoren Digitale electronica en ...

Digitale electronica en processoren Digitale electronica en ...

Digitale electronica en processoren Digitale electronica en ...

Create successful ePaper yourself

Turn your PDF publications into a flip-book with our unique Google optimized e-Paper software.

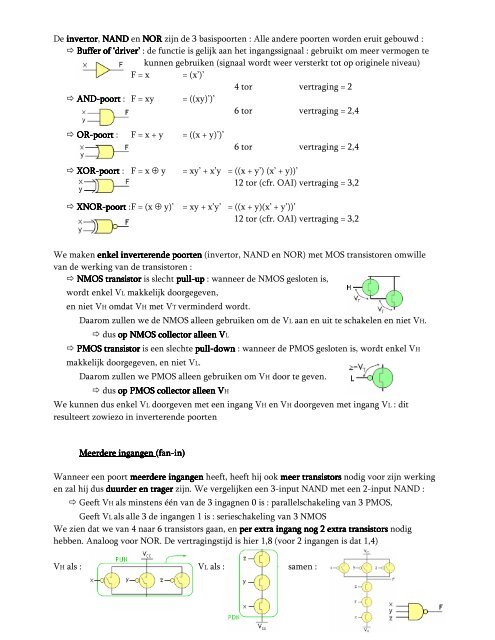

De invertor invertor, invertor NAND <strong>en</strong> NOR NOR zijn de 3 basispoort<strong>en</strong> : Alle andere poort<strong>en</strong> word<strong>en</strong> eruit gebouwd :<br />

Buffer of ‘driver’ : de functie is gelijk aan het ingangssignaal : gebruikt om meer vermog<strong>en</strong> te<br />

kunn<strong>en</strong> gebruik<strong>en</strong> (signaal wordt weer versterkt tot op originele niveau)<br />

F = x = (x’)’<br />

4 tor vertraging = 2<br />

AND AND-poort AND<br />

poort poort : F = xy = ((xy)’)’<br />

6 tor vertraging = 2,4<br />

OR OR-poort OR poort : F = x + y = ((x + y)’)’<br />

6 tor vertraging = 2,4<br />

XOR XOR-poort XOR<br />

poort poort : F = x ⊕ y = xy’ + x’y = ((x + y’) (x’ + y))’<br />

12 tor (cfr. OAI) vertraging = 3,2<br />

XNOR XNOR-poort<br />

XNOR<br />

poort : F = (x ⊕ y)’ = xy + x’y’ = ((x + y)(x’ + y’))’<br />

12 tor (cfr. OAI) vertraging = 3,2<br />

We mak<strong>en</strong> <strong>en</strong>kel inverter<strong>en</strong>de inverter<strong>en</strong>de poort<strong>en</strong> (invertor, NAND <strong>en</strong> NOR) met MOS transistor<strong>en</strong> omwille<br />

van de werking van de transistor<strong>en</strong> :<br />

NMOS transistor transistor is slecht pull pull-up pull<br />

up up : wanneer de NMOS geslot<strong>en</strong> is,<br />

wordt <strong>en</strong>kel VL makkelijk doorgegev<strong>en</strong>,<br />

<strong>en</strong> niet VH omdat VH met VT verminderd wordt.<br />

Daarom zull<strong>en</strong> we de NMOS alle<strong>en</strong> gebruik<strong>en</strong> om de VL aan <strong>en</strong> uit te schakel<strong>en</strong> <strong>en</strong> niet VH.<br />

dus op NMOS NMOS collector alle<strong>en</strong> alle<strong>en</strong> VVL<br />

V<br />

PMOS transistor transistor is e<strong>en</strong> slechte pull pull-down pull<br />

down : wanneer de PMOS geslot<strong>en</strong> is, wordt <strong>en</strong>kel VH<br />

makkelijk doorgegev<strong>en</strong>, <strong>en</strong> niet VL.<br />

Daarom zull<strong>en</strong> we PMOS alle<strong>en</strong> gebruik<strong>en</strong> om VH door te gev<strong>en</strong>.<br />

dus op PMOS collector alle<strong>en</strong> VVH<br />

V<br />

We kunn<strong>en</strong> dus <strong>en</strong>kel VL doorgev<strong>en</strong> met e<strong>en</strong> ingang VH <strong>en</strong> VH doorgev<strong>en</strong> met ingang VL : dit<br />

resulteert zowiezo in inverter<strong>en</strong>de poort<strong>en</strong><br />

Meerdere Meerdere ingang<strong>en</strong> ingang<strong>en</strong> (fan (fan-in) (fan (fan in) in)<br />

Wanneer e<strong>en</strong> poort meerdere ingang<strong>en</strong> heeft, heeft hij ook meer transistors nodig voor zijn werking<br />

<strong>en</strong> zal hij dus duurder duurder <strong>en</strong> trager zijn. We vergelijk<strong>en</strong> e<strong>en</strong> 3-input NAND met e<strong>en</strong> 2-input NAND :<br />

Geeft VH als minst<strong>en</strong>s één van de 3 ingagn<strong>en</strong> 0 is : parallelschakeling van 3 PMOS,<br />

Geeft VL als alle 3 de ingang<strong>en</strong> 1 is : serieschakeling van 3 NMOS<br />

We zi<strong>en</strong> dat we van 4 naar 6 transistors gaan, <strong>en</strong> per extra extra ingang ingang ingang nog nog 2 2 extra extra transistors transistors nodig<br />

hebb<strong>en</strong>. Analoog voor NOR. De vertragingstijd is hier 1,8 (voor 2 ingang<strong>en</strong> is dat 1,4)<br />

VH als : VL als : sam<strong>en</strong> :