Digitale electronica en processoren Digitale electronica en ...

Digitale electronica en processoren Digitale electronica en ...

Digitale electronica en processoren Digitale electronica en ...

You also want an ePaper? Increase the reach of your titles

YUMPU automatically turns print PDFs into web optimized ePapers that Google loves.

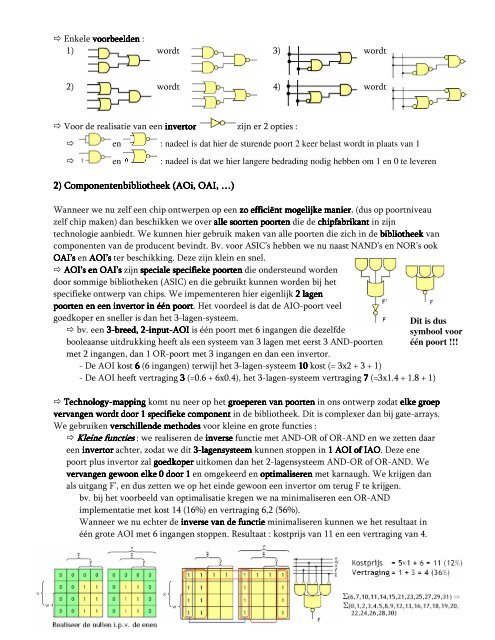

Enkele voorbeeld<strong>en</strong> :<br />

1) wordt 3) wordt<br />

2) wordt 4) wordt<br />

Voor de realisatie van e<strong>en</strong> invertor zijn er 2 opties :<br />

<strong>en</strong> : nadeel is dat hier de stur<strong>en</strong>de poort 2 keer belast wordt in plaats van 1<br />

<strong>en</strong> : nadeel is dat we hier langere bedrading nodig hebb<strong>en</strong> om 1 <strong>en</strong> 0 te lever<strong>en</strong><br />

2) ) Compon<strong>en</strong>t<strong>en</strong>bibliotheek Compon<strong>en</strong>t<strong>en</strong>bibliotheek (AOi, (AOi, OAI OAI, OAI , …)<br />

Wanneer we nu zelf e<strong>en</strong> chip ontwerp<strong>en</strong> op e<strong>en</strong> zo efficiënt mogelijke mogelijke manier manier, manier<br />

(dus op poortniveau<br />

zelf chip mak<strong>en</strong>) dan beschikk<strong>en</strong> we over al alle al<br />

le soort<strong>en</strong> soort<strong>en</strong> poort<strong>en</strong> poort<strong>en</strong> poort<strong>en</strong> die de chipfabrikant<br />

chipfabrikant in zijn<br />

technologie aanbiedt. We kunn<strong>en</strong> hier gebruik mak<strong>en</strong> van alle poort<strong>en</strong> die zich in de bibliotheek bibliotheek van<br />

compon<strong>en</strong>t<strong>en</strong> van de produc<strong>en</strong>t bevindt. Bv. voor ASIC’s hebb<strong>en</strong> we nu naast NAND’s <strong>en</strong> NOR’s ook<br />

OAI’s OAI’s <strong>en</strong> AOI’s ter beschikking. Deze zijn klein <strong>en</strong> snel.<br />

AOI’s <strong>en</strong> OAI’s zijn speciale speciale specifieke poort<strong>en</strong> die ondersteund word<strong>en</strong><br />

door sommige bibliothek<strong>en</strong> (ASIC) <strong>en</strong> die gebruikt kunn<strong>en</strong> word<strong>en</strong> bij het<br />

specifieke ontwerp van chips. We impem<strong>en</strong>ter<strong>en</strong> hier eig<strong>en</strong>lijk 2 lag<strong>en</strong><br />

poort<strong>en</strong> oort<strong>en</strong> <strong>en</strong> e<strong>en</strong> invertor in één poort poort. poort<br />

Het voordeel is dat de AIO-poort veel<br />

goedkoper <strong>en</strong> sneller is dan het 3-lag<strong>en</strong>-systeem.<br />

Dit is dus<br />

bv. e<strong>en</strong> 3-breed, breed, 22-input<br />

2<br />

input input-AOI input AOI is één poort met 6 ingang<strong>en</strong> die dezelfde<br />

symbool voor<br />

booleaanse uitdrukking heeft als e<strong>en</strong> systeem van 3 lag<strong>en</strong> met eerst 3 AND-poort<strong>en</strong> één poort !!!<br />

met 2 ingang<strong>en</strong>, dan 1 OR-poort met 3 ingang<strong>en</strong> <strong>en</strong> dan e<strong>en</strong> invertor.<br />

- De AOI kost 6 (6 ingang<strong>en</strong>) terwijl het 3-lag<strong>en</strong>-systeem 10 kost (= 3x2 + 3 + 1)<br />

- De AOI heeft vertraging 3 (=0.6 + 6x0.4), het 3-lag<strong>en</strong>-systeem vertraging 7 (=3x1.4 + 1.8 + 1)<br />

Technology Technology-mapping<br />

Technology<br />

mapping komt nu neer op het groeper<strong>en</strong> van poort<strong>en</strong> in ons ontwerp zodat elke groep<br />

vervang<strong>en</strong> vervang<strong>en</strong> wordt wordt door door 1 specifieke compon<strong>en</strong>t in de bibliotheek. Dit is complexer dan bij gate-arrays.<br />

We gebruik<strong>en</strong> verschill<strong>en</strong>de methodes voor kleine <strong>en</strong> grote functies :<br />

Kleine Kl Kl Kleine<br />

eine eine functies functies functies functies : we realiser<strong>en</strong> de inverse functie met AND-OR of OR-AND <strong>en</strong> we zett<strong>en</strong> daar<br />

e<strong>en</strong> invertor achter, zodat we dit 3-lag<strong>en</strong>systeem<br />

lag<strong>en</strong>systeem<br />

lag<strong>en</strong>systeem kunn<strong>en</strong> stopp<strong>en</strong> in 1 AOI of of IAO IAO. IAO<br />

Deze <strong>en</strong>e<br />

poort plus invertor zal goedkoper uitkom<strong>en</strong> dan het 2-lag<strong>en</strong>systeem AND-OR of OR-AND. We<br />

vervang<strong>en</strong> vervang<strong>en</strong> gewoon gewoon elke elke 0 0 door door 1 1 <strong>en</strong> omgekeerd <strong>en</strong> optimaliser<strong>en</strong><br />

optimaliser<strong>en</strong> met karnaugh. We krijg<strong>en</strong> dan<br />

als uitgang F’, <strong>en</strong> dus zett<strong>en</strong> we op het einde gewoon e<strong>en</strong> invertor om terug F te krijg<strong>en</strong>.<br />

bv. bij het voorbeeld van optimalisatie kreg<strong>en</strong> we na minimaliser<strong>en</strong> e<strong>en</strong> OR-AND<br />

implem<strong>en</strong>tatie met kost 14 (16%) <strong>en</strong> vertraging 6,2 (56%).<br />

Wanneer we nu echter de inverse van de functie minimaliser<strong>en</strong> kunn<strong>en</strong> we het resultaat in<br />

één grote AOI met 6 ingang<strong>en</strong> stopp<strong>en</strong>. Resultaat : kostprijs van 11 <strong>en</strong> e<strong>en</strong> vertraging van 4.