Digitale electronica en processoren Digitale electronica en ...

Digitale electronica en processoren Digitale electronica en ...

Digitale electronica en processoren Digitale electronica en ...

You also want an ePaper? Increase the reach of your titles

YUMPU automatically turns print PDFs into web optimized ePapers that Google loves.

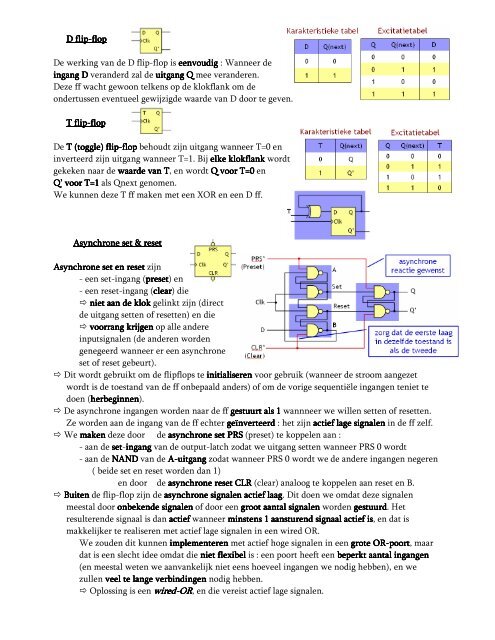

D D flip flip-flop flip flip flop<br />

De werking van de D flip-flop is e<strong>en</strong>voudig : Wanneer de<br />

ingang ingang D D veranderd zal de uitgang Q mee verander<strong>en</strong>.<br />

Deze ff wacht gewoon telk<strong>en</strong>s op de klokflank om de<br />

ondertuss<strong>en</strong> ev<strong>en</strong>tueel gewijzigde waarde van D door te gev<strong>en</strong>.<br />

T T flip flip-flop flip flop<br />

De T T (toggle) (toggle) flip flip-flop flip lop behoudt zijn uitgang wanneer T=0 <strong>en</strong><br />

inverteerd zijn uitgang wanneer T=1. Bij elke klokflank wordt<br />

gekek<strong>en</strong> naar de waarde van TT,<br />

T<br />

<strong>en</strong> wordt Q voor T=0 <strong>en</strong><br />

Q’ Q’ Q’ voor voor T=1 T=1 als Qnext g<strong>en</strong>om<strong>en</strong>.<br />

We kunn<strong>en</strong> deze T ff mak<strong>en</strong> met e<strong>en</strong> XOR <strong>en</strong> e<strong>en</strong> D ff.<br />

Asynchro Asynchrone Asynchro Asynchrone<br />

ne set & & reset<br />

Asynchrone Asynchrone set set <strong>en</strong> <strong>en</strong> <strong>en</strong> reset reset zijn<br />

- e<strong>en</strong> set-ingang (preset preset preset) preset <strong>en</strong><br />

- e<strong>en</strong> reset-ingang (clear clear clear) clear die<br />

niet aan de de klok gelinkt zijn (direct<br />

de uitgang sett<strong>en</strong> of resett<strong>en</strong>) <strong>en</strong> die<br />

voorrang krijg<strong>en</strong> op alle andere<br />

inputsignal<strong>en</strong> (de ander<strong>en</strong> word<strong>en</strong><br />

g<strong>en</strong>egeerd wanneer er e<strong>en</strong> asynchrone<br />

set of reset gebeurt).<br />

Dit wordt gebruikt om de flipflops te initialiser<strong>en</strong> voor gebruik (wanneer de stroom aangezet<br />

wordt is de toestand van de ff onbepaald anders) of om de vorige sequ<strong>en</strong>tiële ingang<strong>en</strong> t<strong>en</strong>iet te<br />

do<strong>en</strong> (herbeginn<strong>en</strong><br />

herbeginn<strong>en</strong><br />

herbeginn<strong>en</strong>).<br />

herbeginn<strong>en</strong><br />

De asynchrone ingang<strong>en</strong> word<strong>en</strong> naar de ff gestuurt als als 1 1 wannneer we will<strong>en</strong> sett<strong>en</strong> of resett<strong>en</strong>.<br />

Ze word<strong>en</strong> aan de ingang van de ff echter geïnverteerd : het zijn actief lage signal<strong>en</strong> signal<strong>en</strong> in de ff zelf.<br />

We mak<strong>en</strong> mak<strong>en</strong> deze door de asynchrone set PPRS<br />

P<br />

RS (preset) te koppel<strong>en</strong> aan :<br />

- aan de set set-ingang set<br />

ingang van de output-latch zodat we uitgang sett<strong>en</strong> wanneer PRS 0 wordt<br />

- aan de NAND van de A-uitgang uitgang zodat wanneer PRS 0 wordt we de andere ingang<strong>en</strong> neger<strong>en</strong><br />

( beide set <strong>en</strong> reset word<strong>en</strong> dan 1)<br />

<strong>en</strong> door de asynchrone reset reset CLR (clear) analoog te koppel<strong>en</strong> aan reset <strong>en</strong> B.<br />

Buit<strong>en</strong> de flip-flop zijn de asynchrone signal<strong>en</strong> actief actief actief laag laag. laag<br />

Dit do<strong>en</strong> we omdat deze signal<strong>en</strong><br />

meestal door onbek<strong>en</strong>de onbek<strong>en</strong>de signal<strong>en</strong> of door e<strong>en</strong> groot groot aantal signal<strong>en</strong> word<strong>en</strong> gestuurd gestuurd. gestuurd<br />

Het<br />

resulter<strong>en</strong>de signaal is dan actief wanneer minst<strong>en</strong>s 1 aanstur<strong>en</strong>d signaal actief is is, is<br />

<strong>en</strong> dat is<br />

makkelijker te realiser<strong>en</strong> met actief lage signal<strong>en</strong> in e<strong>en</strong> wired OR.<br />

We zoud<strong>en</strong> dit kunn<strong>en</strong> implem<strong>en</strong>ter<strong>en</strong> met actief hoge signal<strong>en</strong> in e<strong>en</strong> grote OR OR-poort OR poort poort, poort maar<br />

dat is e<strong>en</strong> slecht idee omdat die niet niet flexibel is : e<strong>en</strong> poort heeft e<strong>en</strong> beperkt aantal aantal ingang<strong>en</strong><br />

ingang<strong>en</strong><br />

(<strong>en</strong> meestal wet<strong>en</strong> we aanvankelijk niet e<strong>en</strong>s hoeveel ingang<strong>en</strong> we nodig hebb<strong>en</strong>), <strong>en</strong> we<br />

zull<strong>en</strong> veel veel te te lange lange verbinding<strong>en</strong> verbinding<strong>en</strong> nodig hebb<strong>en</strong>.<br />

Oplossing is e<strong>en</strong> wired----OR wired wired wired OR, OR OR <strong>en</strong> die vereist actief lage signal<strong>en</strong>.