Digitale electronica en processoren Digitale electronica en ...

Digitale electronica en processoren Digitale electronica en ...

Digitale electronica en processoren Digitale electronica en ...

You also want an ePaper? Increase the reach of your titles

YUMPU automatically turns print PDFs into web optimized ePapers that Google loves.

To Toepassing<strong>en</strong><br />

To epassing<strong>en</strong> :<br />

Voor prototypes & medium volumes ( 5 M poort<strong>en</strong>) @ 400 MHz (in 2004)<br />

FPGA FPGA : volledige programmeerbare chip :<br />

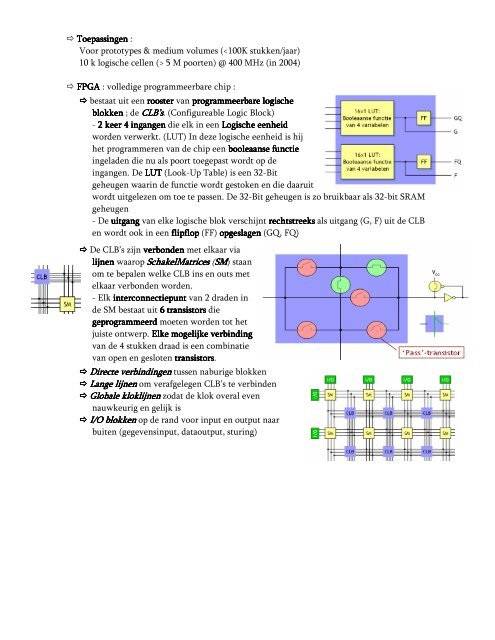

bestaat uit e<strong>en</strong> rooster rooster van programmeerbare logische<br />

blokk<strong>en</strong> blokk<strong>en</strong> ; de CLB’s. CLB’s CLB’s CLB’s (Configureable Logic Block)<br />

- 2 keer 4 ingang<strong>en</strong> die elk in e<strong>en</strong> Logische e<strong>en</strong>heid<br />

word<strong>en</strong> verwerkt. (LUT) In deze logische e<strong>en</strong>heid is hij<br />

het programmer<strong>en</strong> van de chip e<strong>en</strong> booleaanse functie functie<br />

ingelad<strong>en</strong> die nu als poort toegepast wordt op de<br />

ingang<strong>en</strong>. De LUT LUT (Look-Up Table) is e<strong>en</strong> 32-Bit<br />

geheug<strong>en</strong> waarin de functie wordt gestok<strong>en</strong> <strong>en</strong> die daaruit<br />

wordt uitgelez<strong>en</strong> om toe te pass<strong>en</strong>. De 32-Bit geheug<strong>en</strong> is zo bruikbaar als 32-bit SRAM<br />

geheug<strong>en</strong><br />

- De uitgang uitgang van elke logische blok verschijnt rechtstreeks als uitgang (G, F) uit de CLB<br />

<strong>en</strong> wordt ook in e<strong>en</strong> flipflop (FF) opgeslag<strong>en</strong> opgeslag<strong>en</strong> opgeslag<strong>en</strong> (GQ, FQ)<br />

De CLB’s zijn verbond<strong>en</strong> met elkaar via<br />

lijn<strong>en</strong> lijn<strong>en</strong> lijn<strong>en</strong> waarop SchakelMatrices<br />

SchakelM SchakelM SchakelMatrices<br />

atrices atrices SM) (SM SM SM staan<br />

om te bepal<strong>en</strong> welke CLB ins <strong>en</strong> outs met<br />

elkaar verbond<strong>en</strong> word<strong>en</strong>.<br />

- Elk interconnectiepunt<br />

nterconnectiepunt van 2 drad<strong>en</strong> in<br />

de SM bestaat uit 6 transistors die<br />

geprogrammeerd<br />

eprogrammeerd moet<strong>en</strong> word<strong>en</strong> tot het<br />

juiste ontwerp. Elke mogelijke verbinding<br />

van de 4 stukk<strong>en</strong> draad is e<strong>en</strong> combinatie<br />

van op<strong>en</strong> <strong>en</strong> geslot<strong>en</strong> transistors transistors. transistors<br />

Directe Directe Directe Directe verbindingeee<strong>en</strong>nnn verbinding verbinding verbinding tuss<strong>en</strong> naburige blokk<strong>en</strong><br />

Lange Lange Lange Lange lijn<strong>en</strong> lijn<strong>en</strong> lijn<strong>en</strong> lijn<strong>en</strong> om verafgeleg<strong>en</strong> CLB’s te verbind<strong>en</strong><br />

Globale Globale Globale Globale kloklijn<strong>en</strong> kloklijn<strong>en</strong> kloklijn<strong>en</strong> kloklijn<strong>en</strong> zodat de klok overal ev<strong>en</strong><br />

nauwkeurig <strong>en</strong> gelijk is<br />

I/O I/O I/O I/O blokk<strong>en</strong> blokk<strong>en</strong> blokk<strong>en</strong> blokk<strong>en</strong> op de rand voor input <strong>en</strong> output naar<br />

buit<strong>en</strong> (gegev<strong>en</strong>sinput, dataoutput, sturing)