Digitale electronica en processoren Digitale electronica en ...

Digitale electronica en processoren Digitale electronica en ...

Digitale electronica en processoren Digitale electronica en ...

You also want an ePaper? Increase the reach of your titles

YUMPU automatically turns print PDFs into web optimized ePapers that Google loves.

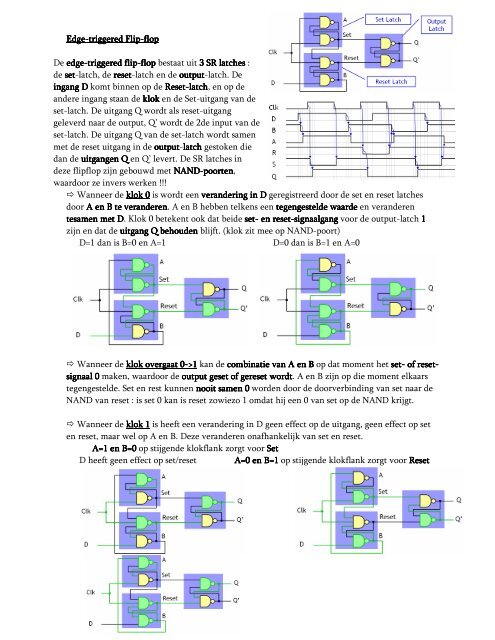

Edge Edge-triggered Edge triggered Flip Flip-flop Flip<br />

flop<br />

De edge edge-triggered edge triggered flip flip-flop flip<br />

flop bestaat uit 3 SR latches :<br />

de set set-latch, set<br />

de reset reset-latch reset<br />

<strong>en</strong> de output output-latch. output<br />

De<br />

ingang ingang D D komt binn<strong>en</strong> op de Reset Reset-latch Reset<br />

latch latch, latch <strong>en</strong> op de<br />

andere ingang staan de klok <strong>en</strong> de Set-uitgang van de<br />

set-latch. De uitgang Q wordt als reset-uitgang<br />

geleverd naar de output, Q’ wordt de 2de input van de<br />

set-latch. De uitgang Q van de set-latch wordt sam<strong>en</strong><br />

met de reset uitgang in de output output-latch<br />

output<br />

latch gestok<strong>en</strong> die<br />

dan de uitgang<strong>en</strong> Q <strong>en</strong> Q’ levert. De SR latches in<br />

deze flipflop zijn gebouwd met NAND NAND-poort<strong>en</strong><br />

NAND<br />

poort<strong>en</strong> poort<strong>en</strong>, poort<strong>en</strong><br />

waardoor ze invers werk<strong>en</strong> !!!<br />

Wanneer de klok 0 is wordt e<strong>en</strong> verandering in D geregistreerd door de set <strong>en</strong> reset latches<br />

door A A <strong>en</strong> B te verander<strong>en</strong> verander<strong>en</strong>. verander<strong>en</strong><br />

A <strong>en</strong> B hebb<strong>en</strong> telk<strong>en</strong>s e<strong>en</strong> teg<strong>en</strong>gestelde waarde <strong>en</strong> verander<strong>en</strong><br />

tesam<strong>en</strong> tesam<strong>en</strong> tesam<strong>en</strong> met DD.<br />

D<br />

Klok 0 betek<strong>en</strong>t ook dat beide set set- set<br />

<strong>en</strong> reset reset-signaalgang<br />

reset<br />

signaalgang voor de output-latch 1<br />

zijn <strong>en</strong> dat de uitgang Q behoud<strong>en</strong> blijft. (klok zit mee op NAND-poort)<br />

D=1 dan is B=0 <strong>en</strong> A=1 D=0 dan is B=1 <strong>en</strong> A=0<br />

Wanneer de klok overgaat 00->1<br />

0<br />

>1 kan de comb combinatie comb<br />

inatie van A <strong>en</strong> B op dat mom<strong>en</strong>t het set set- set<br />

of reset-<br />

signaal signaal 0 0 mak<strong>en</strong>, waardoor de output output geset of gereset wordt wordt. wordt A <strong>en</strong> B zijn op die mom<strong>en</strong>t elkaars<br />

teg<strong>en</strong>gestelde. Set <strong>en</strong> rest kunn<strong>en</strong> nooit sam<strong>en</strong> 0 word<strong>en</strong> door de doorverbinding van set naar de<br />

NAND van reset : is set 0 kan is reset zowiezo 1 omdat hij e<strong>en</strong> 0 van set op de NAND krijgt.<br />

Wanneer de klok 1 is heeft e<strong>en</strong> verandering in D ge<strong>en</strong> effect op de uitgang, ge<strong>en</strong> effect op set<br />

<strong>en</strong> reset, maar wel op A <strong>en</strong> B. Deze verander<strong>en</strong> onafhankelijk van set <strong>en</strong> reset.<br />

A=1 A=1 A=1 e<strong>en</strong><br />

e n B=0 op stijg<strong>en</strong>de klokflank zorgt voor Set<br />

D heeft ge<strong>en</strong> effect op set/reset A=0 <strong>en</strong> B=1 op stijg<strong>en</strong>de klokflank zorgt voor Reset eset