Teoria - LSI - USP

Teoria - LSI - USP

Teoria - LSI - USP

Create successful ePaper yourself

Turn your PDF publications into a flip-book with our unique Google optimized e-Paper software.

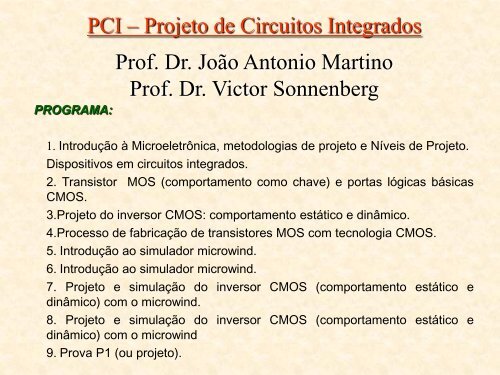

PCI – Projeto de Circuitos Integrados<br />

PROGRAMA:<br />

Prof. Dr. João Antonio Martino<br />

Prof. Dr. Victor Sonnenberg<br />

1. Introdução à Microeletrônica, metodologias de projeto e Níveis de Projeto.<br />

Dispositivos em circuitos integrados.<br />

2. Transistor MOS (comportamento como chave) e portas lógicas básicas<br />

CMOS.<br />

3.Projeto do inversor CMOS: comportamento estático e dinâmico.<br />

4.Processo de fabricação de transistores MOS com tecnologia CMOS.<br />

5. Introdução ao simulador microwind.<br />

6. Introdução ao simulador microwind.<br />

7. Projeto e simulação do inversor CMOS (comportamento estático e<br />

dinâmico) com o microwind.<br />

8. Projeto e simulação do inversor CMOS (comportamento estático e<br />

dinâmico) com o microwind<br />

9. Prova P1 (ou projeto).

PROGRAMA (cont.):<br />

10. Estudo do comportamento estático e dinâmico de Portas lógicas NE (NAND) e<br />

NOU (NOR)<br />

11. Projeto e simulação de porta lógica NE (NAND) e/ou NOU (NOR)<br />

(comportamento estático e dinâmico) com o microwind.<br />

12. Projeto e simulação de porta lógica NE (NAND) e/ou NOU (NOR)<br />

(comportamento estático e dinâmico) com o microwind.<br />

13. Estudo do comportamento dinâmico de outras funções lógicas e simplificação.<br />

14. Projeto e simulação de funções lógicas (comportamento estático e dinâmico)<br />

com o microwind.<br />

15. Projeto e simulação de funções lógicas (comportamento estático e dinâmico)<br />

com o microwind.<br />

16. Projeto e simulação de funções lógicas (comportamento estático e dinâmico)<br />

com o microwind.<br />

17. Prova P2 (ou projeto).<br />

18. Prova Substitutiva ou EXAME.

MÉDIA FINAL :<br />

M=(0,4P1 + 0,6P2) . K<br />

0 < K < 1,2 = fator dos relatórios =MR .0,12<br />

MR = média dos relatórios.<br />

Se M < 6,0 o aluno é reprovado com conceito C<br />

Se 6,0 < M < 7,0 o aluno é aprovado com conceito B<br />

Se 7,0 < M < 8,5 o aluno é aprovado com conceito A<br />

Se M > 8,5 o aluno é aprovado com conceito E<br />

Observação: Será realizada uma prova substitutiva para uma, e só uma, das<br />

provas P1 ou P2. No caso de reprovação, com a realização das 2 provas,<br />

a prova substitutiva vale como um exame onde a média final é a média<br />

aritmética entre M e o exame.

BIBLIOGRAFIA:<br />

Básica<br />

1. WESTE, N.; ESHRAGHIAN, K. Principles of CMOS V<strong>LSI</strong> Design. Ed.<br />

Addison Wesley, 1985<br />

2. PIERRE, T.F. Robert. Field Effect Devices: Modular series on<br />

Solid State Devices. 2. ed. Califórnia: Addison - Wesley Publishing<br />

Company, 1990. 4 v.<br />

3. MARTINO, João Antonio; PAVANELLO, Marcelo A. e VERDONCK,<br />

Patrick B. Caracterização Elétrica de Tecnologia e Dispositivos<br />

MOS. São Paulo: Ed. Pioneira Thomson Learning, 2003. 193 p.<br />

Complementar<br />

1. MARTINO, João Antonio. Um processo CMOS de Cavidade<br />

Dupla para Comprimento de Porta de 2µm São Paulo, 1988. 147 f.<br />

Tese (Doutorado em Engenharia Elétrica) - Escola Politécnica da<br />

Universidade de São Paulo, São Paulo, 1988.<br />

2. SEDRA, A. S.; SMITH, K. C. Microeletrônica. 4. ed. São Paulo:<br />

Makron Books, 1998. 1270 p.<br />

3. STREETMAN, B. G. Solid State Electronic Devices. 4. ed. New<br />

Jersey : Prentice-Hall, 1995, 462 p.<br />

4. TSIVIDIS, Y.P. Operation and Modeling of the MOS Transistor.<br />

Mc Graw Hill, 1987.

MOTIVAÇÃO<br />

•Explosão no uso da tecnologia da informação e<br />

na comunicação sem fio (wireless)<br />

•Telefones celulares, cameras digitais,<br />

microcomputadores pessoais, sistemas de<br />

entretenimentos…<br />

Tudo Graças aos Circuitos Integrados…

Evolução da Eletrônica<br />

Válvula Transistor Circuitos Integrados<br />

1896 1947 1959<br />

(Microeletrônica)

O que é um Circuito Integrado <br />

UNIVERSIDADE DE SÃO PAULO<br />

ESCOLA POLITÉCNICA<br />

DEPARTAMENTO DE ENGENHARIA ELETRÔNICA<br />

LABORATÓRIO DE SISTEMAS INTEGRÁVEIS

Primeiro Circuito Integrado – 1959 (Ano 0)<br />

•Jack St Clair Kilby<br />

(Universidade de Illinois, 1947)<br />

•Texas Instruments em 1958<br />

• U.S. Patent 3.138.743<br />

(Submetida em 1959) em<br />

“Miniaturized Electronic<br />

Circuits”<br />

•Projetou a primeira calculadora<br />

eletrônica portátil (4 operações)<br />

•Prêmio Nobel em 2000

Primeiro Circuito Integrado – 1959 (Ano 0)<br />

•Jack St Clair Kilby<br />

•Texas Instruments<br />

• U.S. Patent 3.138.743<br />

(Submetida em 1959) em<br />

“Miniaturized Electronic<br />

Circuits”<br />

Oscilador de Deslocamento de Fase<br />

•Prémio Nobel em 2000

Microeletrônica<br />

• Estuda Técnicas de projeto fabricação e testes de Circuitos<br />

Integrados<br />

– Possibilidades para construção de um circuito eletrônico:<br />

• Utilizando CI’s de prateleira<br />

(7400, 4000, 8086, Z80, 68000.....)<br />

• C. I. de aplicação específica<br />

(Muito utilizado atualmente pelas empresas de médio e<br />

grande porte em todo ou parte de determinados<br />

equipamentos eletrônicos de grande volume de produção)<br />

• Vantagens em se utilizar um C. I. de aplicação específica:<br />

– Menor área ocupada<br />

– Menor custo<br />

– Maior facilidade de manutenção<br />

– Proteção contra propriedade industrial (não pode ser<br />

copiado)

Tradicionalmente, o número de componentes em uma pastilha de<br />

Si tem dobrado a cada 2 anos (Lei de Moore)<br />

fonte Intel

Evolução do Custo Médio por Transistor<br />

em um Circuito Integrado<br />

Fonte : Intel

Menores dimensões<br />

Tecnológicas [m]<br />

Exemplos<br />

Fio de cabelo: 100 m<br />

Ameba: 15 m<br />

Glóbulo vermelho: 7 m<br />

Vírus da AIDS: 0,1 m<br />

Fonte : Intel

Um Exemplo da Revolução da Microeletrônica<br />

Intel 8008 (1972)<br />

200 KHz<br />

3.300 transistores<br />

13 mm 2<br />

30 anos<br />

X 12.000<br />

Intel Pentium 4 (2002)<br />

2,2 GHz<br />

42.000.000 transistores<br />

146 mm 2<br />

Dobra a cada 2 anos LEI DE MOORE

Evolução dos Parâmetros de Fabricação de Memórias DRAM<br />

1Mb 4Mb 16Mb 64Mb 256Mb 1Gb 4Gb<br />

Ano 1987 1990 1993 1996 1998 2001 2004<br />

L (m) 1,0 0,7 0,5 0,35 0,25 0,18 0,13<br />

Máscaras 11 14 18 21 21 23 23<br />

Porta x ox (nm) 20 15 12 10 7 5-4 5-4<br />

Etapas 200 300 400 500 550 600 600<br />

Junção x j (m) 0,25 0,2 0,15 0,1 0,07 0,05 0,03<br />

lâmina (mm) 125 150 150 200 200/300 300 300<br />

L<br />

N+ N+<br />

P<br />

x ox<br />

x j

Metodologias de Projetos de Circuitos<br />

Integrados Digitais de Aplicação Específica<br />

ASIC - Application Specific Integrated Circuit<br />

Circuitos Integrados de Aplicação Específica (Dedicados)<br />

Totalmente personalizados (Full Custom)<br />

Circuitos<br />

Dedicados<br />

Semi personalizados<br />

Células Padrão<br />

(Standard Cell)<br />

Matriz de Portas<br />

(Gate Array)

Projeto de C. I. Dedicados<br />

Totalmente Personalizados (FULL CUSTOM)<br />

Técnica “Top-Down”<br />

Hierarquicamente estruturado<br />

V DD<br />

Fabricação: Todos os passos (Completa)<br />

Vantagens: Comportamento estático e dinâmico<br />

muito bom<br />

Mínima área<br />

Desvantagens: Custo Elevado<br />

Tempo de projeto elevado

Projeto<br />

Lógico<br />

Semi Personalizados<br />

Ferramentas de C.A.D<br />

Biblioteca de<br />

Células<br />

Lay-out<br />

Metodologia de Projeto com Arranjo de Portas (Gate Array)<br />

CHIP<br />

C. I. já difundido, só falta a camada de interconexão<br />

Pode ter uma ou duas camadas de interconexão<br />

Cada célula contém transistores isolados (CMOS)<br />

Vantagens: Menor número de máscaras<br />

Baixo custo<br />

Realização rápida<br />

Desvantagens:<br />

Muitas interconexões<br />

Baixa utilização da superfície<br />

Otimização impossível

Metodologia Usando Células Padrão (Standard Cell)<br />

• Biblioteca de subsistemas digitais<br />

• Projeto baseado em equações lógicas<br />

CHIP<br />

Regist.<br />

Contador<br />

ULA<br />

Os blocos Registrador, Contador<br />

e ULA tem suas características<br />

bastante conhecidas, bastando<br />

apenas interliga-los e projetar o<br />

que não existe na biblioteca<br />

Vantagens: Projetista não necessita de<br />

muito conhecimento de C. I.<br />

Basta saber o projeto lógico<br />

Desvantagens:<br />

Área total não otimizada<br />

Potência e tempo de atraso não<br />

são bons

Comparação entre as metodologias de projeto de C. I. - V<strong>LSI</strong><br />

Complexidade<br />

Funcional<br />

Células<br />

Padrão<br />

STANDARD CELL<br />

Totalmente<br />

Personalizado<br />

FULL CUSTOM<br />

Arranjo de<br />

Portas<br />

GATE ARRAY<br />

Custo<br />

Relativo<br />

Regularidade<br />

Prateleira<br />

Arranjo de Portas<br />

Célula Padrão<br />

Tot. Personalizado<br />

Volume de Produção

Níveis de Projeto<br />

• Nível Funcional:<br />

– Divisão do circuito a ser projetado em “caixas pretas”, cada uma com uma<br />

função específica.<br />

Ex: Registrador, Somador, Contador....<br />

• Nível Lógico:<br />

– Detalhamento de cada uma das “caixas pretas” em blocos lógicos (portas<br />

lógicas).<br />

Ex: Portas NAND, NOR, Inversores....<br />

• Nível de Transistores:<br />

– Interligação dos componentes (transistores) para a implementação das<br />

portas lógicas, bem como definição das dimensões geométricas destes<br />

transistores.<br />

Ex: Transistores nMOS de W=10m e L=5m<br />

• Nível de Layout:<br />

– Layout final do circuito de acordo com as regras de projeto fornecidas e<br />

com as dimensões preestabelecidas pelo nível 3.<br />

Ex: Ver layout posteriormente

Dispositivos em Circuitos Integrados<br />

• Resistores<br />

Planta:<br />

Perfil:<br />

W<br />

L<br />

N<br />

P<br />

Al<br />

X<br />

SiO 2<br />

R<br />

<br />

L<br />

<br />

X W<br />

Normalmente a relação<br />

<br />

X<br />

(Resistência de Folha - R F )<br />

da tecnologia é fornecida.<br />

Exemplo:<br />

R 30<br />

L<br />

W<br />

90<br />

R F<br />

<br />

<br />

30 <br />

X<br />

L=3 W<br />

, projetar R=90 <br />

Adotando W=20 m<br />

L= 60 m<br />

Existe também o resistor P+ feito sobre substrato N (inverso)

Resistores (<strong>USP</strong>)<br />

Resistores projetado e fabricado na Escola Politécnica da <strong>USP</strong><br />

Dissertação de Mestrado – João Antonio Martino (1984)

• Capacitores<br />

Capacitância (C) Constante: adotada quando se deseja fabricar um<br />

capacitor em CI<br />

Al<br />

Condutor<br />

óxido<br />

P<br />

x ox<br />

óxido<br />

Si-poli/metal<br />

V<br />

C<br />

<br />

<br />

x<br />

ox<br />

ox<br />

A<br />

Onde: ox - Permissividade do dielétrico (normalmente SiO 2 )<br />

x ox - Espessura do dielétrico (normalmente SiO 2 )<br />

A - área do capacitor

Capacitância (C) Variável com a tensão aplicada<br />

Dois tipos<br />

Capacitância reversa de junção<br />

Capacitor MOS<br />

Capacitância Reversa de Junção<br />

V Depleção<br />

12<br />

N <br />

2<br />

Cj 3x10 pF/ m<br />

V 0,7 <br />

N<br />

P<br />

1/ 2<br />

N - Dopagem do Substrato<br />

V - Tensão Reversa

Capacitor MOS<br />

V<br />

Al<br />

SiO 2<br />

P<br />

x ox<br />

Metal<br />

Oxido<br />

Semicondutor<br />

Largamente utilizado para a obtenção de características elétricas e<br />

físicas do processo de fabricação de circuitos integrados.

Capacitores (<strong>USP</strong>)<br />

Capacitor projetado e fabricado na Escola Politécnica da <strong>USP</strong><br />

Dissertação de Mestrado – João Antonio Martino (1984)

• Diodos<br />

N<br />

P<br />

P<br />

N

• Transistor Bipolar<br />

C<br />

B<br />

E<br />

N<br />

B E C<br />

N+ P<br />

P<br />

• Transistor JFET<br />

D<br />

S<br />

G1<br />

D<br />

G2<br />

G<br />

N<br />

P<br />

S<br />

P

• Transistor MOS - Canal N (nMOS)<br />

Fonte<br />

(Source)<br />

Porta<br />

(Gate)<br />

N+ N+<br />

P<br />

Metal<br />

Dreno<br />

(Drain)<br />

Óxido<br />

G<br />

D<br />

B<br />

G<br />

D<br />

Substrato<br />

(Bulk)<br />

S<br />

S

• Transistor MOS - Canal P (pMOS)<br />

Porta<br />

Fonte<br />

Dreno<br />

P+ P+<br />

N<br />

G<br />

D<br />

B<br />

G<br />

D<br />

Substrato<br />

S<br />

S

Transistor – NMOSFET (<strong>USP</strong>)<br />

Porta<br />

(G)<br />

Alumínio<br />

Fonte<br />

(S)<br />

Dreno<br />

(D)<br />

Transistor projetado e fabricado na Escola Politécnica da <strong>USP</strong><br />

Dissertação de Mestrado – João Antonio Martino (1984)

Desenhe o perfil do Circuito Integrado abaixo

Tecnologia de Fabricação de Circuitos<br />

Integrados<br />

- TTL LS DECLÍNIO<br />

SCHOTTKY<br />

• BIPOLAR - ECL MAIS VELOZ<br />

- I 2 L <strong>LSI</strong> , V<strong>LSI</strong><br />

- PMOS: 1 a TECNOLOGIA MOS, MEMÓRIAS,<br />

CALCULADORAS<br />

• MOS<br />

- NMOS: <strong>LSI</strong><br />

- CMOS: SSI, MSI, V<strong>LSI</strong>

Densidade de Integração:<br />

Número de transistores:<br />

SSI = pequena escala: N 100<br />

MSI = média escala: 100 N 1.000<br />

<strong>LSI</strong> = grande escala: 1.000 N 100.000<br />

V<strong>LSI</strong> = muito grande: 100.000 N 1.000.000<br />

U<strong>LSI</strong> = altíssima: N 1.000.000

Tecnologia CMOS<br />

• Composta pela associação de transistores<br />

• Alta imunidade à ruído<br />

nMOS<br />

pMOS<br />

• Baixa potência dissipada<br />

•Mais importante tecnologia da atualidade, pois permite o projeto de<br />

Circuitos Integrados Digitais em escala muito ampla<br />

V<strong>LSI</strong>

TRANSISTORES MOS<br />

• MOS canal N<br />

TIPO ENRIQUECIMENTO*<br />

TIPO DEPLEÇÃO<br />

• MOS canal P<br />

TIPO ENRIQUECIMENTO*<br />

TIPO DEPLEÇÃO

1. TRANSISTOR MOS CANAL N ( nMOS ) TIPO<br />

ENRIQUECIMENTO<br />

Fonte<br />

(Source)<br />

Porta<br />

(Gate)<br />

Dreno<br />

(Drain)<br />

N+ N+<br />

P<br />

PORTA<br />

Substrato<br />

(Bulk)<br />

FONTE<br />

SUBSTRATO<br />

DRENO

• Normalmente o substrato é aterrado<br />

• Funcionamento como uma chave:<br />

- Para G= 5V ( “1” )<br />

( CHAVE FECHADA )<br />

- Para G= 0V ( “0” )<br />

( CHAVE ABERTA )<br />

S<br />

S<br />

G=1<br />

G=0<br />

D<br />

D<br />

•Característica:<br />

-Transmite bem o “0” :<br />

-NÃO transmite bem o “1” :<br />

0V<br />

5V<br />

I<br />

0V<br />

4V<br />

I

2. TRANSISTOR MOS CANAL P ( pMOS ) TIPO<br />

ENRIQUECIMENTO<br />

Fonte<br />

(Source)<br />

Porta<br />

(Gate)<br />

Dreno<br />

(Drain)<br />

PORTA<br />

P+ P+<br />

N<br />

FONTE<br />

DRENO<br />

Substrato<br />

(Bulk)<br />

SUBSTRATO

• Normalmente o substrato é ligado a “V DD ”<br />

• Funcionamento como uma chave:<br />

- Para G= 5V ( “1” )<br />

( CHAVE ABERTA )<br />

- Para G= 0V ( “0” )<br />

( CHAVE FECHADA )<br />

S<br />

S<br />

G=1<br />

G=0<br />

D<br />

D<br />

•Característica:<br />

-Transmite bem o “1” :<br />

-NÃO transmite bem o “0” :<br />

5V<br />

0V<br />

I<br />

5V<br />

1V<br />

I

G<br />

CHAVE CMOS<br />

S<br />

D<br />

5V<br />

I<br />

0V<br />

5V<br />

G<br />

I<br />

INVERSOR CMOS<br />

V DD<br />

V DD<br />

V DD<br />

E<br />

S<br />

S=1<br />

S=0 E S<br />

E=0 E=1

PORTAS LÓGICAS BÁSICAS<br />

V DD<br />

V DD<br />

B<br />

B<br />

S<br />

A<br />

S<br />

A<br />

A B S<br />

0<br />

0<br />

0<br />

1<br />

1<br />

1<br />

0<br />

1<br />

A B S<br />

0<br />

0<br />

0<br />

1<br />

1<br />

1<br />

0<br />

1

PORTA LÓGICA “AND”<br />

<br />

PORTA LÓGICA “OR”

Exercícios:<br />

Preencha o Mapa de Karnaugh das funções abaixo:<br />

V DD<br />

V DD<br />

A<br />

B<br />

C<br />

A<br />

B<br />

C<br />

D<br />

G<br />

A<br />

F<br />

A<br />

B<br />

D<br />

B<br />

C<br />

C<br />

AB<br />

C<br />

0<br />

00 01 11 10<br />

AB<br />

CD<br />

00<br />

01<br />

00 01 11 10<br />

1<br />

11<br />

10<br />

F=____________________<br />

G=____________________

Transistor MOS - Comportamento Elétrico<br />

• Transistor nMOS<br />

Porta<br />

Fonte<br />

Dreno<br />

N+ N+<br />

I DS<br />

V DS =cte<br />

G<br />

P<br />

Substrato<br />

I DS<br />

D<br />

I DS<br />

V Tn 1 V<br />

(Tensão de Limiar)<br />

Região<br />

Triodo<br />

Região de<br />

Saturação<br />

V GS<br />

V GS2<br />

V GS1<br />

V GS2 >V GS1<br />

V DS<br />

V GS<br />

S<br />

V DS

Transistor NMOSFET<br />

(Metal-Oxide-Semiconductor Field Effect<br />

Transistor, canal N, tipo Enriquecimento)<br />

V DS<br />

I DS<br />

D<br />

Metal<br />

(condutor)<br />

V GS<br />

W<br />

I DS<br />

Óxido de porta<br />

(isolante)<br />

G<br />

Porta<br />

x ox<br />

V DS<br />

V GS<br />

S<br />

N+<br />

Fonte<br />

L<br />

P<br />

N+<br />

Dreno<br />

Substrato<br />

(ou Corpo)

Transistor - NMOSFET<br />

Porta<br />

(G)<br />

Alumínio<br />

Fonte<br />

(S)<br />

Dreno<br />

(D)<br />

Transistor projetado e fabricado na Escola Politécnica da <strong>USP</strong><br />

Dissertação de Mestrado – João Antonio Martino (1984)

Equações de I DS =f(V GS , V DS ) de 1 a Ordem<br />

• Região de Corte:<br />

I DS =0<br />

• Região Triodo:<br />

I<br />

<br />

DS n<br />

V GS V Tn ou V GS -V Tn 0<br />

0< V DS V GS -V Tn<br />

<br />

V <br />

V<br />

V V<br />

<br />

DS<br />

GS Tn DS <br />

<br />

2 <br />

• Região de Saturação:<br />

I<br />

DS<br />

<br />

<br />

2<br />

2<br />

0< V GS -V Tn V DS<br />

V V<br />

<br />

GS Tn<br />

nox<br />

W <br />

n<br />

onde n<br />

<br />

2<br />

x ox L <br />

Fator de Ganho

Fator de ganho<br />

nox<br />

W <br />

n<br />

<br />

x ox L <br />

Dependentes<br />

do Processo<br />

<br />

<br />

x<br />

n<br />

ox<br />

ox<br />

Mobilidade dos elétrons<br />

Permissividade do óxido<br />

Espessura do óxido de porta<br />

Dependentes<br />

da Geometria<br />

(lay-out)<br />

W<br />

L<br />

Largura de canal<br />

Comprimento de canal

• Transistor pMOS<br />

Porta<br />

Fonte<br />

Dreno<br />

P+ P+<br />

-I DS<br />

-V DS =cte<br />

N<br />

V Tp -1 V<br />

-V GS<br />

G<br />

Substrato<br />

I DS<br />

D<br />

V DS<br />

-I DS<br />

(Tensão de Limiar)<br />

Região<br />

Triodo<br />

Região de<br />

Saturação<br />

-V GS2<br />

-V GS1<br />

V GS<br />

S<br />

-V DS

• Região de Corte: V GS V Tp ou V GS -V Tp 0<br />

I DS =0<br />

• Região Triodo: V GS -V Tp V DS < 0<br />

I<br />

<br />

DS p<br />

<br />

<br />

<br />

V <br />

V V V <br />

DS<br />

GS Tp DS <br />

<br />

2 <br />

• Região de Saturação: V DS V GS -V Tp < 0<br />

2<br />

I<br />

DS<br />

<br />

<br />

<br />

p<br />

<br />

V<br />

GS<br />

<br />

2<br />

V<br />

Tp<br />

<br />

2

p<br />

<br />

<br />

<br />

p ox<br />

x ox<br />

<br />

<br />

<br />

W<br />

L<br />

Fator de ganho<br />

<br />

<br />

<br />

p<br />

<br />

p<br />

<br />

2<br />

Mobilidade<br />

Tensão de Limiar do Transistor canal P<br />

V Tp -1 V<br />

Geometrias<br />

Normalmente<br />

n<br />

das lacunas<br />

Normalmente simétrico com relação a V Tn<br />

|V Tp | = V Tn<br />

Wp<br />

<br />

L<br />

p<br />

W<br />

L<br />

e assim podemos ter p = n<br />

n<br />

n<br />

para compensar o fato de p < n

Inversor CMOS - Comportamento Elétrico<br />

V E<br />

G<br />

G<br />

V DD<br />

S<br />

D<br />

D<br />

S<br />

I SD =-I DS<br />

I DS<br />

V S<br />

Transistor canal p<br />

•V GS =V E -V DD<br />

•V DS =V S -V DD<br />

•I DS =-I SD<br />

Transistor canal n<br />

•V GS =V E<br />

•V DS =V S<br />

I DSn =-I DSp

V S<br />

Inversor CMOS<br />

Metal<br />

Si-poli<br />

V DD<br />

Saída<br />

SiO 2<br />

Terra<br />

N+ P+ P+ N+ N+ P+<br />

Si N<br />

Si P<br />

G<br />

V E<br />

V DD<br />

S<br />

D D<br />

S

Inversor CMOS (<strong>USP</strong>)<br />

Inversor CMOS projetado e fabricado na Escola Politécnica da <strong>USP</strong><br />

Tese de Doutorado – João Antonio Martino (1988)

Curva Característica de Transferência<br />

I DSn =-I DSp<br />

V S<br />

V DD<br />

0,7V DD<br />

A<br />

B<br />

V DD /2<br />

C<br />

0,3V DD<br />

V Tn<br />

D<br />

E<br />

V INV V DD -|V Tp | V DD<br />

V<br />

E

V S<br />

V DD<br />

A<br />

1 2<br />

B<br />

3<br />

Regiões Operacionais<br />

A -<br />

B -<br />

nMOS corte<br />

pMOS triodo<br />

nMOS saturação<br />

pMOS triodo<br />

0,7V DD<br />

V DD /2<br />

0,3V DD<br />

4<br />

5<br />

C<br />

D<br />

E<br />

6<br />

7 8<br />

C -<br />

D -<br />

E -<br />

nMOS saturação<br />

pMOS saturação<br />

nMOS triodo<br />

pMOS saturação<br />

nMOS triodo<br />

pMOS corte<br />

V Tn<br />

V INV V DD -|V Tp | V DD<br />

V<br />

E

Influência da Relação n / p na Curva Característica<br />

de Transferência<br />

V S<br />

V DD<br />

V<br />

INV<br />

V<br />

DD<br />

1 1/16<br />

16<br />

<br />

V<br />

Tp<br />

<br />

1<br />

n / p<br />

n<br />

<br />

p<br />

<br />

V<br />

n<br />

<br />

<br />

p<br />

Tn<br />

<br />

<br />

n<br />

p<br />

<br />

x<br />

<br />

x<br />

n<br />

<br />

ox<br />

ox<br />

ox<br />

ox<br />

p<br />

W<br />

L<br />

W<br />

L<br />

n<br />

n<br />

p<br />

p<br />

<br />

<br />

<br />

n<br />

p<br />

W<br />

L<br />

W<br />

L<br />

n<br />

n<br />

p<br />

p<br />

1,6<br />

V DD /2<br />

2,5<br />

3,4<br />

V DD<br />

V E

Margens de Ruído<br />

V S<br />

V DD<br />

MR L<br />

dV<br />

dV<br />

S<br />

E<br />

<br />

1<br />

MR H<br />

V IL<br />

V INV<br />

V IH<br />

V DD<br />

V<br />

E

MR<br />

H<br />

<br />

V<br />

Margem de ruído em nível alto:<br />

V V V V V<br />

OH<br />

IH<br />

DD<br />

IH<br />

DD<br />

INV<br />

<br />

0,1 V<br />

DD<br />

<br />

MR<br />

H<br />

<br />

0,9V<br />

DD<br />

<br />

V<br />

INV<br />

Margem de ruído em nível baixo:<br />

MR<br />

L<br />

<br />

V<br />

IL<br />

<br />

V<br />

OL<br />

<br />

V<br />

IL<br />

<br />

0<br />

<br />

V<br />

INV<br />

<br />

0,1 V<br />

DD<br />

MR<br />

L<br />

<br />

V<br />

INV<br />

<br />

0,1 V<br />

DD<br />

A aproximação acima é válida para 2VV INV 3V (maioria das<br />

aplicações) e garante erro inferior a 10% nesta faixa

Comportamento Dinâmico<br />

1. Resistências<br />

L<br />

R <br />

X.W<br />

<br />

onde : <br />

X<br />

R<br />

FOLHA<br />

<br />

R<br />

<br />

R<br />

FOLHA<br />

.<br />

L<br />

W<br />

X<br />

L<br />

W<br />

Material R FOLHA [ ]<br />

Alumínio 0,05<br />

Silicetos 2<br />

N+ 20<br />

P+ 50<br />

Polisilício 30<br />

Exemplo: POLISILÍCIO<br />

W= 5m<br />

L= 100m<br />

L=100m e W=5 m<br />

R<br />

POLI<br />

100<br />

30. 600<br />

5

2.Capacitâncias<br />

G<br />

C GD<br />

D<br />

Capacitância total<br />

associada à porta<br />

C DB<br />

B<br />

• CAPACITÂNCIA MOS<br />

C<br />

C<br />

G<br />

G<br />

<br />

<br />

C<br />

C<br />

GS<br />

<br />

óxido<br />

C<br />

<br />

GD<br />

<br />

x<br />

ox<br />

ox<br />

<br />

C<br />

.A<br />

• CAPACITÂNCIA DE JUNÇÃO (C J )<br />

GB<br />

C GS<br />

C GB<br />

S<br />

onde:<br />

C DB …… C J Dreno<br />

C SB …… C J Fonte<br />

C SB<br />

Perfil:<br />

Planta:<br />

N<br />

N<br />

P<br />

N<br />

N<br />

a<br />

C JP (periférico)<br />

C JA (área)<br />

C J = C JA .( área ) + C JP .( perímetro )<br />

C J = C JA .( a.b ) + C JP .( 2a + 2b )<br />

b

Tempos de Atraso, Subida e Descida de um<br />

Inversor CMOS<br />

V DD<br />

V E<br />

V DD<br />

t<br />

V S<br />

V E<br />

C L<br />

V S<br />

V DD<br />

90%<br />

50%<br />

t f<br />

t r<br />

10%<br />

t<br />

tp HL<br />

tp LH

• tp LH ..tempo entre o sinal na entrada atingir 50% (descendente) e o<br />

sinal na saída também 50% no sentido ascendente.<br />

•tp HL ..tempo entre o sinal na entrada atingir 50% (ascendente) e o sinal<br />

na saída também 50% no sentido descendente.<br />

• t d … média dos tempos de propagação do sinal lógico;<br />

• t r …. tempo do sinal na saída subir de 10% a 90% do seu total.<br />

• t f ….tempo do sinal na saída descer de 90% a 10% do total.<br />

t<br />

d<br />

<br />

tp<br />

LH<br />

<br />

2<br />

tp<br />

HL<br />

t<br />

tp r t<br />

LH tp<br />

2<br />

f<br />

HL<br />

2<br />

t<br />

d<br />

<br />

t<br />

r<br />

<br />

4<br />

t<br />

f<br />

t<br />

r<br />

4.<br />

β<br />

P<br />

CL<br />

.V<br />

DD<br />

t<br />

f<br />

4.<br />

β<br />

N<br />

CL<br />

.V<br />

DD

Exercício 1<br />

Projete um circuito inversor que tenha margem de ruído em nível<br />

alto de 2,5V e tempo de atraso de 1ns.<br />

Dados:<br />

V DD = 5V ;V TN = 1V ; V TP = -1V ; N = 400 [ cm 2 /V.s] ;<br />

P = 200 [ cm 2 /V.s] ; x ox = 40nm ; ox = 40x10 -14 [F/cm] ; L N = L P ;<br />

Dimensão mínima= 1 m ; C L =4pF

Exercício 2<br />

Projete um circuito inversor que tenha margem de ruído em nível<br />

alto de 2,5V e tempo de subida de 4ns.<br />

Dados:<br />

V DD = 5V ;V TN = 1V ; V TP = -1V ; N = 400 [ cm 2 /V.s] ;<br />

P = 200 [ cm 2 /V.s] ; x ox = 40nm ; ox = 40x10 -14 [F/cm] ; L N = L P ;<br />

Dimensão mínima= 1 m ; C L =1pF

Inversor Lógico Digital CMOS<br />

280 m<br />

V out<br />

V DD<br />

PMOSFET<br />

V DD<br />

GND<br />

V in<br />

V out<br />

V in<br />

NMOSFET<br />

420 m<br />

V in<br />

Si-Poli<br />

V DD<br />

V out<br />

GND<br />

Metal<br />

N+ P+ P+ N+ N+ P+<br />

SiO 2<br />

(Isolante)<br />

Si - N<br />

Si - P

Processo de Fabricação de Circuitos Integrados<br />

Principais Etapas de Processo:<br />

Oxidação Térmica<br />

Deposição de óxido de silício<br />

Fotogravação<br />

Corrosão Química<br />

Difusão de Impurezas<br />

Implantação Iônica

Sala Limpa (“Cleanroom”)

Oxidação Térmica:<br />

Objetivo: Obtenção de óxido de silício (SiO 2 ) sobre o silício<br />

Oxidação Térmica<br />

SiO 2<br />

Si p<br />

• Tempo<br />

• Temperatura<br />

Si p<br />

Lâmina<br />

• Ambiente<br />

Si<br />

<br />

o<br />

<br />

T900<br />

C<br />

O SiO<br />

2<br />

2<br />

Funções Principais<br />

• Mascaramento contra impurezas<br />

• Dielétrico de porta

Deposição de Óxido de Silício: (C.V.D.)<br />

Objetivo: Obtenção de óxido de silício (SiO 2 ) sobre o silício<br />

ou outra superfície qualquer<br />

Deposição de SiO 2<br />

SiO 2<br />

Si p<br />

Lâmina<br />

• Tempo<br />

• Temperatura<br />

• Fluxo de Gases<br />

Si p<br />

SiH<br />

500<br />

o<br />

C<br />

O <br />

SiO<br />

2H<br />

4 2<br />

2 2<br />

<br />

Função Principal<br />

• Mascaramento contra impurezas

Abertura de Janelas : Fotogravação e Corrosão Química<br />

Objetivo: processo pelo qual retiramos o óxido de silício,<br />

silício policristalino ou alumínio de certas regiões,<br />

determinadas pela fotomáscara<br />

Si p<br />

Abertura de<br />

Janelas<br />

• fotomáscara<br />

Si p<br />

Funções Principais<br />

• No SiO 2 : posterior difusão localizada;<br />

• No alumínio ou silício policristalino: definição das vias de<br />

interconexão.

1 - Obtenção da Fotomáscara<br />

Sucessivas reduções<br />

Campo claro<br />

Campo escuro

2 - Aplicação de Fotorresiste na<br />

lâmina<br />

3 - Exposição à luz ultravioleta<br />

4 - Revelação<br />

5 - Corrosão química<br />

6 - Remoção do Fotorresiste<br />

Si p<br />

SiO 2<br />

Luz Ultravioleta<br />

Fotomáscara<br />

Fotorresiste<br />

SiO 2<br />

Si p<br />

Si p<br />

Si p

Difusão de Impurezas:<br />

SiO 2<br />

Objetivo: introduzir na rede cristalina do Si impurezas<br />

doadoras (fósforo, arsênio…) ou aceitadoras (boro…)<br />

Si p<br />

Concentração<br />

• Tempo<br />

Difusão<br />

• Temperatura<br />

• Tipo de dopante<br />

Si n<br />

Si p<br />

Superfície da lâmina<br />

profundidade<br />

Função Principal<br />

• criação de uma região com características doadora ou aceitadora

Implantação Iônica:<br />

SiO 2<br />

Objetivo: introduzir na rede cristalina do Si impurezas<br />

doadoras ou aceitadoras por impacto<br />

Si p<br />

Concentração<br />

Superfície da lâmina<br />

Implantação Iônica<br />

• Dose<br />

• Energia<br />

• Tipo de dopante<br />

Função Principal<br />

profundidade<br />

• criação de uma região com características doadora ou aceitadora<br />

Si n<br />

Si p<br />

Perfil de dopantes após o<br />

recozimento térmico

Processo de Fabricação de Circuitos Integrados CMOS<br />

Tecnologia CMOS cavidade N de 1,2 m (Foundry ES2)<br />

1 - Oxidação térmica<br />

Lâmina de silício tipo p <br />

2 - Fotogravação e corrosão do SiO 2<br />

Máscara (NWELL) - Definição das regiões que serão cavidades tipo N<br />

3 - Implantação Iônica de Fósforo<br />

1 a máscara<br />

I/I de Fósforo<br />

SiO 2<br />

Si n<br />

Si p

4 - Remoção total do SiO 2<br />

5 - Deposição de SiO 2<br />

6 - Fotogravação e Corrosão do SiO 2<br />

7 - Oxidação térmica de porta<br />

Máscara DN<br />

Máscaras (N+Diffusion e P+Diffusion)- Definição das regiões de difusão tipo N e P<br />

Máscara<br />

NW<br />

Máscara DP<br />

SiO 2<br />

Si n<br />

Si p

8 - Deposição de silício policristalino dopado<br />

9 - Fotogravação e Corrosão do Silício policristalino<br />

Máscara (Polysilicon)- Definição do silício policristalino<br />

Máscara PO<br />

Máscara<br />

NW<br />

Máscara DN<br />

Máscara DP<br />

Si-poli<br />

SiO 2<br />

Si n<br />

Si p

10 - Fotogravação do Fotorresiste<br />

Máscara (P+Diffusion)- Definição das regiões P+<br />

11 - Implantação Iônica de Boro<br />

Transistor pMOS e<br />

contato com substrato<br />

Máscara PO<br />

Máscara<br />

NW<br />

Máscara DN<br />

Máscara DP<br />

Fotorresiste<br />

SiO 2<br />

P+<br />

P+<br />

P+<br />

Si n<br />

Si p<br />

12 - Remoção do Fotorresiste

13 - Fotogravação do Fotorresiste<br />

Máscara (N+Diffusion)- Definição das regiões N+<br />

14 - Implantação Iônica de Fósforo<br />

Transistor nMOS e<br />

contato com cavidade<br />

Máscara PO<br />

Máscara<br />

NW<br />

Máscara DN<br />

Fotorresiste<br />

Máscara DP<br />

SiO 2<br />

N+ P+ P+ N+ N+ P+<br />

Si n<br />

15 - Remoção do Fotorresiste<br />

Si p

17 - Fotogravação e Corrosão do SiO 2<br />

Máscara (Contact) - Definição de contatos<br />

Máscara CO<br />

Máscara PO<br />

Máscara<br />

NW<br />

Máscara DN<br />

Máscara DP<br />

SiO 2<br />

16 - Deposição de SiO 2<br />

Si n<br />

Si p<br />

N+ P+ P+ N+ N+ P+<br />

18 - Deposição de Metal - Alumínio

19 - Fotogravação e Corrosão do Alumínio<br />

Máscara (Metal ) - Definição do Alumínio<br />

Máscara ME<br />

Máscara PO<br />

Máscara<br />

NW<br />

Máscara DN<br />

Alumínio<br />

Máscara DP<br />

SiO 2<br />

N+ P+ P+ N+ N+ P+<br />

Si n<br />

Si p