ampirik kip ayrışımı için kübik esnek şerit aradeğerleme yönteminin ...

ampirik kip ayrışımı için kübik esnek şerit aradeğerleme yönteminin ...

ampirik kip ayrışımı için kübik esnek şerit aradeğerleme yönteminin ...

Create successful ePaper yourself

Turn your PDF publications into a flip-book with our unique Google optimized e-Paper software.

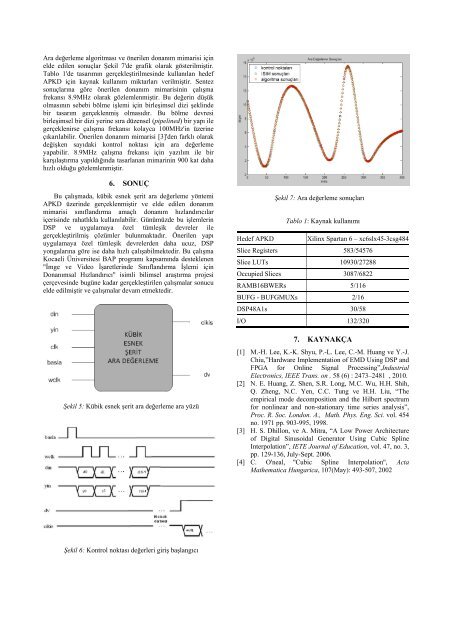

Ara değerleme algoritması ve önerilen donanım mimarisi <strong>için</strong><br />

elde edilen sonuçlar Şekil 7'de grafik olarak gösterilmiştir.<br />

Tablo 1'de tasarımın gerçekleştirilmesinde kullanılan hedef<br />

APKD <strong>için</strong> kaynak kullanım miktarları verilmiştir. Sentez<br />

sonuçlarına göre önerilen donanım mimarisinin çalışma<br />

frekansı 8.9MHz olarak gözlemlenmiştir. Bu değerin düşük<br />

olmasının sebebi bölme işlemi <strong>için</strong> birleşimsel dizi şeklinde<br />

bir tasarım gerçeklenmiş olmasıdır. Bu bölme devresi<br />

birleşimsel bir dizi yerine sıra düzensel (pipelined) bir yapı ile<br />

gerçeklenirse çalışma frekansı kolayca 100MHz'in üzerine<br />

çıkarılabilir. Önerilen donanım mimarisi [3]'den farklı olarak<br />

değişken sayıdaki kontrol noktası <strong>için</strong> ara değerleme<br />

yapabilir. 8.9MHz çalışma frekansı <strong>için</strong> yazılım ile bir<br />

karşılaştırma yapıldığında tasarlanan mimarinin 900 kat daha<br />

hızlı olduğu gözlemlenmiştir.<br />

6. SONUÇ<br />

Bu çalışmada, <strong>kübik</strong> <strong>esnek</strong> <strong>şerit</strong> ara değerleme yöntemi<br />

APKD üzerinde gerçeklenmiştir ve elde edilen donanım<br />

mimarisi sınıflandırma amaçlı donanım hızlandırıcılar<br />

içerisinde rahatlıkla kullanılabilir. Günümüzde bu işlemlerin<br />

DSP ve uygulamaya özel tümleşik devreler ile<br />

gerçekleştirilmiş çözümler bulunmaktadır. Önerilen yapı<br />

uygulamaya özel tümleşik devrelerden daha ucuz, DSP<br />

yongalarına göre ise daha hızlı çalışabilmektedir. Bu çalışma<br />

Kocaeli Üniversitesi BAP programı kapsamında desteklenen<br />

"İmge ve Video İşaretlerinde Sınıflandırma İşlemi <strong>için</strong><br />

Donanımsal Hızlandırıcı" isimli bilimsel araştırma projesi<br />

çerçevesinde bugüne kadar gerçekleştirilen çalışmalar sonucu<br />

elde edilmiştir ve çalışmalar devam etmektedir.<br />

Şekil 5: Kübik <strong>esnek</strong> <strong>şerit</strong> ara değerleme ara yüzü<br />

Şekil 6: Kontrol noktası değerleri giriş başlangıcı<br />

Şekil 7: Ara değerleme sonuçları<br />

Tablo 1: Kaynak kullanımı<br />

Hedef APKD Xilinx Spartan 6 – xc6slx45-3csg484<br />

Slice Registers 583/54576<br />

Slice LUTs 10930/27288<br />

Occupied Slices 3087/6822<br />

RAMB16BWERs 5/116<br />

BUFG - BUFGMUXs 2/16<br />

DSP48A1s 30/58<br />

I/O 132/320<br />

7. KAYNAKÇA<br />

[1] M.-H. Lee, K.-K. Shyu, P.-L. Lee, C.-M. Huang ve Y.-J.<br />

Chiu,”Hardware Implementation of EMD Using DSP and<br />

FPGA for Online Signal Processing”,Industrial<br />

Electronics, IEEE Trans. on , 58 (6) : 2473–2481 , 2010.<br />

[2] N. E. Huang, Z. Shen, S.R. Long, M.C. Wu, H.H. Shih,<br />

Q. Zheng, N.C. Yen, C.C. Tung ve H.H. Liu, “The<br />

empirical mode decomposition and the Hilbert spectrum<br />

for nonlinear and non-stationary time series analysis”,<br />

Proc. R. Soc. London. A., Math. Phys. Eng. Sci. vol. 454<br />

no. 1971 pp. 903-995, 1998.<br />

[3] H. S. Dhillon, ve A. Mitra, “A Low Power Architecture<br />

of Digital Sinusoidal Generator Using Cubic Spline<br />

Interpolation”, IETE Journal of Education, vol. 47, no. 3,<br />

pp. 129-136, July-Sept. 2006.<br />

[4] C. O'neal, ''Cubic Spline Interpolation'', Acta<br />

Mathematica Hungarica, 107(May): 493-507, 2002

![Page 1 %XODQÕN 6 ]JHo LOH *|U QW 6WDELOL]DV\RQX M ...](https://img.yumpu.com/18085529/1/184x260/page-1-xodqon-6-jho-loh-u-qw-6wdeloldvrqx-m-.jpg?quality=85)

![[ ]T [ ]T - KULIS - Kocaeli Üniversitesi](https://img.yumpu.com/18085463/1/184x260/-t-t-kulis-kocaeli-universitesi.jpg?quality=85)