Skript

Skript

Skript

Erfolgreiche ePaper selbst erstellen

Machen Sie aus Ihren PDF Publikationen ein blätterbares Flipbook mit unserer einzigartigen Google optimierten e-Paper Software.

Kapitel 5 Analoge Schaltungstechnik Integrierte Schaltungen II<br />

5 Integrierte Schaltungstechnik<br />

Elektronische und insbesondere integrierte Schaltungen dienen der Verarbeitung elektrischer<br />

Signale.<br />

Grobe Klassifizierung:<br />

Analoge Signale - Analoge Schaltungstechnik<br />

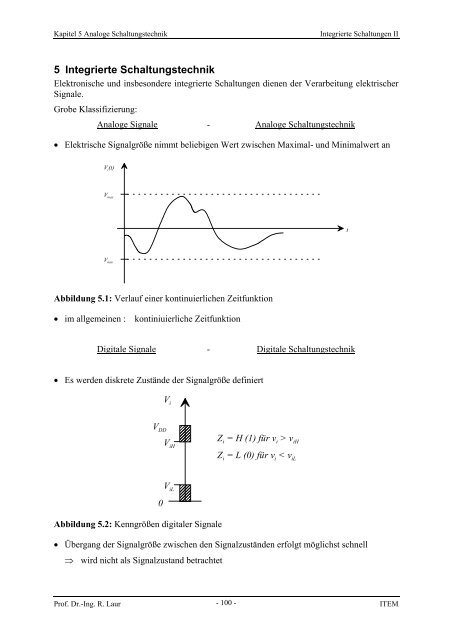

• Elektrische Signalgröße nimmt beliebigen Wert zwischen Maximal- und Minimalwert an<br />

V i(t)<br />

V max<br />

V min<br />

Abbildung 5.1: Verlauf einer kontinuierlichen Zeitfunktion<br />

• im allgemeinen : kontiniuierliche Zeitfunktion<br />

Digitale Signale - Digitale Schaltungstechnik<br />

• Es werden diskrete Zustände der Signalgröße definiert<br />

V i<br />

VDD ViH V iL<br />

<br />

<br />

<br />

<br />

Abbildung 5.2: Kenngrößen digitaler Signale<br />

0<br />

Z i = H (1) für v i > v iH<br />

Z i = L (0) für v i < v iL<br />

• Übergang der Signalgröße zwischen den Signalzuständen erfolgt möglichst schnell<br />

⇒ wird nicht als Signalzustand betrachtet<br />

Prof. Dr.-Ing. R. Laur - 100 -<br />

ITEM<br />

t

Kapitel 5 Analoge Schaltungstechnik Integrierte Schaltungen II<br />

V i(t)<br />

V iH<br />

V iL<br />

Z i(t)<br />

1<br />

0<br />

Abbildung 5.3: Übergang analoger auf digitale Signale<br />

• Analoge Signale werden mit A/D-Umsetzern in digitale Signale gewandelt<br />

Abbildung 5.4: A/D-Umsetzer<br />

V e<br />

• Digitale Signale werden mit D/A-Umsetzern in analoge Signale gewandelt<br />

Abbildung 5.5: D/A-Umsetzer<br />

X e<br />

A<br />

D<br />

• Zunehmende Bedeutung gemischter Schaltungen insbesondere im Bereich der Mikrosystemtechnik<br />

⇒ analoge Signalverarbeitung<br />

⇒ digitale Signalverarbeitung<br />

Prof. Dr.-Ing. R. Laur - 101 -<br />

ITEM<br />

D<br />

A<br />

X a<br />

V a<br />

t<br />

t

Kapitel 5 Analoge Schaltungstechnik Integrierte Schaltungen II<br />

5.1 Transistor - Grundschaltungen<br />

Anschlüsse: Emitter (E), Basis (B), Collector (C)<br />

6 grundsätzliche Zuordnungen der Anschlüsse zu den Signalklemmen => lediglich drei mit<br />

technischem Nutzen.<br />

v I<br />

i B<br />

i E<br />

i C<br />

Emitter-Grundschaltung<br />

v O<br />

v I<br />

i B iE<br />

i E<br />

v I v O<br />

i C<br />

Kollektor-Grundschaltung<br />

Abbildung 5.6: Grundschaltungen des Bipolar-Transistors<br />

i B<br />

i C<br />

Basis-Grundschaltung<br />

Da beim MOS-Transistor der Substrat- oder Bulkanschluß in der Regel nicht als Signalklemme<br />

genutzt wird, ergeben sich entsprechend:<br />

• Source-Grundschaltung<br />

• Gate-Grundschaltung<br />

• Drain-Grundschaltung<br />

5.2 Gleichstrom - Arbeitspunkt<br />

Der Transistor wird in einem definierten Arbeitspunkt betrieben. Kenngrößen in Emitterschaltung:<br />

VBE, VCE (eingeprägte Größen)<br />

IB, IC<br />

Diesen Gleichströmen bzw. -spannungen werden die zeitabhängigen Signalströme bzw. -<br />

spannungen überlagert:<br />

vBE(t), vCE(t),<br />

iB(t), iC(t).<br />

In integrierten Schaltungen steht zumeist nur eine Versorgungsquelle zur Verfügung. Diese<br />

muß zur Einstellung des Arbeitspunktes verwendet werden.<br />

Prof. Dr.-Ing. R. Laur - 102 -<br />

ITEM<br />

v O

Kapitel 5 Analoge Schaltungstechnik Integrierte Schaltungen II<br />

Einstellung des Basisstroms über Basiswiderstand<br />

R B<br />

VBE<br />

I B<br />

I C<br />

R C<br />

I E<br />

V CE<br />

V O<br />

V CC<br />

Abbildung 5.7: Einstellung des Gleichstromarbeitspunktes durch Basiswiderstand<br />

Vorwärts-Aktiver Bereich:<br />

R<br />

B<br />

IC ≈ β F ⋅IB R<br />

C<br />

VCC −VBEVCC−0.7V = ≈ (5.1)<br />

I I<br />

B B<br />

V −V V −V<br />

= ≈<br />

I β ⋅ IB<br />

CC CE CC CE<br />

C F<br />

Arbeitspunkteinstellung durch Basis-Spannungsteiler<br />

R 1<br />

V B<br />

R 2<br />

I Q<br />

I B<br />

Abbildung 5.8: Einstellung des Gleichstromarbeitspunktes mit Basis-Spannungsteiler<br />

V BE<br />

V CC<br />

IC = β ⋅IB ( β 1)<br />

R C<br />

I C<br />

I E<br />

R E<br />

V O<br />

V CE<br />

I = I + I = + ⋅I ≈ I<br />

E C B F B<br />

Prof. Dr.-Ing. R. Laur - 103 -<br />

ITEM<br />

C<br />

(5.2)<br />

(5.3)<br />

(5.4)

Kapitel 5 Analoge Schaltungstechnik Integrierte Schaltungen II<br />

VB = VBE + IE ⋅RE ≈ 0.7V<br />

+ IC ⋅RE V ≈V − I R + R<br />

CE CC C C E<br />

Belasteter Spannungsteiler: IQ = KIB mit K = 3...10<br />

VB<br />

R2<br />

=<br />

K⋅IB 07 . V + IC ⋅RE<br />

07 . V + I<br />

≈<br />

=<br />

K⋅I I<br />

B<br />

C<br />

β<br />

⋅R<br />

R<br />

1<br />

(<br />

VCC −VB<br />

=<br />

K I<br />

( + 1)<br />

5.3 Kleinsignalverhalten<br />

Signalgrößen

Kapitel 5 Analoge Schaltungstechnik Integrierte Schaltungen II<br />

Einfaches quasistationäres Ersatzschaltbild nach Ebers-Moll im vorwärts-aktiven Bereich<br />

v BE<br />

i B<br />

g BE<br />

gm v BE<br />

Abbildung 5.9: Einfaches quasistationäres Ersatzschaltbild des NPN-Transistors<br />

Die Kenngrößen des Kleinsignalersatzbildes lauten:<br />

∂IB<br />

gBE<br />

=<br />

∂V<br />

I B<br />

Ap ≈<br />

V<br />

Differentieller Eingangsleitwert<br />

g<br />

g<br />

m<br />

CE<br />

BE<br />

T<br />

∂IC<br />

IC<br />

= | AP ≈<br />

Transkonduktanz<br />

∂V<br />

V<br />

BE<br />

T<br />

∂IC<br />

I<br />

= Ap ≈<br />

∂V<br />

V<br />

CE<br />

C<br />

eaf<br />

i B<br />

gm⋅ vBE = gm⋅<br />

≈β ⋅i<br />

g<br />

BE<br />

F B<br />

g CE<br />

Differentieller Ausgangsleitwert<br />

Vorwärts-aktiver-Betrieb, vereinfachtes Ebers-Moll Ersatzschaltbild<br />

I B<br />

VBE βF⋅IB Abbildung 5.10: Vereinfachtes Ebers-Moll-Ersatzschaltbild im vorwärts-aktiven Betrieb<br />

V ⎛ BE ⎞<br />

⎛<br />

VT<br />

IB ≈ ( 1−αF) I ⎜<br />

ES⎜<br />

e −1<br />

⎟<br />

≈ ( 1−αF)<br />

I ⎜<br />

ES⎜<br />

e<br />

⎝ ⎠<br />

⎝<br />

αF<br />

IC = β ⋅ IB = ( 1 −αF) IES ⋅e<br />

1−<br />

α<br />

g<br />

BE<br />

F<br />

V<br />

V<br />

1 ∂IB<br />

1<br />

⎛<br />

= ≈ ≈ ⋅( 1−α<br />

F) ⋅IES ⋅⎜e<br />

rBE<br />

∂VBE<br />

V<br />

⎜<br />

T<br />

⎝<br />

BE<br />

T<br />

V<br />

V<br />

BE<br />

T<br />

⎞<br />

⎟<br />

⎠<br />

⎞<br />

⎟<br />

I<br />

⎟<br />

⎠ V<br />

=<br />

VBE<br />

V B<br />

Berücksichtigung des endlichen Ausgangsleitwertes: ⇒ Early-Effekt<br />

Prof. Dr.-Ing. R. Laur - 105 -<br />

ITEM<br />

T<br />

T<br />

I C<br />

i C<br />

V CE<br />

v CE

Kapitel 5 Analoge Schaltungstechnik Integrierte Schaltungen II<br />

-Veaf<br />

Abbildung 5.11: Early-Effekt<br />

Unter Berücksichtigung des Early-Effektes ergibt sich:<br />

⎛ V<br />

IC = I'C⋅ ( 1+ ⋅ VCE) = I'C⋅<br />

⎜<br />

⎜1+<br />

⎝ V<br />

λ<br />

CE<br />

eaf<br />

⎞<br />

⎟<br />

⎠<br />

IC'<br />

IC<br />

dIC<br />

I<br />

⇒ gCE<br />

= ≈<br />

dV V<br />

Vollständiges π-Ersatzschalbild für höhere Frequenzen<br />

Für höhere Frequenzen ergibt sich nachfolgendes Ersatzschaltbild:<br />

v BE<br />

r B<br />

B B' C'<br />

C<br />

g BE<br />

v' BE<br />

C BE<br />

C BC<br />

r BC<br />

CE<br />

g mv' BE<br />

Abbildung 5.12: Vollständiges π-Ersatzschaltbild für höhere Frequenzen<br />

CBC: Sperrschichtkapazität<br />

CBE: Sperrschicht- und Diffusionskapazität<br />

rB, rC: Bahnwiderstände<br />

rBC: Rückwirkungswiderstand<br />

Vereinfachtes π-Ersatzschalbild für mittlere Frequenzen<br />

v BE<br />

i B<br />

C BC<br />

C<br />

eaf<br />

g CE<br />

r C<br />

VCE<br />

g C g BE BE<br />

mvBE gCE<br />

Abbildung 5.13: Vereinfachtes π-Ersatzschaltbild für mittlere Frequenzen<br />

Prof. Dr.-Ing. R. Laur - 106 -<br />

ITEM<br />

i C<br />

i C<br />

v CE<br />

v CE

Kapitel 5 Analoge Schaltungstechnik Integrierte Schaltungen II<br />

Frequenzgang der Kleinsignal-Stromverstärkung<br />

βF<br />

0<br />

Näherung: Tiefpaßverhalten mit β F =<br />

ω<br />

1+<br />

j<br />

mit 3dB Grenzfrequenz mit<br />

ωβ : ( ω )<br />

ω β<br />

!<br />

β F β =<br />

Bei ausgangsseitigem Kurzschluß ergibt sich<br />

mit:<br />

i ≈ g ⋅v − jω C ⋅v ≈ g ⋅v<br />

C m BE BC BE m BE<br />

( ( ) )<br />

iB ≈ gBE + jωCBE + CBC vBE<br />

β<br />

F<br />

iC<br />

gm<br />

= ≈<br />

i g + jωC + C<br />

B<br />

( )<br />

BE BE BC<br />

βF<br />

0 βF<br />

0<br />

=<br />

=<br />

ω<br />

ω<br />

1+ j<br />

1+<br />

j<br />

⎛ g<br />

ω BE ⎞<br />

β<br />

⎜ ⎟<br />

⎝ C + C ⎠<br />

g<br />

BE BC<br />

BE<br />

ω β ≈ ; βF 0<br />

CBE<br />

+ CBC<br />

=<br />

Definition: Transitfrequenz<br />

g<br />

g<br />

m<br />

BE<br />

β<br />

F 0<br />

2<br />

gm<br />

gBE<br />

=<br />

⎛ C + C<br />

1+<br />

jω⎜<br />

⎝ g<br />

BE BC<br />

Die Frequenz, bei der die Kleinsignal-Stromverstärkung auf 1 absinkt, wird als Transitfrequenz<br />

bezeichnet.<br />

( )<br />

!<br />

βF ωT = 1 , wobei gBE

Kapitel 5 Analoge Schaltungstechnik Integrierte Schaltungen II<br />

( )<br />

β ω<br />

F T<br />

!<br />

= 1 ≈<br />

ω<br />

g<br />

m<br />

( C + C )<br />

T BE BC<br />

g BE<br />

ωT ≈ β F 0 ⋅ = β F 0 ⋅ω<br />

C + C<br />

BE<br />

BC<br />

β<br />

Verstärkungs-Bandbreiteprodukt<br />

Da die Kapazitäten von Transistorflächen abhängig sind, lassen sich hohe Bandbreiten nur<br />

mit möglichst kleinen Transistorflächen erzielen.<br />

log f T<br />

Abbildung 5.15: Stromabhängigkeit der Transitfrequenz<br />

⇒ Optimale Bandbreite für maximales fT<br />

log I C<br />

Grund für verringertes fT bei niedrigen und hohen Strömen: Abfall von β (siehe Gummel-<br />

Poon-Modell<br />

5.3.2 Kleinsignalersatzschaltbild des MOSFET in Sättigung<br />

Die Kenngrößen des Kleinsignalersatzbildes des MOS-Transistors in Sättigung lauten:<br />

β<br />

2<br />

ID ≈ ⋅( VGS −VTS<br />

)<br />

Drainstrom in Sättigung<br />

2<br />

(<br />

VTS = VT0+ γ VSB+<br />

2ΦF− 2Φ<br />

F ) Schwellenspannung mit Substratsteuereffekt<br />

Der Eingangsleitwert kann bei der Kleinsignalbetrachtung aufgrund der Isolation des Gates<br />

vernachlässigt werden.<br />

g<br />

g<br />

m<br />

DS<br />

∂ID<br />

2I<br />

D<br />

= ≈β( VGS −VTS ) ≈ ≈ 2 ⋅β⋅IDTranskonduktanz ∂V<br />

V −V<br />

GS<br />

I<br />

=<br />

V<br />

∂<br />

∂<br />

D<br />

DS<br />

GS TS<br />

Differentieller Ausgangsleitwert<br />

Betrachtung der Kanallängenverkürzung:<br />

⎛ V<br />

ID = ID′ ( 1+ λVDS) = ID'<br />

⋅ ⎜<br />

⎜1+<br />

⎝ V<br />

=> g<br />

DS<br />

∂I<br />

D I<br />

= ≈ λ I D =<br />

∂V<br />

V<br />

DS<br />

D<br />

eaf<br />

DS<br />

eaf<br />

⎞<br />

⎟<br />

⎠<br />

Prof. Dr.-Ing. R. Laur - 108 -<br />

ITEM

Kapitel 5 Analoge Schaltungstechnik Integrierte Schaltungen II<br />

Substratsteuereffekt:<br />

g<br />

mb<br />

∂I<br />

=<br />

∂V<br />

= β<br />

= β<br />

= g<br />

= g<br />

( V −V<br />

)<br />

( V −V<br />

)<br />

m<br />

m<br />

D<br />

BS<br />

⋅<br />

GS<br />

GS<br />

⋅ χ<br />

TS<br />

TS<br />

γ<br />

⎛ ∂V<br />

⎜<br />

⎜−<br />

⎝ ∂V<br />

∂VTS<br />

∂V<br />

SB<br />

+ 2Φ<br />

TS<br />

BS<br />

⎞<br />

⎟<br />

⎠<br />

, mit χ =<br />

2<br />

2 VSB<br />

F<br />

VSB<br />

γ<br />

+ 2Φ<br />

Das Substrat steuert ebenso wie das Gate den Kanalstrom. Dieser Effekt wird Back-Gate-<br />

Effekt genannt. Der Steuer-Leitwert gmb ist um den Faktor χ kleiner als gm.<br />

g = χ ⋅g<br />

mb m<br />

typische Werte: γ ≈03 . V, Φ ≈13<br />

. V<br />

Tabelle 5.1: Back-Gate-Effekt<br />

2 F<br />

VSB 0V 3V 5V<br />

χ 0.13 0.07 0.06<br />

Das vollständige Kleinsignalersatzschaltbild des MOSFET in Sättgung ergibt sich daher zu:<br />

G<br />

S<br />

v GS<br />

i G<br />

C SB<br />

C GS<br />

C GD<br />

B<br />

C DB<br />

g mv GS<br />

F<br />

g mbv BS<br />

Abbildung 5.16: Kleinsignalersatzbild des MOSFET in Sättigung<br />

Prof. Dr.-Ing. R. Laur - 109 -<br />

ITEM<br />

g DS<br />

i D<br />

D<br />

v DS

Kapitel 5 Analoge Schaltungstechnik Integrierte Schaltungen II<br />

Grenzfrequenz des MOS-Transistors<br />

Unter Vernachlässigung von gmb, CDB, CSB, gDS ergibt sich:<br />

ω T<br />

ω<br />

T<br />

gm<br />

≈<br />

C + C<br />

GS GD<br />

=<br />

g<br />

C<br />

m<br />

OX<br />

W<br />

mit gm = β ⋅( VGS −VTS)<br />

und β = ⋅µ ⋅ COX ′ und COX = W⋅L⋅ COX<br />

′ ist<br />

L<br />

µ C<br />

W<br />

⋅ ′ ⋅ −<br />

=<br />

L<br />

C′ ⋅W⋅L ( V −V<br />

)<br />

( V V )<br />

OX GS TS<br />

OX<br />

µ GS TS 1<br />

= 2 ~ 2<br />

L L<br />

Optimale Grenzfrequenz für kurze Transistoren.<br />

5.4 Einfache bipolare Kleinsignal - Verstärkerschaltungen<br />

5.4.1 Emitter - Grundschaltung<br />

Beispiel: - Einstellung des Basisstroms über Basiswiderstand RB<br />

- Kapazitive Ein- /Auskopplung der Signale über Ci, Co<br />

C i<br />

Abbildung 5.17: Emitter-Grundschaltung<br />

vi<br />

R B<br />

VCC<br />

Kapazitive Kopplung ist nur in diskreter Schaltungstechnik wegen flächenaufwendiger<br />

Kapazitäten möglich. Direkte Kopplung der Stufen in integrierter Schaltungstechnik.<br />

Prof. Dr.-Ing. R. Laur - 110 -<br />

ITEM<br />

R C<br />

CO<br />

vo

Kapitel 5 Analoge Schaltungstechnik Integrierte Schaltungen II<br />

V BE'+v i<br />

V CC<br />

R C<br />

V CE'+v o<br />

Abbildung 5.18: Symbolische Darstellung der Arbeitspunkteinstellung über die Basis-<br />

Emitter-Spannung<br />

v gBE vBE gmvBE rCE i RC vo Abbildung 5.19: Kleinsignal-Ersatzschaltung der Emitterschaltung für niedrige Frequenzen<br />

Für niedrige Frequenzen gilt:<br />

( ) ( )<br />

vo =−gm⋅vBE ⋅ RC|| rCE =−gm RC|| rCE<br />

⋅vi<br />

vo<br />

AV<br />

= = − gm( RC|| rCE)<br />

v<br />

i<br />

In der Regel gilt rCE >> RC. Daraus resultiert die Kleinsignal-Spannungsverstärkung<br />

IC<br />

AV ≈ −g<br />

m ⋅ RC<br />

≈ − ⋅ RC<br />

v<br />

Abschätzung:<br />

V<br />

CE<br />

V<br />

≈<br />

2<br />

CC<br />

T<br />

, I<br />

C<br />

VCC<br />

≈<br />

2⋅<br />

R<br />

C<br />

, A<br />

V<br />

V<br />

≈ −<br />

2v<br />

Für VCC = 5V ⇒ AV ≈ -100 (das negative Vorzeichen bedeutet eine Phasendrehung um 180°)<br />

Eingangswiderstand: r<br />

i<br />

=<br />

g<br />

1 => einige kΩ<br />

Ausgangswiderstand: ro = RC|| rCE ≈ RC<br />

=> einige kΩ<br />

BE<br />

CC<br />

Prof. Dr.-Ing. R. Laur - 111 -<br />

ITEM<br />

T

Kapitel 5 Analoge Schaltungstechnik Integrierte Schaltungen II<br />

v i<br />

r i<br />

Abbildung 5.20: Ersatzschaltung der Verstärkerstufe als spannungsgesteuerte Spannungsquelle<br />

Frequenzverhalten, Miller-Kapazität<br />

v i<br />

gBE<br />

iCBC<br />

CBE<br />

CBC<br />

A Vv i<br />

r o<br />

AVv i<br />

Abbildung 5.21: Kleinsignal-Ersatzschaltbild für mittlere Frequenzen<br />

|AV| >> 1; AV < 0<br />

( | | v )<br />

i = jω⋅C ⋅ v + A ⋅<br />

≈ jω⋅C ⋅| A | ⋅v<br />

CBC BC i V i<br />

Miller-Kapazität<br />

CM = AV ⋅CBC BC V i<br />

CBC belastet den Eingang mit CM gang geliefert werden muß.<br />

= AV ⋅CBC zusätzlich zu CBE, da dieser Strom vom Ein-<br />

Miller-Effekt (bewirkt eine Reduzierung der Grenzfrequenz)<br />

v i<br />

r i<br />

C BE+C M<br />

A Vv i<br />

Abbildung 5.22: Kleinsignal-Ersatzschaltbild mit Miller-Kapazität<br />

Prof. Dr.-Ing. R. Laur - 112 -<br />

ITEM<br />

r o<br />

r o<br />

v o<br />

v o<br />

v o

Kapitel 5 Analoge Schaltungstechnik Integrierte Schaltungen II<br />

5.4.2 Kollektor - Grundschaltung, Emitterfolger<br />

V B'+v i<br />

V BE<br />

V CC<br />

Abbildung 5.23: Kollektor-Grundschaltung, Emitterfolger<br />

R E<br />

V E'+v o<br />

Qualitative Überlegung:<br />

Bei leitendem Basis-Emitter-Übergang ist die Spannung V BE ≈ 07 . ... 08 . V näherungsweise<br />

konstant.<br />

Daraus folgt:<br />

v ≈ v , A ≈1<br />

o i V<br />

Ausgangssignal am Emitter "folgt" dem Eingangssignal an der Basis. Die Kollektor-<br />

Schaltung wird daher auch als Emitterfolger bezeichnet.<br />

v i<br />

i B<br />

g BE<br />

v BE<br />

R E<br />

g mv BE<br />

Abbildung 5.24: Kleinsignal-Ersatzschaltbild des Emitterfolgers<br />

v<br />

BE<br />

i<br />

=<br />

g<br />

B<br />

BE<br />

iB<br />

gm⋅ vBE = βF ⋅gBE ⋅ = β ⋅i<br />

g<br />

BE<br />

( β 1)<br />

( || )<br />

( β 1)<br />

( ) (<br />

F B<br />

vo = F + iB RE rCE<br />

= + ⋅ v −v g ⋅ R || r )<br />

F i o BE E<br />

CE<br />

Prof. Dr.-Ing. R. Laur - 113 -<br />

ITEM<br />

r CE<br />

v o

Kapitel 5 Analoge Schaltungstechnik Integrierte Schaltungen II<br />

A<br />

V<br />

( βF<br />

+ 1)<br />

gBE( RE|| rCE)<br />

( β ) g ( R r )<br />

vo<br />

= =<br />

v 1+ + 1 ⋅ ⋅<br />

i<br />

|| E<br />

F BE E C<br />

In der Regel gilt: rCE >> RE, βF >> 1<br />

A<br />

V<br />

1<br />

≈<br />

1<br />

1+<br />

β ⋅R ⋅g<br />

F E BE<br />

Beispiel: IC = 1mA, RE = 0.5kΩ, βF = 100<br />

g<br />

BE<br />

IC<br />

≈<br />

β ⋅V<br />

F T<br />

AV ≈095 . ≈1<br />

≈ 04 . mS<br />

In der Regel gilt: AV ≈ 1, AV < 1 ⇒ Ein- und Ausgangssignal des Emitterfolgers liegen in<br />

Phase<br />

Eingangswiderstand:<br />

( ) ( )<br />

iB = vi −vo ⋅ gBE = vi − AV ⋅vi ⋅gBE mit rCE >> RE ergibt sich:<br />

1<br />

iB ≈ vi⋅gBE −<br />

1<br />

1+<br />

β ⋅g ⋅R<br />

r<br />

i<br />

F BE E<br />

⎡ ⎛ 1<br />

≈ ⎢1−⎜1−<br />

⎣ ⎝ β ⋅g ⋅R<br />

vi<br />

=<br />

β ⋅ R<br />

F E<br />

F BE E<br />

⋅v ⋅g<br />

⎞⎤<br />

⎟⎥<br />

⋅v ⋅g<br />

⎠⎦<br />

i BE<br />

i BE<br />

vi<br />

= ≈ βF ⋅RE<br />

=> extrem hoher Eingangswiderstand<br />

i<br />

B<br />

Beispiel: βF = 100, RE = 0.5kΩ<br />

=> ri ≈ 50kΩ<br />

; 1<br />

≈1− x, wenn x

Kapitel 5 Analoge Schaltungstechnik Integrierte Schaltungen II<br />

Ausgangswiderstand<br />

Signalquelle mit Innenwiderstand RS am Eingang.<br />

R S<br />

i B<br />

r BE<br />

R E<br />

ßF i B<br />

Abbildung 5.25: Bestimmung des Ausgangswiderstands des Emitterfolgers<br />

i<br />

B<br />

vo<br />

=−<br />

RS + rbe<br />

( β 1)<br />

v<br />

v<br />

o F + ⋅ o vo<br />

io =− ( βF<br />

+ 1)<br />

⋅ iB<br />

+ =<br />

+<br />

R || r R + r R || r<br />

( + )<br />

E CE<br />

i β o F 1 1<br />

= + = g<br />

v R + r R || r<br />

r<br />

o<br />

o<br />

S BE E CE<br />

vo<br />

1 R + r<br />

= = =<br />

i g β + 1<br />

mit rCE >> RE, βF >> 1:<br />

r<br />

o<br />

o<br />

R + r<br />

≈<br />

β<br />

0<br />

S BE<br />

F<br />

|| R<br />

E<br />

S BE<br />

F<br />

0<br />

( R r )<br />

|| ||<br />

E CE<br />

S BE<br />

E CE<br />

Unter der Voraussetzung einer niederohmigen Signalquelle (RS

Kapitel 5 Analoge Schaltungstechnik Integrierte Schaltungen II<br />

Stromverstärkung<br />

Zur Bestimmung der Stromverstärkung wird das Kleinsignal-Ersatzschaltbild bei ausgangsseitigem<br />

Kurzschluß betrachtet.<br />

i i<br />

gBE<br />

RE<br />

βF ⋅iB<br />

Abbildung 5.26: Kleinsignal-Ersatzschaltbild zur Bestimmung der Stromverstärkung<br />

( β 1 )<br />

i =− + ⋅i<br />

o F<br />

A<br />

I<br />

i<br />

io<br />

= = − ( βF + 1) ≈ −β<br />

F => hohe Stromverstärkung<br />

i<br />

i<br />

5.4.3 Basis - Grundschaltung<br />

E<br />

VEB'+v i<br />

Abbildung 5.27: Basis-Grundschaltung<br />

=> mittlere Leistungsverstärkung<br />

Kleinsignalrechnung mit entsprechenden Abschätzungen ergibt:<br />

AV ≈ gm⋅RC 1<br />

ri<br />

≈<br />

gm<br />

r ≈ R<br />

o C<br />

Eigenschaften der Basis-Schaltung:<br />

Hohe Spannungsverstärkung (100 . . . 200)<br />

Hoher Ausgangswiderstand ( . . . KΩ)<br />

B<br />

V CC<br />

R C<br />

C<br />

i o<br />

rCE<br />

VCB'+v o<br />

Prof. Dr.-Ing. R. Laur - 116 -<br />

ITEM

Kapitel 5 Analoge Schaltungstechnik Integrierte Schaltungen II<br />

Sehr niedriger Eingangswiderstand ( . . . Ω)<br />

Die Basisschaltung ist wegen ihrer hohen Bandbreite besonders für Hochfrequenzanforderungen<br />

geeignet.<br />

Höhere Verstärkungen lassen sich durch mehrstufige Verstärkerschaltungen erzielen. Da in<br />

intergrierten Schaltungen keine kapazitiven Kopplungen zwischen den einzelnen<br />

Verstärkerstufen möglich sind, ergibt sich das Problem der Einstellung des Arbeitspunktes.<br />

5.4.4 Kaskadenschaltung<br />

Die Kaskadenschaltung besteht aus jeweils einem npn- und einem pnp-Verstärker in Emitterschaltung.<br />

Das Ausgangssignal des npn-Verstärkers dient als Eingangssignal des pnp-<br />

Verstärkers.<br />

Abbildung 5.28: Kaskadenschaltung<br />

T1<br />

RC1<br />

VCC<br />

VBE1'+vi RC2 VC2'+vo Für die Spannungsverstärkung der Kaskadenschaltung ergibt sich unter der Bedingung, daß:<br />

r >> R<br />

BE2 C1<br />

A = g ⋅R ⋅g ⋅R<br />

V m1 C1 m2<br />

C2<br />

Ein- und Ausgangssignal der Kaskadenschaltung befinden sich in Phase.<br />

5.4.5 Darlington - Schaltung<br />

V B1'+v i<br />

Abbildung 5.29: NPN-Darlington-Stufe<br />

I B'<br />

T 1<br />

I C1<br />

I E1=I B2<br />

T 2<br />

V CC<br />

R C<br />

I C'<br />

I C2<br />

I E'<br />

T 2<br />

V CE2'+v o<br />

Prof. Dr.-Ing. R. Laur - 117 -<br />

ITEM

Kapitel 5 Analoge Schaltungstechnik Integrierte Schaltungen II<br />

Beide Transistoren können zusammen als ein Transistor aufgefaßt werden, der als Darlington-Transistor<br />

bezeichnet wird.<br />

B'<br />

I B'=I B1<br />

Abbildung 5.30: Darlington-Transistor<br />

I C1<br />

I E1=I B2<br />

Großsignalverhalten der Darlington-Schaltung<br />

VB'E' = VBE1+ VBE2<br />

≈14V<br />

. ⇒ ≈2⋅VBE von einstufigen Verstärkern<br />

I ≈ β ⋅ I′<br />

C1 1 B<br />

( ) IB IB β<br />

( )<br />

( 1)<br />

I = I ≈ + ⋅ ′<br />

B2 E1<br />

1 1<br />

I ≈ β ⋅I ≈ β ⋅ β + ⋅ ′<br />

C2 2 B2<br />

2 1 1<br />

[ ]<br />

I′ = I + I ≈ β + β β + ⋅ I′ ≈β ⋅β ⋅ I′<br />

mit β ≈ 100<br />

C C1 C2 1 2 1 B 1 2<br />

IC B<br />

′ ≈ β ′ ⋅ I′<br />

, mit β′ ≈ β1⋅β2 Der Darlington-Transistor entspricht einem Transistor mit hoher Stromverstärkung<br />

Kleinsignalverhalten<br />

ic'≈ β ′ ⋅iB'<br />

1 IC<br />

' I B'<br />

gBE<br />

'≈<br />

⋅ =<br />

2⋅ β ′ V 2⋅V<br />

g<br />

m<br />

IC<br />

'<br />

'≈<br />

2⋅V<br />

T<br />

T<br />

T<br />

B<br />

C'<br />

I C'<br />

I C2<br />

I E'<br />

E'<br />

β1⋅β2 gCE '≈ ⋅gCE<br />

3<br />

2<br />

2<br />

Die Spannungsverstärkung der Darlington-Schaltung entspricht der Emitter-Grundschaltung:<br />

A ≈−g ' ⋅<br />

V m<br />

R C<br />

Prof. Dr.-Ing. R. Laur - 118 -<br />

ITEM

Kapitel 5 Analoge Schaltungstechnik Integrierte Schaltungen II<br />

5.4.6 PNP - Darlington - Transistor<br />

In bipolaren Schaltungen sind PNP-Transistoren lediglich als laterale Transistoren mit niedriger<br />

Stromverstärkung zu realisieren. Die nachfolgende Darlington-Schaltung verhält sich wie<br />

ein PNP-Transistor mit hoher Stromverstärkung<br />

Abbildung 5.31: PNP-Darlington-Transistor<br />

I = I ≈ β ⋅ I′<br />

CP BN P B<br />

C′ ≈ βN ⋅ BN ≈βN ⋅ β PIB′<br />

I I<br />

I B<br />

B'<br />

IC′ = β' ⋅ ′ mit β'≈ β ⋅β<br />

N P<br />

IB'<br />

IEP<br />

ICP=IBN<br />

5.5 Einfache Kleinsignal - Verstärkerschaltungen in MOS - Technik<br />

Prinzipiell ergeben sich in der MOS-Technik wie bei den bipolaren Transistoren 3<br />

Grundschaltungen mit entsprechenden Schaltungen.<br />

5.5.1 Source - Grundschaltung<br />

Die Funktionsweise der Source-Schaltung entspricht der der Emitterschaltung in Bipolar-<br />

Technologie.<br />

V GS'+v i<br />

Abbildung 5.32: Source-Grundschaltung<br />

V B'<br />

V CC<br />

R D<br />

E'<br />

IE'<br />

ICN<br />

I C'<br />

C'<br />

V D'+v o<br />

Prof. Dr.-Ing. R. Laur - 119 -<br />

ITEM

Kapitel 5 Analoge Schaltungstechnik Integrierte Schaltungen II<br />

v i<br />

vGS gmVGS rDS RD Abbildung 5.33: Kleinsignal-Ersatzschaltung der Source-Schaltung<br />

( )<br />

AV =−gm⋅RD|| rDS ≈−gm⋅RD mit ri →∞ ergibt sich der Ausgangswiderstand zu<br />

r = r || R ≈ R<br />

o DS D<br />

D<br />

Beim Vergleich mit der bipolaren Schaltung zeigt sich, daß die Verstärkung erheblich geringer<br />

ist.<br />

IC<br />

Bipolar: gm<br />

≈<br />

V<br />

MOS: g ≈ 2⋅β ⋅I<br />

T<br />

m D<br />

Beispiel: ID = IC = 1mA<br />

W<br />

= 1; L<br />

A<br />

′ = 90 2; V<br />

A<br />

= ⋅ ′ = 90 2<br />

V<br />

W µ<br />

β<br />

µ<br />

β β<br />

L<br />

1mA<br />

gmBip<br />

( ) ≈ ≈400<br />

mS<br />

26mV<br />

µ A<br />

gm(<br />

MOS)<br />

≈ 290 ⋅ 2 ⋅1mA ≈04<br />

. mS<br />

V<br />

Für hohe Verstärkungen sind hohe Widerstandswerte für den Drain-Widerstand erforderlich.<br />

Diese lassen sich jedoch nicht oder nur mit erheblichem Platzaufwand realisieren. Der Drain-<br />

Widerstand wird in der integrierten Schaltungstechnik durch aktive Lastschaltungen ersetzt.<br />

5.5.2 Source - Schaltung mit Enhancement - Last<br />

VGS = VDS<br />

VCC<br />

ID<br />

VB VDS<br />

ID<br />

VTS<br />

a) b)<br />

Abbildung 5.34: a) Enhancement Lasttransistor, b) Übergangskennlinie<br />

Prof. Dr.-Ing. R. Laur - 120 -<br />

ITEM<br />

VDS<br />

v o

Kapitel 5 Analoge Schaltungstechnik Integrierte Schaltungen II<br />

VDS = VGS < VTS : ID=<br />

0<br />

V ≥V −V : I<br />

β<br />

≈ V<br />

2<br />

−V<br />

( )<br />

DS GS TS D DS TS<br />

v i+V GS1'<br />

2<br />

Transistor in Sättigung<br />

T 2<br />

T 1<br />

V CC<br />

Abbildung 5.35: Source-Schaltung mit Enhancement-Last<br />

Übertragungscharakteristik, Großsignalverhalten<br />

V 0<br />

VCC<br />

VCC-VT2<br />

I II III<br />

VT1<br />

v o+V DS1'<br />

Abbildung 5.36: Übertragungscharakteristik der Source-Schaltung mit Enhancement-Last<br />

Die Übertragungscharakteristik Vo=VDS1 = f(Vi=VGS1) läßt sich in drei Arbeitsbereiche unterteilen.<br />

I: T2 gesättigt, T1 ist gesperrt, da Vi < VT1<br />

T2 liefert lediglich geringen Sperrstrom<br />

VDS2 = VT2 : Vo = VCC - VT2<br />

II: T2 gesättigt, T1 ist leitfähig und in Sättigung, da Vi > VT1 und Vo > Vi - VT1<br />

näherungsweise lineare Übertragungscharakteristik<br />

Prof. Dr.-Ing. R. Laur - 121 -<br />

ITEM<br />

Vi

Kapitel 5 Analoge Schaltungstechnik Integrierte Schaltungen II<br />

III: T2 gesättigt, T1 im Triodenbereich, da Vi > VT1 und Vo < Vi - VT1<br />

Mit den vereinfachenden Voraussetzungen r DS ≈ oo und γ ≈ 0 (kein Substratsteuereffekt)<br />

kann folgendes Kleinsignalersatzschaltbild angenommen werden:<br />

VGS2<br />

gm2 v GS2<br />

vGS1 = vi vo<br />

gm1 v i<br />

Abbildung 5.37: Kleinsignalersatzschaltbild der Source-Schaltung mit Enhancement-Last in<br />

Bereich II<br />

vgs2 vo<br />

=−<br />

− g ⋅ v = g ⋅v<br />

A<br />

V<br />

m2 o m1<br />

i<br />

v<br />

=<br />

v<br />

o<br />

i<br />

g<br />

= −<br />

g<br />

m1<br />

m2<br />

= −<br />

2β1I<br />

2β<br />

I<br />

2<br />

D<br />

D<br />

= −<br />

( W ) L 1<br />

( W ) 2<br />

L<br />

Daraus resultiert die Forderung, daß T1 möglichst kurz und weit und T2 möglichst lang und<br />

schmal sein sollen, um eine hohe Spannungsverstärkung zu erhalten.<br />

Beispiel: ( )<br />

W L 1<br />

= 30 , ( W<br />

L) 2<br />

1<br />

= => AV = 30<br />

30<br />

5.5.3 Source-Schaltung mit Depletion-Last<br />

G<br />

D<br />

S<br />

ID<br />

VT = VDSAT<br />

a) b)<br />

Abbildung 5.38: a) Depletion-Lasttransistor, b) Übergangskennlinie<br />

Prof. Dr.-Ing. R. Laur - 122 -<br />

ITEM<br />

VDS

Kapitel 5 Analoge Schaltungstechnik Integrierte Schaltungen II<br />

v i+V GS1'<br />

Abbildung 5.39: Source-Schaltung mit Depletion-Last<br />

Übertragungscharakteristik, Großsignalverhalten<br />

VO VCC T2<br />

T1<br />

VCC<br />

I II III IV<br />

vo+VDS1'<br />

Abbildung 5.40: Übertragungscharakteristik der Source-Schaltung mit Depletion-Last<br />

I: Vi < VT1<br />

T1 gesperrt, ID = 0, kein Spannungsabfall über T2,<br />

⇒ Vo ≈ VCC<br />

II: Vi > VT1, Vo > VCC - |VT2|<br />

T1 ist leitfähig und in Sättigung, T2 ist leitfähig und im Triodengebiet<br />

⇒ Übertragungscharakteristik stark nichtlinear<br />

III: Vo < (VCC -|VT2|), Vo > (Vi - VT1) beide Transistoren leitfähig und in Sättigung<br />

⇒ lineare Übertragungscharakteristik (Verstärkerbereich)<br />

IV: Vo < (Vi - VT1)<br />

beide Transistoren leitfähig, T2 in Sättigung, T1 in Triodenbereich<br />

Prof. Dr.-Ing. R. Laur - 123 -<br />

ITEM<br />

V i

Kapitel 5 Analoge Schaltungstechnik Integrierte Schaltungen II<br />

v gs1 = v i<br />

g DS2<br />

Abbildung 5.41: Kleinsignal-Ersatzschaltbild der Source-Schaltung mit Depletion-Last in<br />

Bereich III<br />

g m1 v i<br />

Bestimmung der Kleinsignal-Spannungsverstärkung in Bereich III:<br />

v gs2<br />

v<br />

o<br />

A<br />

V<br />

= 0<br />

gm1<br />

=−<br />

g + g<br />

DS1 DS 2<br />

⋅ v<br />

vo<br />

gm1<br />

= = −<br />

v g + g<br />

i<br />

DS1 DS 2<br />

i<br />

W µ A<br />

′<br />

L<br />

2 D λ<br />

1<br />

V<br />

−1<br />

Beispiel: ( ) = 20,<br />

β = 90 , I = 1mA,<br />

= 0,<br />

01V<br />

5.5.4 Source - Schaltung mit Stromquellen - Last<br />

V GSP'<br />

Abbildung 5.42: PMOS-Stromquelle<br />

VCC<br />

I q<br />

MP<br />

g DS1<br />

⇒ AV<br />

VDSP<br />

≈ −95<br />

An das Gate des PMOS-Transistors wird die Spannung V GSP ′ = const angelegt; für<br />

VGSP ′ < VTP<<br />

0 ist MP<br />

leitfähig und für VDSP < V GSP ′ −VTP ist Mp<br />

gesättigt.<br />

Prof. Dr.-Ing. R. Laur - 124 -<br />

ITEM<br />

v o

Kapitel 5 Analoge Schaltungstechnik Integrierte Schaltungen II<br />

IQ<br />

I'<br />

Iq *<br />

|VGSP-VTP ' |<br />

Abbildung 5.43: Ausgangskennlinienfeld der PMOS-Stromquelle<br />

*<br />

Im Arbeitspunkt Q verhält sich der PMOS-Transistor wie eine ideale Stromquelle Iq mit parallelem<br />

Leitwert g . DSP<br />

VCC<br />

Iq<br />

gDSP<br />

Abbildung 5.44: Ersatzschaltbild der PMOS-Stromquelle<br />

I q *<br />

CMOS-Verstärker mit Stromquellen-Last<br />

Kein Backgate Einfluß, da VSBN und VSBP vom Signal unbeeinflußt sind.<br />

V' GS2<br />

V' GS1+v i<br />

Abbildung 5.45: CMOS-Verstärker mit Stromquellen-Last<br />

VCC<br />

T2<br />

T 1<br />

Q<br />

V'DS1+vo<br />

Prof. Dr.-Ing. R. Laur - 125 -<br />

ITEM<br />

|VDSP|

Kapitel 5 Analoge Schaltungstechnik Integrierte Schaltungen II<br />

V0<br />

V CC<br />

VCC-|VT2 |<br />

I II III IV<br />

VT1<br />

Verstärkerbereich<br />

Abbildung 5.46: Übertragungscharakteristik des CMOS-Verstärkers mit Stromquellen-Last<br />

I: Vi < VT1 ⇒ T1 ist gesperrt<br />

Vo > (VCC - |VT2|) ⇒ T2 ist leitfähig und im Triodenbereich<br />

Vo ≈ VCC<br />

II: Vi > VT1, Vo > (VCC - |VT2|) ⇒ T1 ist leitfähig und in Sättigung<br />

T2 ist leitfähig und im Triodenbereich<br />

⇒ stark nichtlineare Charakteristik<br />

IIII: Vo < (VCC -|VT2|), Vo > (Vi - VT1) ⇒ beide Transistoren sind leitfähig und in Sättigung<br />

⇒ Verstärkerbereich<br />

IV: Vo < (VCC -|VT2|), Vo > (Vi - VT1) ⇒ beide Transistoren leitfähig, T2 ist in Sättigung, T1 im<br />

Trodenbereich<br />

gDS2<br />

vi<br />

gm1 v gDS1<br />

vo<br />

i<br />

Abbildung 5.47: Kleinsignal-Ersatzschaltbild in Bereich III (beide Transistoren in Sättigung)<br />

Kleinsignal-Ersatzschaltbild im Bereich III<br />

vo<br />

=−<br />

g<br />

gm1⋅vi + g<br />

A<br />

Wegen:<br />

V<br />

DS1 DS 2<br />

gm1<br />

=−<br />

g + g<br />

DS1 DS 2<br />

Prof. Dr.-Ing. R. Laur - 126 -<br />

ITEM<br />

Vi

Kapitel 5 Analoge Schaltungstechnik Integrierte Schaltungen II<br />

g<br />

m<br />

2I<br />

D<br />

≈<br />

V −V<br />

GS T<br />

gDS ≈λ ⋅ID<br />

AV<br />

≈−<br />

V<br />

2⋅ I D<br />

−V ⋅λ⋅I ~ −<br />

1<br />

I<br />

⇒ AV<br />

~<br />

1<br />

I<br />

( )<br />

GS T D D<br />

Spannungsrückwirkung für einen typischen CMOS-Verstärker<br />

log|A V |<br />

10 3<br />

10 2<br />

10 -7<br />

D<br />

Sub-Threshold-Bereich<br />

10 -5 10 -3<br />

log(I D/A)<br />

Abbildung 5.48: Spannungsrückwirkung eines typischen CMOS-Verstärkers<br />

5.5.5 Source - Folger<br />

Die Funktionsweise des Sourcefolgers entspricht der des Emitterfolgers in Bipolar-<br />

Technologie.<br />

Beispiel: Source-Folger mit Stromquelle als Last<br />

V G'+v i<br />

V CC<br />

Abbildung 5.49: Source-Folger mit Stromquellen-Last<br />

I0'<br />

gQ<br />

VS'+vo<br />

Bei dieser Betrachtung wird der Back-Gate-Einfluß vernachlässigt. Ferner muß, da es sich um<br />

eine Kleinsignalbetrachtung handelt, die Ruhestromquelle I0<br />

' nicht berücksichtigt werden.<br />

Prof. Dr.-Ing. R. Laur - 127 -<br />

ITEM

Kapitel 5 Analoge Schaltungstechnik Integrierte Schaltungen II<br />

v i<br />

v GS gmvGS gDS<br />

Abbildung 5.50: Kleinsignal-Ersatzschaltbild des Source-Folgers mit Stromquellen-Last<br />

v = v − v<br />

v<br />

GS<br />

o<br />

A<br />

V<br />

i<br />

o<br />

gm⋅vGS =<br />

g + g<br />

DS Q<br />

gm<br />

=<br />

g + g<br />

vo<br />

1<br />

= ≈<br />

v g + g<br />

1+<br />

g<br />

DS Q<br />

i DS Q<br />

Wegen gm >> gDS, gQ ergibt sich<br />

A ≈ 1, A < 1<br />

V V<br />

m<br />

( v v )<br />

⋅ −<br />

i o<br />

wie beim Emitterfolger. Der Sourcefolger wird ebenfalls als Impedanzwandler eingesetzt.<br />

5.6 Leistungsverstärker<br />

Externe Systeme müssen in der Regel mit einer geeignet großen Signalleistung versorgt werden.<br />

Hohe Signalleistungen bedingen hohe Signalströme und/oder Signalspannungen.<br />

• Hohe Signalströme erfordern spezielle Leistungstransistoren großer Fläche, die sich<br />

prinzipiell als Parallelschaltung einer Vielzahl an Transistoren ergeben<br />

• Signalspannung ist durch die Versorgungsspannung begrenzt, die bei integrierten Schaltungen<br />

in der Regel nicht variabel ist<br />

Die folgende Skizze stellt den Leistungsfluß dar<br />

PS<br />

PV<br />

LV<br />

Abbildung 5.51: Schematische Darstellung eines Leistungsverstärkers<br />

Prof. Dr.-Ing. R. Laur - 128 -<br />

ITEM<br />

PQ<br />

PL<br />

gQ<br />

RL<br />

vo

Kapitel 5 Analoge Schaltungstechnik Integrierte Schaltungen II<br />

PQ: von Versorgungsspannung gelieferte Leistung<br />

PL: an Last abfallende Signalleistung<br />

PV: Verlustleistung, die im Verstärker in Joulesche Wärme umgewandelt wird<br />

PS: Signalleistung am Eingang, vernachlässigbar<br />

Wirkungsgrad:<br />

L<br />

η = P<br />

P<br />

Q<br />

( )<br />

PV = PQ − PL = 1−ηPQ Joulesche Wärme muß abgeführt werden. Daraus folgt die Forderung nach optimalem η ,<br />

insbesondere bei Verstärkern hoher Leistung.<br />

5.6.1 Klassen von Leistungsverstärkern<br />

Unter der Annahme eines harmonischen Eingangssignals, ergibt sich folgende Klassifizierung<br />

von Leistungsverstärkern.<br />

Klasse-A: Transistor leitet in beiden Halbperioden. Kollektorstrom pendelt um den<br />

Gleichstrom im Arbeitspunkt IC´<br />

ic<br />

IC'<br />

π 2π 3π 4π<br />

Abbildung 5.52: Kollektorstrom eines Klasse-A Leistungsverstärkers<br />

Klasse-B: Transistor leitet lediglich während einer Halbwelle, IC’=0<br />

ic<br />

π 2π 3π 4π<br />

Abbildung 5.53: Kollektorstrom eines Klasse-B Leistungsverstärkers<br />

Prof. Dr.-Ing. R. Laur - 129 -<br />

ITEM<br />

ωt<br />

ωt

Kapitel 5 Analoge Schaltungstechnik Integrierte Schaltungen II<br />

Klasse-AB: Transistor leitet etwas länger als eine Halbperiode:<br />

ic<br />

IC'<br />

π 2π 3π 4π<br />

ωt<br />

I<br />

′<br />

C < i<br />

c<br />

Abbildung 5.54: Kollektorstrom eines Klasse-AB Leistungsverstärkers<br />

Klasse-C: Transistor leitet weniger als eine Halbperiode<br />

ic<br />

π 2π 3π 4π<br />

Abbildung 5.55: Kollektorstrom eines Klasse-C Leistungsverstärkers<br />

Klasse-C Leistungsverstärker haben lediglich in der HF-Technik Bedeutung und sollen daher<br />

nicht weiter betrachtet werden.<br />

Ohne geeignete Maßnahmen (Gegentakt-Endstufen) liefern Klasse AB und B starke Verzerrungen<br />

des Ausgangssignals.<br />

Klasse-A-Verstärker: (typisch: Emitterschaltung)<br />

Abbildung 5.56: Klasse-A-Verstärker<br />

v i<br />

V CC<br />

il<br />

R L<br />

Die Emitter-Grundschaltung ist ein typischer Klasse-A-Verstärker.<br />

Prof. Dr.-Ing. R. Laur - 130 -<br />

ITEM<br />

V CE'<br />

vo<br />

ωt

Kapitel 5 Analoge Schaltungstechnik Integrierte Schaltungen II<br />

Für ′ = VCC<br />

V CE ergibt sich die maximale Ausgangsleistung unter Vernachlässigung der Sätti-<br />

2<br />

gungsspannung.<br />

V<br />

IC′<br />

=<br />

2R<br />

CC<br />

L<br />

CC () ( )<br />

i t<br />

u<br />

L<br />

P<br />

L<br />

L<br />

V<br />

= 1+ cosω t<br />

2R<br />

V<br />

2<br />

L<br />

CC () t = ( 1+<br />

cosωt)<br />

2<br />

V<br />

4R<br />

() () () ( ) 2<br />

CC<br />

t = u t ⋅i<br />

t = 1+<br />

cosωt<br />

L<br />

L<br />

L<br />

2 T<br />

2<br />

VCC<br />

1<br />

V 1 1<br />

P ′<br />

L = ⋅<br />

4RL<br />

T ∫ 4RL<br />

2 4<br />

0<br />

2 CC<br />

( 1+<br />

cosω<br />

t)<br />

dt = ⋅ = VCC<br />

⋅ IC<br />

V<br />

PQ t = VCC ⋅ iL() t = 1+ cosω<br />

t<br />

2R<br />

CC<br />

() ( )<br />

2<br />

2 T<br />

2<br />

VCC<br />

1<br />

V<br />

P Q = ⋅<br />

′<br />

RL<br />

T ∫ 1<br />

2<br />

2R<br />

0<br />

L<br />

η max<br />

L<br />

2 CC<br />

( 1+<br />

cosω<br />

t)<br />

dt = ⋅ = VCC<br />

⋅ IC<br />

PL<br />

VCC ⋅ IC'<br />

1<br />

= = = = 025 . ⇒ sehr ineffizient<br />

P 4⋅V<br />

⋅I<br />

' 4<br />

Q<br />

CC C<br />

PV min = 075 . ⋅ PQ<br />

= 3⋅PL Die dreifache Ausgangsleistung fällt als Verlustleistung im günstigsten Fall am Transistor ab.<br />

Klasse-B-Verstärker, Gegentakt-Endstufe<br />

v i<br />

V CC<br />

V CC<br />

Abbildung 5.57: Klasse-B-Verstärker, Gegentakt-Endstufe<br />

In jeder Halbwelle leitet einer der Transistoren, wenn gilt:<br />

Q N<br />

Q P<br />

Prof. Dr.-Ing. R. Laur - 131 -<br />

ITEM<br />

i L<br />

R L<br />

v o

Kapitel 5 Analoge Schaltungstechnik Integrierte Schaltungen II<br />

V > 06 07V<br />

,....<br />

i<br />

Unter Vernachlässigung dieser Schwellenspannung ergibt sich ein Klasse-B-Betrieb.<br />

Der jeweils leitende Transistor bildet mit RL einen Emitterfolger.<br />

angestrebtes<br />

Verhalten<br />

Abbildung 5.58: Übertragungscharakteristik eines Klasse-B-Verstärkers<br />

1V<br />

Durch die Schwellenspannungen ergeben sich Verzerrungen von ≈±07 . V im Übergangsbereich.<br />

Unter Vernachlässigung der Schwellenspannung und bei maximal möglicher Ansteuerung<br />

ergibt sich für die Spannung und den Strom an der Last<br />

()<br />

v t = V ⋅cosω t<br />

L CC<br />

()<br />

i t<br />

L<br />

VCC<br />

= ⋅cosω t<br />

R<br />

L<br />

Die Augenblicksleistung ergibt sich zu<br />

()<br />

P t<br />

L<br />

2<br />

VCC<br />

2<br />

= ⋅cos<br />

ω t .<br />

R<br />

L<br />

Für die Wirkleistung folgt damit:<br />

P<br />

L<br />

T<br />

2<br />

1 1 VCC<br />

= PL<br />

() t dt<br />

T ∫ = ⋅ .<br />

2 R<br />

0<br />

Für die Versorgungsquellen ergibt sich symmetrisch:<br />

P<br />

+<br />

Q<br />

P<br />

−<br />

Q<br />

L<br />

T<br />

2<br />

2<br />

VCC<br />

1 2 1 V<br />

= ⋅ cos tdt<br />

= ⋅<br />

R T ∫ ω<br />

π R<br />

L<br />

0<br />

T<br />

T<br />

2<br />

L<br />

2<br />

CC<br />

2<br />

VCC<br />

1 2 1 V<br />

= − ⋅ cos tdt<br />

= ⋅<br />

R T ∫ ω<br />

π R<br />

L<br />

2<br />

CC<br />

L<br />

Prof. Dr.-Ing. R. Laur - 132 -<br />

ITEM<br />

vo<br />

1V<br />

1V<br />

1V<br />

vi

Kapitel 5 Analoge Schaltungstechnik Integrierte Schaltungen II<br />

2<br />

CC<br />

+ − 2 V<br />

PQ = PQ + PQ<br />

= ⋅<br />

π R<br />

Wirkungsgrad maximal: η<br />

L<br />

max<br />

PL<br />

π<br />

= ≤ = 0. 785 (theoretische Grenze)<br />

P 4<br />

Q<br />

Nachteil: Verzerrungen wegen Schwellenspannung, die sich im Übergangsbereich auswirkt<br />

Klasse-AB-Verstärker<br />

Die Verzerrung im Übergangsbereich wird reduziert, wenn jeder Transistor einen kleinen<br />

Ruhestrom erhält, d.h eine Vorspannung der Basis vorgenommen wird.<br />

v i<br />

V BB<br />

2<br />

V BB<br />

2<br />

Abbildung 5.59: Klasse AB-Verstärker<br />

VBEN<br />

VBEP<br />

VCC<br />

Q N<br />

iN<br />

iP<br />

Q P<br />

Jeder Transistor leitet für etwas mehr als eine Halbperiode; dies entspricht der Definition der<br />

Klasse AB. Beide Transsistoren arbeiten als Emitterfolger, deshalb gilt mit hoher Genauigkeit:<br />

Es gilt:<br />

VBB<br />

vo( vi) = vi<br />

+ −07<br />

. V<br />

2<br />

∂v<br />

∂v<br />

o<br />

i<br />

VSS<br />

≈ 1, da Spannungsverstärkung bei Emitterfolgern ≈ 1<br />

i ≈ I ⋅ e<br />

i<br />

N S<br />

P<br />

≈ I<br />

S<br />

⋅e<br />

V<br />

V<br />

BEN<br />

T<br />

V<br />

−<br />

V<br />

BEP<br />

T<br />

Prof. Dr.-Ing. R. Laur - 133 -<br />

ITEM<br />

i L<br />

RL<br />

v o

Kapitel 5 Analoge Schaltungstechnik Integrierte Schaltungen II<br />

2 VT<br />

2 VT<br />

2<br />

i ⋅ i = I ⋅ e = I ⋅ e = I mit I = I ⋅e<br />

N P S<br />

V −V<br />

BEN BEP<br />

IQ: Querstrom für vi = vo = 0<br />

S<br />

V<br />

BB<br />

Q<br />

Q S<br />

IQ<br />

Wird vi positiv, steigt in an; ip wird entsprechend ip<br />

= kleiner. vo steigt proportional zu vi.<br />

in<br />

Dies entspricht dem Funktionsprinzip des Emitterfolgers.<br />

Der Wirkungsgrad dieser Schaltung ist < 0.785 ⇒ höhere Verlustleistung durch Basisvorspannung.<br />

Vorspannungserzeugung für Klasse-AB-Verstärker<br />

vI<br />

IBIAS<br />

D1<br />

D2<br />

iBN<br />

iBP<br />

VCC<br />

VBB<br />

iCN<br />

QN<br />

QP<br />

iCP<br />

VSS<br />

Abbildung 5.60: Vorspannungserzeugung für Klasse AB-Verstärker<br />

iL<br />

RL<br />

Die Konstantstromquelle erzeugt eine Vorspannung in Höhe von zwei Diodenflußspannungen<br />

über die Dioden D1, D2. Mit steigender Eingangsspannung steigen Kollektor- und damit Basisstrom<br />

des NPN-Transistors. Dadurch wird VBB geringfügig verringert und ist damit nicht mehr<br />

konstant.<br />

Dieser Nachteil wird durch die folgende VBE-Multiplizierer-Schaltung vermieden.<br />

Prof. Dr.-Ing. R. Laur - 134 -<br />

ITEM<br />

vo<br />

2<br />

V<br />

2V<br />

BB<br />

T<br />

-0.6<br />

vo<br />

vi

Kapitel 5 Analoge Schaltungstechnik Integrierte Schaltungen II<br />

vi<br />

i 1=i Q<br />

R 1<br />

i2<br />

R2 I Bias<br />

Q1<br />

iC1<br />

iBN<br />

VBB<br />

i BP<br />

Abbildung 5.61: VBE -Multiplizierer-Schaltung<br />

V CC<br />

Bei richtiger Dimensionierung des Spannungsteilers R1, R2 ist der Basisstrom von Q1 vernachlässigbar<br />

gegen den Querstrom IR des Spannungsteilers. An RL fällt VBE1 ab. Damit gilt:<br />

I<br />

2<br />

VBE1<br />

= ≈ I<br />

R<br />

2<br />

1<br />

V1 = I1⋅R1 ; mit I2 ≈ I1<br />

R<br />

V1 ≈ I2⋅ R1 = VBE<br />

⋅<br />

R<br />

1<br />

2<br />

R1<br />

⎛ R1<br />

⎞<br />

VBB = VBE + V1= VBE + VBE<br />

⋅ = VBE<br />

⋅ ⎜1<br />

+ ⎟<br />

R ⎝ R ⎠<br />

2<br />

Daraus resultiert die Bezeichnung VBE-Multiplizierer. Ein Teil des Stromes der Stromquelle IBias<br />

liefert den Kollektorstrom von Q1. Steigt iBn an, verringert sich entsprechend IC1 ohne daß sich<br />

VBB merklich ändert.<br />

Der Nachteil dieser Schaltung ist, daß der von Qn benötigte Basisstrom von IBias abgezogen<br />

wird. Damit ergibt sich eine Abhängigkeit der Spannung VBB vom Signalstrom. Weiterhin ist<br />

die Temperaturabhängigkeit von VBB zu beachten.<br />

5.7 Quellenschaltungen<br />

Betriebsspannungen integrierter Schaltungen werden gemäß Spezifikation nur innerhalb von<br />

Toleranzgrenzen festgelegt. In digitalen Schaltungen gilt zumeist:<br />

V = 5V ± ∆V ; mit ∆V<br />

= ± 10%<br />

DD DD DD<br />

In analogen Schaltungen ist die Betriebsspannung zumeist frei wählbar. Ströme sind stark von<br />

toleranzbehafteten Parametern und die wiederum stark von der Temperatur abhängig. Häufig<br />

müssen innerhalb von Schaltungen Referenzspannungen und Konstantspannungsquellen verfügbar<br />

sein.<br />

Prof. Dr.-Ing. R. Laur - 135 -<br />

ITEM<br />

2<br />

iCN<br />

Q N<br />

Q P<br />

iCP<br />

V SS<br />

i L<br />

RL<br />

vo

Kapitel 5 Analoge Schaltungstechnik Integrierte Schaltungen II<br />

V0<br />

R i → 0<br />

Vref<br />

Abbildung 5.62: Idealisierte Spannungs- und Stromquelle<br />

Problematik: Typische Eigenschaften integrierter Schaltungen<br />

• große Toleranzen der Parameterwerte (≈ ± 20%)<br />

• Temperaturabhängigkeit von Parametern (z.B. VBE(T))<br />

RL<br />

I 0<br />

VCC ,VDD<br />

Iref<br />

RL<br />

R i →∞<br />

• Begrenzter Wertebereich der Parameter (Widerstände können nicht beliebig groß realisiert<br />

werden)<br />

Vorteilhaft sind folgende Eigenschaften von integrierten Schaltungen:<br />

• große Anzahl aktiver Elemente<br />

• Parameter-Tracking<br />

• starke thermische Kopplung benachbarter Elemente<br />

• Geometrie und Layout sind beeinflußbar<br />

Daraus resultieren eine Vielzahl typischer Quellenschaltungen.<br />

5.7.1 Konstantspannungsquellen, Referenzspannungsquellen<br />

Während bei digitalen Schaltungen in der Regel enge Toleranzgrenzen für die Betriebsspannung<br />

vorgeschrieben sind, können analoge Schaltungen häufig mit unterschiedlichen Betriebsspannungen<br />

versorgt werden. Das macht genaue und stabile Referenzspannungsquellen<br />

erforderlich.<br />

Idealfall ist eine Quelle mit einer von Temperatur und Betriebsspannung unabhängigen Leerlaufspannung<br />

mit verschwindendem Innenwiderstand.<br />

Als einfache Spannungsquelle kann der VBE-Multiplizierer verwendet werden.<br />

Prof. Dr.-Ing. R. Laur - 136 -<br />

ITEM

Kapitel 5 Analoge Schaltungstechnik Integrierte Schaltungen II<br />

R1<br />

IQ<br />

IB<br />

R2 VBE<br />

Abbildung 5.63: VBE -Multiplizierer-Schaltung<br />

Bei geeigneter Dimensionierung des Spannungsteilers und hinreichend hoher Stromverstärkung<br />

des Transistors gilt mit guter Näherung:<br />

R + R<br />

V ≈V ( I ) ⋅<br />

R<br />

IC<br />

I<br />

VOUT<br />

IC<br />

mit I ≈ I , I > I , I =<br />

β<br />

1 2<br />

OUT BE C C Q B B<br />

2<br />

Der Kleinsignal-Innenwiderstand ergibt sich dann zu:<br />

r<br />

out<br />

∂v<br />

∂v<br />

= ≈ =<br />

∂i<br />

∂i<br />

C<br />

R + R<br />

R<br />

1 2<br />

2<br />

∂vBE<br />

⋅ ≈<br />

∂i<br />

R1 + R2<br />

1<br />

⋅ ≈<br />

R g<br />

C 2 m<br />

R + R<br />

R<br />

1 2<br />

2<br />

VT<br />

I<br />

⋅ , gm<br />

≈<br />

I V<br />

Niedrige Innenwiderstände ergeben sich nur auf Kosten hoher Ströme IC, dies bedeutet eine<br />

hohe Verlustleistung. Wesentlicher Nachteil der VBE-Multiplizierer-Schaltung ist allerdings die<br />

Temperaturabhängigkeit der Basis-Emitterspannung zu etwa 2mV/K.<br />

Bandgap-Reference-Konstantspannungsquelle<br />

Eine der bekanntesten Schaltungen zur Realisierung einer temperaturunabhängigen Spannungsreferenz<br />

ist die Bandgap-Referenzspannungsquelle. Mit dieser Schaltung läßt sich bei<br />

geeigneter Dimensionierung aufgrund gegenläufiger, sich kompensierender Temperatureffekte<br />

eine stabile Referenzspannung von VREF ≈ 1.25V erzeugen. Die Referenzspannung wird aus<br />

einer Basis-Emitter-Spannung VBE und einer Spannung VT ⋅K zusammengesetzt (VT = Temperaturspannung).<br />

Dies entspricht etwa dem Si-Bandabstand, daher die Bezeichnung. Dabei wählt<br />

man die Spannung VT⋅K so, daß deren positiver Temperaturkoeffizient gerade den negativen<br />

Koeffizienten von VBE kompensiert. Abbildung 5.64 zeigt das generelle Prinzip. Die Spannung<br />

VBE ist mit einem Temperaturkoeffizienten von -2 mV/°C behaftet. Der Temperaturkoeffizient<br />

der Temperaturspannung VT hat den positiven Wert von +0,085 mV/°C. Die Ausgangsspannung<br />

errechnet sich nach folgender Gleichung (K ist eine Konstante, mit der die Temperaturspannung<br />

multipliziert wird):<br />

VREF = VBE + K⋅VT<br />

Es soll nun zunächst der Wert für K bestimmt werden, bei dem der Temperaturkoeffizient für<br />

die Ausgangsspannung Null ist.<br />

2<br />

K = = 23, 5<br />

0, 085<br />

Prof. Dr.-Ing. R. Laur - 137 -<br />

ITEM<br />

C<br />

C<br />

T

Kapitel 5 Analoge Schaltungstechnik Integrierte Schaltungen II<br />

23, 5 ⋅26 mV ≈ 0, 6 V , bei Raumtemperatur<br />

Nimmt man für VBE einen Wert von 0,65V an, so errechnet sich eine Ausgangsspannung von<br />

1,25 V.<br />

V CC<br />

Generator<br />

VT<br />

Verstärker<br />

K<br />

+<br />

VREF = VBE + KVT Abbildung 5.64: Prinzipschaltbild der Bandgap-Referenzspannungsquelle<br />

In Abbildung 5.65 ist die entsprechende Transistorschaltung der Bandgap-<br />

Referenzspannungsquelle dargestellt.<br />

V 1<br />

R V<br />

R 1<br />

V BE1<br />

I 1<br />

T 1<br />

V BE2<br />

R2<br />

R 3<br />

I 2<br />

T 2<br />

I 3<br />

V2<br />

V BE3<br />

Abbildung 5.65: Bandgap-Referenzspannungsquelle<br />

I3 ≈ I2<br />

∆V BE<br />

T 3<br />

V REF<br />

I1<br />

I2⋅ R3 = VBE1 − VBE2 = VT⋅<br />

ln = ∆VBE , T1<br />

= T2 , beide Transistoren identisch<br />

I<br />

2<br />

Prof. Dr.-Ing. R. Laur - 138 -<br />

ITEM

Kapitel 5 Analoge Schaltungstechnik Integrierte Schaltungen II<br />

I<br />

2<br />

V<br />

R R V<br />

∆ BE 1 I<br />

= = ⋅ T ⋅ln<br />

I<br />

3 3<br />

R<br />

V I R<br />

R V<br />

2 I<br />

2 = 2⋅ 2 = ⋅ T ⋅ln<br />

I<br />

3<br />

R<br />

V V V V<br />

R V<br />

2 I1<br />

REF = BE3 + 2 = BE3 + ⋅ T ⋅ln<br />

≈ 1.26V<br />

I<br />

1<br />

2<br />

1<br />

2<br />

3<br />

2<br />

Die letzte Gleichung entspricht der Gleichung des Prinzipschaltbildes, wobei sich die folgende<br />

Konstante K ergibt:<br />

K R2<br />

I<br />

= ⋅ln<br />

R I<br />

3<br />

1<br />

2<br />

Bei geeigneter Dimensionierung der Bauelemente ergibt sich die Referenzspannung von ca.<br />

1,25 V. Aufgrund des temperaturabhängigen Quotienten I1/ I2<br />

ist die Referenzspannung nur<br />

in einem bestimmten Temperaturbereich um den nominalen Wert nahezu konstant. Bei Verwendung<br />

eines Operationsverstärkers läßt sich eine Schaltung aufbauen, die unabhängig von<br />

dem temperaturabhängigen Quotienten arbeitet.<br />

Abbildung 5.66 zeigt die Referenzspannungsquelle mit Operationsverstärker.<br />

R 2<br />

R 3<br />

T 2<br />

I 2<br />

R1<br />

T 1<br />

I 1<br />

∆V E<br />

-<br />

+<br />

V REF<br />

Abbildung 5.66: Bandgap-Referenzspannungsquelle mit Operationsverstärker<br />

Für Av →∞ gilt: ∆VE = 0 , bei endlicher Ausgangsspannung ⇒ V1<br />

≈ V2<br />

I<br />

I<br />

1<br />

2<br />

R2<br />

=<br />

R<br />

1<br />

I1⋅IS2 R ⋅ I<br />

V3 = ∆VBE = VBE1 − VBE2 = VT⋅ln<br />

= VT<br />

⋅ln<br />

I ⋅ I R ⋅ I<br />

2 S1<br />

V = V + V ≈ V + V = V + R ⋅<br />

2 S 2<br />

1 S1<br />

REF BE1 1 BE1 2 BE1<br />

2 I2 mit I2 ≈ I3<br />

Prof. Dr.-Ing. R. Laur - 139 -<br />

ITEM

Kapitel 5 Analoge Schaltungstechnik Integrierte Schaltungen II<br />

V V R V R<br />

V<br />

R R V<br />

3<br />

2 R2<br />

I<br />

REF = BE1 + 2⋅<br />

= BE1 + ⋅ T ⋅ln ⋅<br />

R I<br />

3<br />

Wenn beide Transistoren identisch sind (IS1 = IS2) ergibt sich:<br />

V V R V R<br />

V<br />

R R V<br />

3<br />

2 R<br />

REF = BE1 + 2⋅<br />

= BE1 + ⋅ T ⋅ln<br />

3<br />

3 R<br />

= V + K⋅V BE1 T<br />

3<br />

Diese Gleichung entspricht der Gleichung des Prinzipschaltbildes (siehe Abbildung 5.64).<br />

Die Schaltung nach Abbildung 5.66 kann in CMOS-Schaltungstechnik realisiert werden. T1<br />

und T2 sind dann durch die verfügbaren Substrattransistoren zu ersetzen.<br />

5.7.2 Konstantstromquellen, Stromspiegel<br />

Stromquellen werden häufig als sogenannte Stromspiegel realisiert. Dabei wird z.B. mit einem<br />

Widerstand eine Stromreferenz erzeugt, die eine stromgesteuerte Stromquelle ansteuert.<br />

Die gesteuerte Quelle besitzt einen hohen Innenwiderstand. Damit ist der Strom durch die<br />

Last weitgehend spannungsunabhängig. Die Last belastet den Referenzstrom nicht. Der Referenzstrom<br />

erscheint "gespiegelt" am Ausgang der gesteuerten Quelle.<br />

VCC<br />

R<br />

1<br />

2<br />

1<br />

S 2<br />

S1<br />

VCC<br />

RL (beliebiges Lastelement)<br />

IREF α⋅I REF R i →∞<br />

Abbildung 5.67: Prinzipschaltbild des Stromspiegels<br />

Die folgende Schaltung zeigt eine einfache Umsetzung des Prinzips mit Bipolartransistoren.<br />

Wegen VBE1 = VBE2 gilt unter Vernachlässigung des Ausgangswiderstandes von T2 (Early-<br />

Effekt) und bei identischen, benachbarten Transistoren IC2 ≈ IC1 und für β1 ≈ β2 >> 1:<br />

IC2 ≈ IC1 ≈ IREF<br />

Prof. Dr.-Ing. R. Laur - 140 -<br />

ITEM<br />

IL

Kapitel 5 Analoge Schaltungstechnik Integrierte Schaltungen II<br />

V CC<br />

R 1<br />

T1<br />

I REF<br />

Abbildung 5.68: Einfache Konstantstromquelle (Stromspiegel)<br />

IC1<br />

Wegen des Early-Effektes von T2 ist der Ausgangswiderstand begrenzt.<br />

I B1<br />

Die Toleranzen der "Bauelemente" , die Basisströme IB1 und IB2 sowie der begrenzte Ausgangswiderstand<br />

von T2 führen zu einer Abweichung vom Idealfall<br />

IC2 ≈ I REF<br />

Der Strom IC2 kann um den Faktor n vergrößert werden, wenn die Emitterfläche von T2 um den<br />

Faktor n vergrößert wird, oder besser, wenn n zu T1 identische Transistoren parallelgeschaltet<br />

werden:<br />

IC2 = n⋅IREF IB2<br />

T2<br />

RL<br />

IC2<br />

IREF IREF IREF<br />

Abbildung 5.69: Stromspiegel mit mehren Transistoren<br />

Prof. Dr.-Ing. R. Laur - 141 -<br />

ITEM

Kapitel 5 Analoge Schaltungstechnik Integrierte Schaltungen II<br />

VCC<br />

IC1<br />

T1<br />

IREF<br />

Abbildung 5.70: Modifizierter Stromspiegel (Widlar-Stromspiegel)<br />

R1<br />

I B1<br />

Erhält T2 einen Emitterwiderstand RE (Widlar-Schaltung) ergibt sich durch Stromgegenkopplung<br />

eine Erhöhung des Ausgangswiderstands. Steigt auf Grund des Early-Effektes (Anstieg<br />

des Kollektorpotentials von T2) IC2 an, wird durch den Spannungsabfall an RE die Basis-<br />

Emitterspannung an T2 reduziert, was der Stromzunahme entgegenwirkt.<br />

In guter Näherung gilt, wenn das Basispotential von T2 als konstant angenommen wird:<br />

mit:<br />

∆I<br />

C2<br />

ergibt sich:<br />

∆VCE2<br />

≈ − gm⋅∆VBE r<br />

CE<br />

∆V ≈ ∆I ⋅R ≈ ∆I<br />

⋅R<br />

BE2 E2 E C2 E<br />

∆V ∆V<br />

∆I ≈ −g ⋅R ⋅∆I<br />

2<br />

IB2<br />

CE2 CE 2<br />

C2 m E C2<br />

=<br />

rCE ( 1+<br />

gm⋅RE)<br />

⋅rCE<br />

∆I≈ r<br />

o<br />

C 2<br />

1<br />

∆VCE2<br />

+ g ⋅R ⋅r<br />

( )<br />

m E CE<br />

∆VCE2<br />

= ≈ ( 1 + g ⋅R ) ⋅r<br />

∆I<br />

C2<br />

V = V − I ⋅ R<br />

m E CE<br />

Der Ausgangswiderstand wird gegenüber der einfachen Stromspiegelschaltung um den Faktor<br />

1+ gm⋅RE erhöht, der Early-Effekt wird also deutlich reduziert.<br />

Wegen<br />

BE2 BE1 E2 E<br />

ist bei gleicher Transistorgröße IC2 < IC1. Durch Vergrößerung der Emitterfläche von T2 kann<br />

dieser Effekt kompensiert werden.<br />

Prof. Dr.-Ing. R. Laur - 142 -<br />

ITEM<br />

T2<br />

R L<br />

I C2<br />

RE

Kapitel 5 Analoge Schaltungstechnik Integrierte Schaltungen II<br />

Mit<br />

I ≈ I ⋅ e<br />

C1S V<br />

V<br />

BE1<br />

gilt für den Kollektorstrom von T2<br />

I<br />

C 2<br />

Der Faktor<br />

≈ I<br />

S<br />

⋅e<br />

V<br />

T<br />

BE1<br />

−I<br />

V<br />

C 2<br />

T<br />

⋅R<br />

IC2⋅RE −<br />

V IC2<br />

T α = e ≈<br />

I<br />

C1<br />

E<br />

≈ I<br />

C1<br />

⋅e<br />

−I<br />

C 2⋅R<br />

V<br />

T<br />

E<br />

.<br />

bestimmt das Verhältnis von IC2 und IC1. Ist dieses und IC2 vorgegeben, kann der Emitterwiderstand<br />

RE berechnet werden.<br />

Beispiel:<br />

Mit<br />

g<br />

m<br />

I<br />

=<br />

V<br />

C 2<br />

T<br />

IC2= 100µ A , α = 01 .<br />

R<br />

E<br />

VT<br />

≈ - ⋅ln α ≈ 600Ω<br />

I<br />

C 2<br />

ergibt sich als Faktor der Erhöhung des Ausgangswiderstandes:<br />

1+ g ⋅ R = 1+ 23≈33<br />

m E , ,<br />

Bei der Wilson-Schaltung (siehe Abbildung 5.71) ist die Erhöhung des Ausgangswiderstandes<br />

erheblich höher.<br />

V CC<br />

Abbildung 5.71: Wilson-Stromquelle<br />

R1<br />

I C1<br />

T1<br />

IREF<br />

Bei identischen Transistoren mit β1 = β2 = β3 >> 1 gilt:<br />

Prof. Dr.-Ing. R. Laur - 143 -<br />

ITEM<br />

T3<br />

T 2<br />

R L<br />

I C3

Kapitel 5 Analoge Schaltungstechnik Integrierte Schaltungen II<br />

Erhöht sich z.B. aufgrund von Laständerungen das Kollektorpotential von T3 bleibt VE3 konstant.<br />

Es gilt:<br />

V 2 = V 2 = V<br />

V = V + V<br />

CE BE BE1<br />

CE1 BE2 BE3<br />

IREF bleibt näherungsweise unverändert und es gilt:<br />

I ≈ I ≈ I ≈ I<br />

C2 C3 C1 REF<br />

Für den Ausgangsstrom ergibt sich:<br />

∆I = ∆I + ∆I = − ∆I + ∆I ⇒ ∆I ≈ ⋅∆<br />

C2 B3 C3 C1 C3 C3<br />

2<br />

I C1<br />

, da ∆I<br />

C1 ≈ ∆IC2<br />

Daraus resultiert:<br />

β F<br />

∆IC 3 = −β<br />

F ⋅∆I<br />

C1<br />

+ ∆VC3<br />

⋅ gCE3<br />

= − ⋅∆I<br />

C3<br />

+ ∆VC3<br />

⋅ gCE<br />

.<br />

2<br />

Der Ausgangswiderstand der Wilson-Quelle ergibt sich mit βF >> 1 zu:<br />

r<br />

o<br />

∆VC3<br />

⎛ βF⎞βF = ≈ ⎜1+<br />

⎟ ⋅rCE ≈ ⋅r<br />

∆I<br />

⎝ 2 ⎠ 2<br />

C3<br />

3 CE3<br />

Dies entspricht einer Erhöhung des Ausgangswiderstands gegenüber der einfachen Stromspiegelschaltung<br />

um einen Faktor von etwa 50 ... 75.<br />

Einfache Stromspiegelschaltung in MOS-Technik<br />

Die einfache Stromspiegelschaltung in MOS-Technik ist entsprechend Abbildung 5.72 aufgebaut.<br />

I REF<br />

M 1<br />

V DD<br />

R 1<br />

V DD<br />

Abbildung 5.72: Einfache Stromspiegel-Schaltung in MOS-Technik<br />

Für den Referenzstrom gilt hier:<br />

Prof. Dr.-Ing. R. Laur - 144 -<br />

ITEM<br />

I o<br />

R L<br />

M 2

Kapitel 5 Analoge Schaltungstechnik Integrierte Schaltungen II<br />

I<br />

1 1<br />

2<br />

= ⋅( V − V ) = ⋅β⋅( V −V ) ⋅ ( 1+<br />

λ ⋅V<br />

)<br />

R 2<br />

REF DD GS GS T GS<br />

1<br />

Mit dem Widerstand R1 wird der Referenzstrom eingestellt. Bei gegebener Dimensionierung<br />

von Transistor bestimmt der Referenzstrom die Steuerspannung VGS.<br />

Die eindeutige Ab-<br />

T 1<br />

hängigkeit der Gate-Source-Spannung des Transistors T1 vom Referenzstrom wird von dem<br />

Kurzschluß zwischen Drain und Gate von T1 verursacht. Für den Fall, daß beide Transistoren<br />

gleich sind, gilt näherungsweise:<br />

IREF = Io<br />

Bei Vernachlässigung der Kanallängenmodulation ist der Ausgangsstrom Io unabhängig von<br />

der Ausgangsspannung Vo.<br />

Bei unterschiedlicher Dimensionierung der Transistoren haben die Ströme ein konstantes<br />

Verhältnis zueinander:<br />

I<br />

I<br />

o<br />

REF<br />

= 2 2<br />

W / L<br />

W / L<br />

1 1<br />

In MOS-Stromspiegelschaltungen treten zwei Störeffekte auf. Die Einsatzspannung benachbarter<br />

Transistoren ist aufgrund von Herstellungstoleranzen nicht genau gleich. Für Kanallängen<br />

von 1 µm sind Abweichungen der Einsatzspannungen von 20 mV bis 40 mV realistisch.<br />

Wegen der Kanallängenmodulation hat der Transistor T2<br />

einen endlichen Ausgangswiderstand.<br />

Der Drainstrom von T2 ist somit schwach von der Ausgangsspannung Vo abhängig<br />

(ra ≈ rDS). Für den Fall, daß der Ausgangsstrom ein ganzzahliges Vielfaches des Referenzstroms<br />

sein soll, ist es sinnvoll, den Transistor T2 durch die Parallelschaltung von Transistoren,<br />

die genauso wie Transistor T1 dimensioniert sind, zu ersetzen. Durch dieses als „Matching“<br />

bezeichnete Prinzip können Randeffekte vermieden werden.<br />

Nachteilig gegenüber der Bipolarschaltung ist, daß die minimale Ausgangsspannung erheblich<br />

größer ist. Es gilt:<br />

V > V V<br />

o omin DS ≈ AT<br />

da sonst T2 im Triodengebiet betrieben wird.<br />

Die minimale Ausgangsspannung des Stromspiegels in MOS-Technologie liegt beispielsweise<br />

im Bereich von 1V, während sie bei der Bipolarschaltung der erheblich niedrigeren Sättigungsspannung<br />

von etwa 150mV entspricht.<br />

Wilson-Stromquelle in MOS-Technik<br />

Wie in der Bipolartechnik läßt sich auch in der MOS-Technik mit einer Wilson-<br />

Stromquelle (Abbildung 5.73) ein höherer Ausgangswiderstand realisieren.<br />

Prof. Dr.-Ing. R. Laur - 145 -<br />

ITEM

Kapitel 5 Analoge Schaltungstechnik Integrierte Schaltungen II<br />

I REF<br />

M 1<br />

V DD<br />

Abbildung 5.73: Wilson-Stromquelle in NMOS-Technik<br />

Wie anhand von Abbildung 5.73 zu erkennen, ist die Gate-Source-Spannung von T3 gleich der<br />

Drain-Gate-Spannung von T1. Aus diesem Grund benötigt die Wilson-Quelle keinen Kurzschluß<br />

zwischen Drain und Gate von T1. Eine Erhöhung des Ausgangsstromes Io bewirkt eine<br />

Vergrößerung der Gate-Source-Spannung von T1. Dies bedeutet wegen der Rückkopplung<br />

eine Verkleinerung der Gate-Source-Spannung von T3. Damit wird der auslösenden Ursache<br />

entgegengewirkt.<br />

Eine Berechnung des Ausgangswiderstandes ergibt das folgende Ergebnis:<br />

r = r ⋅g ⋅r<br />

o DS3 m1 DS1<br />

Die Wilson-Stromquelle weist gegenüber der einfachen Stromspiegelschaltung einen um den<br />

Faktor gm1⋅rDS1 höheren Ausgangswiderstand auf.<br />

Die Wilson-Quelle läßt sich auch in PMOS-Technologie realisieren, heute werden jedoch<br />

zumeist CMOS-Schaltungen verwendet.<br />

Prof. Dr.-Ing. R. Laur - 146 -<br />

ITEM<br />

V DD<br />

I o<br />

M 3<br />

M 2

Kapitel 5 Analoge Schaltungstechnik Integrierte Schaltungen II<br />

5.8 Differenzverstärker<br />

Zwei beliebige Signale v1, v2 können eindeutig in ein Differenzsignal vD und ein Gleichtaktsignal<br />

vC zerlegt werden:<br />

vD<br />

v D v 1 = + vC<br />

; v 2 = − + vC<br />

;<br />

2<br />

2<br />

v D<br />

= v − v ;<br />

1<br />

2<br />

v C<br />

v1<br />

+ v2<br />

=<br />

2<br />

Aufgabe eines Differenzverstärkers ist die alleinige Verstärkung des Differenzsignals vD unabhängig<br />

vom Gleichsignal vC.<br />

Abbildung 5.74: Prinzipschaltbild eines Differenzverstärkers<br />

Das Übertragungsverhalten lautet:<br />

v = A ⋅v<br />

+ A ⋅v<br />

o<br />

VD<br />

D<br />

VC<br />

C<br />

v 1<br />

v 2<br />

v D<br />

Die Differenzverstärkung AVD soll im Vergleich zur Gleichtaktverstärkung AVC möglichst<br />

groß sein.<br />

Das Verhältnis<br />

AVD<br />

= CMRR ≈<br />

A<br />

VC<br />

4 5 [ 10 ... 10 ]<br />

wird als Gleichtaktunterdrückung (Common Mode Rejection Ratio, CMRR) bezeichnet, die<br />

im Idealfall möglichst groß sein sollte.<br />

Differenzverstärker sind für die monolithische Integration besonders geeignet, weil benachbarte<br />

Elemente auf einem Chip in ihren Parametern gut übereinstimmen, während die Absolutwerte<br />

der Parameter über eine Charge erheblich streuen können (Tracking). Zudem haben<br />

benachbarte Elemente auf einem Chip bei geeigneter Anordnung eine nahezu identische<br />

Temperatur. Temperatureffekte können damit als Gleichsignale aufgefaßt werden, die hinreichend<br />

unterdrückt werden.<br />

Geringe Parameterabweichungen gleicher benachbarter Elemente sind nicht zu vermeiden.<br />

Diese Unsymmetrien führen zu einer Ausgangsspannung V 0 ≠ 0 für V 0 . Als Eingangs-<br />

Offset-Spannung V<br />

= D<br />

OS wird die Spannung bezeichnet, die am Eingang für V 0 ≡ 0 erforderlich<br />

ist.<br />

[ µ .. ]<br />

V = V | 0 ≈ 100 V. 3mV<br />

OS D Vo =<br />

Entsprechend kann der Eingangs-Offset-Strom IOS definiert werden. Beide Parameter sind<br />

abhängig von Temperatur, Betriebsspannung und Gleichtaktsignal VC.<br />

Prof. Dr.-Ing. R. Laur - 146 -<br />

ITEM<br />

v O

Kapitel 5 Analoge Schaltungstechnik Integrierte Schaltungen II<br />

5.8.1 Bipolarer Differenzverstärker<br />

Der Differenzverstärker ist meist nach dem in Abbildung 5.75 gezeigten Prinzip aus zwei<br />

Transistoren mit gekoppelten Emittern aufgebaut. Es soll zunächst das Gleichspannungsverhalten<br />

des Differenzverstärkers betrachtet werden. Dabei wird von genau gleichen, idealen<br />

Transistoren (z.B. IS1 = IS2), gleichen Kollektorwiderständen sowie einer idealen Konstantstromquelle<br />

ausgegangen.<br />

V1<br />

RC<br />

T1<br />

+VCC<br />

I C1 IC2<br />

V01 V02<br />

REE<br />

VO<br />

IEE<br />

-VEE<br />

Abbildung 5.75: Differenzverstärker mit Emitterkopplung<br />

Großsignalverhalten für<br />

R EE →∞<br />

Kirchhoffsche Maschengleichung:<br />

− V + V − V + V =<br />

1 BE1 BE2<br />

2 0<br />

Für Transistoren im aktiven Bereich (nicht in Sättigung) gilt:<br />

IC1<br />

I<br />

VBE1 = VT⋅ln<br />

und VBE 2 = V T ⋅ln<br />

I<br />

I<br />

S1<br />

C2<br />

S 2<br />

⎛ IC1<br />

IC2<br />

⎞<br />

VD = V1 − V2 = VBE1 − VBE2 = VT<br />

⋅⎜ln −ln<br />

⎟<br />

⎝ IS1<br />

IS<br />

2 ⎠<br />

Mit IS1 = IS2<br />

= IS folgt:<br />

I ⎛ ⎞ ⎛ ⎞<br />

C1<br />

V1<br />

−V2<br />

VD<br />

= exp ⎜<br />

⎟ = exp ⎜<br />

⎟ , mit VD = V 1 −V2.<br />

IC<br />

2 ⎝ VT<br />

⎠ ⎝ VT<br />

⎠<br />

Prof. Dr.-Ing. R. Laur - 147 -<br />

ITEM<br />

T2<br />

R C<br />

V2

Kapitel 5 Analoge Schaltungstechnik Integrierte Schaltungen II<br />

Mit<br />

⎛ 1 ⎞ 1<br />

β<br />

IE1 =− ( IB1 + IC1) =− ⎜ + 1⎟<br />

⎜ ⎟<br />

⋅ IC1<br />

= − ⋅IC1<br />

, mit α =<br />