Zustandsautomaten - Lehrstuhl Technische Informatik, Universität ...

Zustandsautomaten - Lehrstuhl Technische Informatik, Universität ...

Zustandsautomaten - Lehrstuhl Technische Informatik, Universität ...

Erfolgreiche ePaper selbst erstellen

Machen Sie aus Ihren PDF Publikationen ein blätterbares Flipbook mit unserer einzigartigen Google optimierten e-Paper Software.

4 VHDL - Very High Speed IC Hardware Description Language<br />

Das letzte Kapitel zum Thema <strong>Zustandsautomaten</strong> soll einen kurzen Einblick in die<br />

Grundlagen von VHDL bieten. Dabei handelt es sich um eine Hardware-<br />

Beschreibungssprache, mit deren Hilfe <strong>Zustandsautomaten</strong> dargestellt werden können.<br />

Die Anfänge von VHDL liegen in den 90er Jahren. Ursprünglich wurde die Sprache im<br />

Auftrag des amerikanischen Militärs zur Dokumentation und Simulation von Hardware<br />

entwickelt. Der Grund dafür war der Wunsch nach einer eindeutigen Sprache; diese sollte<br />

dabei helfen, die damals hohe Fehlerrate in elektronischen Steuer- und Regelsystemen (z.B. in<br />

Flugzeugen) zu senken.<br />

Heute ist VHDL eine standardisierte Sprache, die vor allem in Europa verbreitet ist. Eine<br />

Untermenge der Sprache kann nun auch zur Synthese von Schaltnetzen und Schaltwerken<br />

genutzt werden.<br />

Die beiden folgenden Unterkapitel stellen jeweils einen kurzen Ausschnitt aus dem<br />

Sourcecode eines zu realisierenden <strong>Zustandsautomaten</strong> vor. Dabei handelt es sich um das<br />

Moore-Schaltwerk zur Impulsfolgeerkennung aus Kapitel 3.<br />

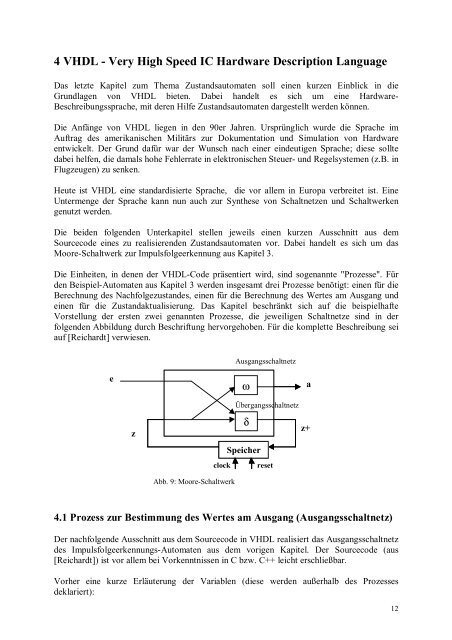

Die Einheiten, in denen der VHDL-Code präsentiert wird, sind sogenannte "Prozesse". Für<br />

den Beispiel-Automaten aus Kapitel 3 werden insgesamt drei Prozesse benötigt: einen für die<br />

Berechnung des Nachfolgezustandes, einen für die Berechnung des Wertes am Ausgang und<br />

einen für die Zustandaktualisierung. Das Kapitel beschränkt sich auf die beispielhafte<br />

Vorstellung der ersten zwei genannten Prozesse, die jeweiligen Schaltnetze sind in der<br />

folgenden Abbildung durch Beschriftung hervorgehoben. Für die komplette Beschreibung sei<br />

auf [Reichardt] verwiesen.<br />

e<br />

z<br />

Abb. 9: Moore-Schaltwerk<br />

Ausgangsschaltnetz<br />

clock reset<br />

4.1 Prozess zur Bestimmung des Wertes am Ausgang (Ausgangsschaltnetz)<br />

Der nachfolgende Ausschnitt aus dem Sourcecode in VHDL realisiert das Ausgangsschaltnetz<br />

des Impulsfolgeerkennungs-Automaten aus dem vorigen Kapitel. Der Sourcecode (aus<br />

[Reichardt]) ist vor allem bei Vorkenntnissen in C bzw. C++ leicht erschließbar.<br />

Vorher eine kurze Erläuterung der Variablen (diese werden außerhalb des Prozesses<br />

deklariert):<br />

ω<br />

Übergangsschaltnetz<br />

δ<br />

Speicher<br />

a<br />

z+<br />

12