Entwicklung eines Echtzeit-Strahlprofil-Monitoring-Systems für das ...

Entwicklung eines Echtzeit-Strahlprofil-Monitoring-Systems für das ...

Entwicklung eines Echtzeit-Strahlprofil-Monitoring-Systems für das ...

Sie wollen auch ein ePaper? Erhöhen Sie die Reichweite Ihrer Titel.

YUMPU macht aus Druck-PDFs automatisch weboptimierte ePaper, die Google liebt.

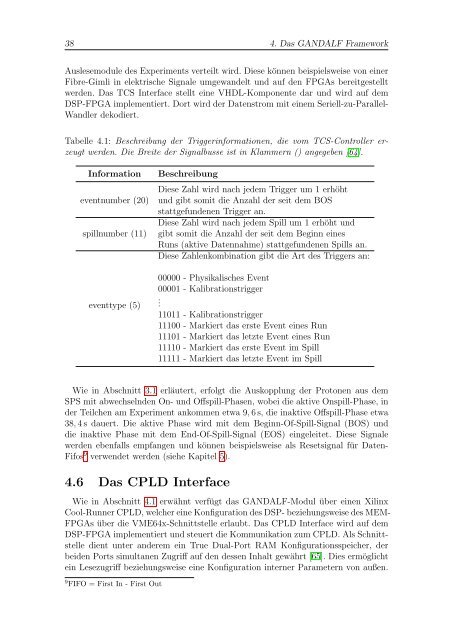

38 4. Das GANDALF FrameworkAuslesemodule des Experiments verteilt wird. Diese können beispielsweise von einerFibre-Gimli in elektrische Signale umgewandelt und auf den FPGAs bereitgestelltwerden. Das TCS Interface stellt eine VHDL-Komponente dar und wird auf demDSP-FPGA implementiert. Dort wird der Datenstrom mit einem Seriell-zu-Parallel-Wandler dekodiert.Tabelle 4.1: Beschreibung der Triggerinformationen, die vom TCS-Controller erzeugtwerden. Die Breite der Signalbusse ist in Klammern () angegeben [64].Informationeventnumber (20)spillnumber (11)eventtype (5)BeschreibungDiese Zahl wird nach jedem Trigger um 1 erhöhtund gibt somit die Anzahl der seit dem BOSstattgefundenen Trigger an.Diese Zahl wird nach jedem Spill um 1 erhöht undgibt somit die Anzahl der seit dem Beginn <strong>eines</strong>Runs (aktive Datennahme) stattgefundenen Spills an.Diese Zahlenkombination gibt die Art des Triggers an:00000 - Physikalisches Event00001 - Kalibrationstrigger.11011 - Kalibrationstrigger11100 - Markiert <strong>das</strong> erste Event <strong>eines</strong> Run11101 - Markiert <strong>das</strong> letzte Event <strong>eines</strong> Run11110 - Markiert <strong>das</strong> erste Event im Spill11111 - Markiert <strong>das</strong> letzte Event im SpillWie in Abschnitt 3.1 erläutert, erfolgt die Auskopplung der Protonen aus demSPS mit abwechselnden On- und Offspill-Phasen, wobei die aktive Onspill-Phase, inder Teilchen am Experiment ankommen etwa 9, 6 s, die inaktive Offspill-Phase etwa38, 4 s dauert. Die aktive Phase wird mit dem Beginn-Of-Spill-Signal (BOS) unddie inaktive Phase mit dem End-Of-Spill-Signal (EOS) eingeleitet. Diese Signalewerden ebenfalls empfangen und können beispielsweise als Resetsignal <strong>für</strong> Daten-Fifos 9 verwendet werden (siehe Kapitel 5).4.6 Das CPLD InterfaceWie in Abschnitt 4.1 erwähnt verfügt <strong>das</strong> GANDALF-Modul über einen XilinxCool-Runner CPLD, welcher eine Konfiguration des DSP- beziehungsweise des MEM-FPGAs über die VME64x-Schnittstelle erlaubt. Das CPLD Interface wird auf demDSP-FPGA implementiert und steuert die Kommunikation zum CPLD. Als Schnittstelledient unter anderem ein True Dual-Port RAM Konfigurationsspeicher, derbeiden Ports simultanen Zugriff auf den dessen Inhalt gewährt [65]. Dies ermöglichtein Lesezugriff beziehungsweise eine Konfiguration interner Parametern von außen.9 FIFO = First In - First Out