SASCO Information & News - ISI-Design

SASCO Information & News - ISI-Design

SASCO Information & News - ISI-Design

Sie wollen auch ein ePaper? Erhöhen Sie die Reichweite Ihrer Titel.

YUMPU macht aus Druck-PDFs automatisch weboptimierte ePaper, die Google liebt.

Application Briefs<br />

HCPL - 316 J -<br />

2.0 A Gate Drive Optokoppler -<br />

Start - Sequenz<br />

Der HCPL-316J ist ein<br />

hochintegrierter Baustein<br />

zur Leistungssteuerung,<br />

der über alle für eine vollständige,<br />

isolierte IGBT-<br />

Ansteuerung nötigen Komponenten<br />

verfügt.<br />

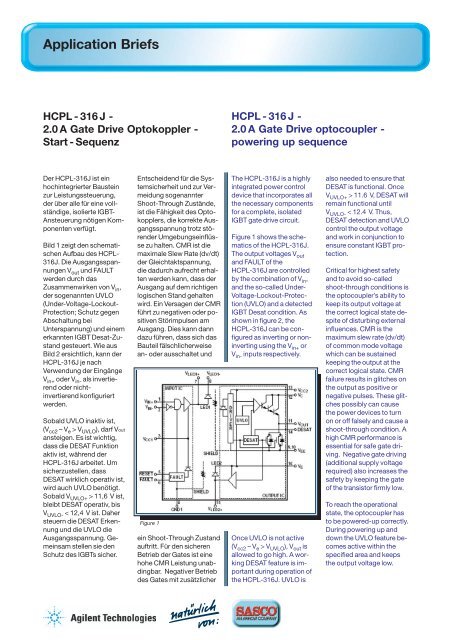

Bild 1 zeigt den schematischen<br />

Aufbau des HCPL-<br />

316J. Die Ausgangsspannungen<br />

V out und FAULT<br />

werden durch das<br />

Zusammenwirken von V in ,<br />

der sogenannten UVLO<br />

(Under-Voltage-Lockout-<br />

Protection; Schutz gegen<br />

Abschaltung bei<br />

Unterspannung) und einem<br />

erkannten IGBT Desat-Zustand<br />

gesteuert. Wie aus<br />

Bild 2 ersichtlich, kann der<br />

HCPL-316J je nach<br />

Verwendung der Eingänge<br />

V in+ oder V in- als invertierend<br />

oder nichtinvertierend<br />

konfiguriert<br />

werden.<br />

Sobald UVLO inaktiv ist,<br />

(V cc2 – V e > V UVLO ), darf Vout<br />

ansteigen. Es ist wichtig,<br />

dass die DESAT Funktion<br />

aktiv ist, während der<br />

HCPL-316J arbeitet. Um<br />

sicherzustellen, dass<br />

DESAT wirklich operativ ist,<br />

wird auch UVLO benötigt.<br />

Sobald V UVLO+ > 11,6 V ist,<br />

bleibt DESAT operativ, bis<br />

V UVLO- < 12,4 V ist. Daher<br />

steuern die DESAT Erkennung<br />

und die UVLO die<br />

Ausgangsspannung. Gemeinsam<br />

stellen sie den<br />

Schutz des IGBTs sicher.<br />

Entscheidend für die Systemsicherheit<br />

und zur Vermeidung<br />

sogenannter<br />

Shoot-Through Zustände,<br />

ist die Fähigkeit des Optokopplers,<br />

die korrekte Ausgangsspannung<br />

trotz störenderUmgebungseinflüsse<br />

zu halten. CMR ist die<br />

maximale Slew Rate (dv/dt)<br />

der Gleichtaktspannung,<br />

die dadurch aufrecht erhalten<br />

werden kann, dass der<br />

Ausgang auf dem richtigen<br />

logischen Stand gehalten<br />

wird. Ein Versagen der CMR<br />

führt zu negativen oder positiven<br />

Störimpulsen am<br />

Ausgang. Dies kann dann<br />

dazu führen, dass sich das<br />

Bauteil fälschlicherweise<br />

an- oder ausschaltet und<br />

Figure 1<br />

ein Shoot-Through Zustand<br />

auftritt. Für den sicheren<br />

Betrieb der Gates ist eine<br />

hohe CMR Leistung unabdingbar.<br />

Negativer Betrieb<br />

des Gates mit zusätzlicher<br />

HCPL - 316 J -<br />

2.0 A Gate Drive optocoupler -<br />

powering up sequence<br />

The HCPL-316J is a highly<br />

integrated power control<br />

device that incorporates all<br />

the necessary components<br />

for a complete, isolated<br />

IGBT gate drive circuit.<br />

Figure 1 shows the schematics<br />

of the HCPL-316J.<br />

The output voltages V out<br />

and FAULT of the<br />

HCPL-316J are controlled<br />

by the combination of V in ,<br />

and the so-called Under-<br />

Voltage-Lockout-Protection<br />

(UVLO) and a detected<br />

IGBT Desat condition. As<br />

shown in figure 2, the<br />

HCPL-316J can be configured<br />

as inverting or noninverting<br />

using the V in+ or<br />

V in- inputs respectively.<br />

Once UVLO is not active<br />

(V cc2 – V e > V UVLO ), V out is<br />

allowed to go high. A working<br />

DESAT feature is important<br />

during operation of<br />

the HCPL-316J. UVLO is<br />

also needed to ensure that<br />

DESAT is functional. Once<br />

V UVLO+ > 11.6 V, DESAT will<br />

remain functional until<br />

V UVLO- < 12.4 V. Thus,<br />

DESAT detection and UVLO<br />

control the output voltage<br />

and work in conjunction to<br />

ensure constant IGBT protection.<br />

Critical for highest safety<br />

and to avoid so-called<br />

shoot-through conditions is<br />

the optocoupler’s ability to<br />

keep its output voltage at<br />

the correct logical state despite<br />

of disturbing external<br />

influences. CMR is the<br />

maximum slew rate (dv/dt)<br />

of common mode voltage<br />

which can be sustained<br />

keeping the output at the<br />

correct logical state. CMR<br />

failure results in glitches on<br />

the output as positive or<br />

negative pulses. These glitches<br />

possibly can cause<br />

the power devices to turn<br />

on or off falsely and cause a<br />

shoot-through condition. A<br />

high CMR performance is<br />

essential for safe gate driving.<br />

Negative gate driving<br />

(additional supply voltage<br />

required) also increases the<br />

safety by keeping the gate<br />

of the transistor firmly low.<br />

To reach the operational<br />

state, the optocoupler has<br />

to be powered-up correctly.<br />

During powering up and<br />

down the UVLO feature becomes<br />

active within the<br />

specified area and keeps<br />

the output voltage low.