Download PDF (2 MB) - MathWorks Deutschland

Download PDF (2 MB) - MathWorks Deutschland

Download PDF (2 MB) - MathWorks Deutschland

Sie wollen auch ein ePaper? Erhöhen Sie die Reichweite Ihrer Titel.

YUMPU macht aus Druck-PDFs automatisch weboptimierte ePaper, die Google liebt.

26<br />

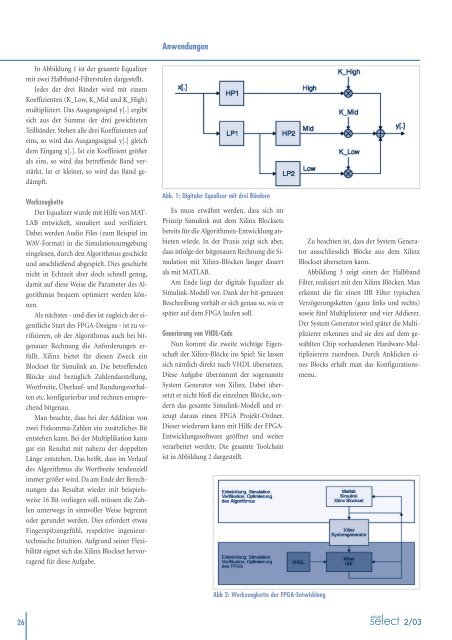

In Abbildung 1 ist der gesamte Equalizer<br />

mit zwei Halbband-Filterstufen dargestellt.<br />

Jedes der drei Bänder wird mit einem<br />

Koeffizienten (K_Low, K_Mid und K_High)<br />

multipliziert. Das Ausgangssignal y[.] ergibt<br />

sich aus der Summe der drei gewichteten<br />

Teilbänder. Stehen alle drei Koeffizienten auf<br />

eins, so wird das Ausgangssignal y[.] gleich<br />

dem Eingang x[.]. Ist ein Koeffizient größer<br />

als eins, so wird das betreffende Band verstärkt.<br />

Ist er kleiner, so wird das Band gedämpft.<br />

Werkzeugkette<br />

Der Equalizer wurde mit Hilfe von MAT-<br />

LAB entwickelt, simuliert und verifiziert.<br />

Dabei werden Audio Files (zum Beispiel im<br />

WAV-Format) in die Simulationsumgebung<br />

eingelesen, durch den Algorithmus geschickt<br />

und anschließend abgespielt. Dies geschieht<br />

nicht in Echtzeit aber doch schnell genug,<br />

damit auf diese Weise die Parameter des Algorithmus<br />

bequem optimiert werden können.<br />

Als nächstes - und dies ist zugleich der eigentliche<br />

Start des FPGA-Designs - ist zu verifizieren,<br />

ob der Algorithmus auch bei bitgenauer<br />

Rechnung die Anforderungen erfüllt.<br />

Xilinx bietet für diesen Zweck ein<br />

Blockset für Simulink an. Die betreffenden<br />

Blöcke sind bezüglich Zahlendarstellung,<br />

Wortbreite, Überlauf- und Rundungsverhalten<br />

etc. konfigurierbar und rechnen entsprechend<br />

bitgenau.<br />

Man beachte, dass bei der Addition von<br />

zwei Fixkomma-Zahlen ein zusätzliches Bit<br />

entstehen kann. Bei der Multiplikation kann<br />

gar ein Resultat mit nahezu der doppelten<br />

Länge entstehen. Das heißt, dass im Verlauf<br />

des Algorithmus die Wortbreite tendenziell<br />

immer größer wird. Da am Ende der Berechnungen<br />

das Resultat wieder mit beispielsweise<br />

16 Bit vorliegen soll, müssen die Zahlen<br />

unterwegs in sinnvoller Weise begrenzt<br />

oder gerundet werden. Dies erfordert etwas<br />

Fingerspitzengefühl, respektive ingenieurtechnische<br />

Intuition. Aufgrund seiner Flexibilität<br />

eignet sich das Xilinx Blockset hervorragend<br />

für diese Aufgabe.<br />

Anwendungen<br />

Abb. 1: Digitaler Equalizer mit drei Bändern<br />

Es muss erwähnt werden, dass sich im<br />

Prinzip Simulink mit dem Xilinx Blocksets<br />

bereits für die Algorithmen-Entwicklung anbieten<br />

würde. In der Praxis zeigt sich aber,<br />

dass infolge der bitgenauen Rechnung die Simulation<br />

mit Xilinx-Blöcken länger dauert<br />

als mit MATLAB.<br />

Am Ende liegt der digitale Equalizer als<br />

Simulink-Modell vor. Dank der bit-genauen<br />

Beschreibung verhält er sich genau so, wie er<br />

später auf dem FPGA laufen soll.<br />

Generierung von VHDL-Code<br />

Nun kommt die zweite wichtige Eigenschaft<br />

der Xilinx-Blöcke ins Spiel: Sie lassen<br />

sich nämlich direkt nach VHDL übersetzen.<br />

Diese Aufgabe übernimmt der sogenannte<br />

System Generator von Xilinx. Dabei übersetzt<br />

er nicht bloß die einzelnen Blöcke, sondern<br />

das gesamte Simulink-Modell und erzeugt<br />

daraus einen FPGA Projekt-Ordner.<br />

Dieser wiederum kann mit Hilfe der FPGA-<br />

Entwicklungssoftware geöffnet und weiter<br />

verarbeitet werden. Die gesamte Toolchain<br />

ist in Abbildung 2 dargestellt.<br />

Abb 2: Werkzeugkette der FPGA-Entwicklung<br />

Zu beachten ist, dass der System Generator<br />

ausschliesslich Blöcke aus dem Xilinx<br />

Blockset übersetzen kann.<br />

Abbildung 3 zeigt einen der Halbband<br />

Filter, realisiert mit den Xilinx Blöcken. Man<br />

erkennt die für einen IIR Filter typischen<br />

Verzögerungsketten (ganz links und rechts)<br />

sowie fünf Multiplizierer und vier Addierer.<br />

Der System Generator wird später die Multiplizierer<br />

erkennen und sie den auf dem gewählten<br />

Chip vorhandenen Hardware-Multiplizierern<br />

zuordnen. Durch Anklicken eines<br />

Blocks erhält man das Konfigurationsmenu.<br />

MATLAB<br />

select 2/03