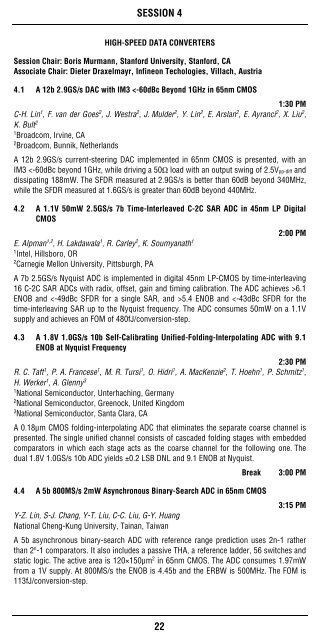

SESSION 4 HIGH-SPEED DATA CONVERTERS Session Chair: Boris Murmann, Stanford University, Stanford, CA Associate Chair: Dieter Draxelmayr, Infineon Techologies, Villach, Austria 4.1 A 12b 2.9GS/s DAC with IM3

Monday, February 9th 1:30 PM 4.5 A 600MS/s 30mW 0.13μm CMOS ADC Array Achieving Over 60dB SFDR with Adaptive Digital Equalization 3:45 PM 1 1,2 1,3 3 3 3 3 W. Liu , Y. Chang , S-K. Hsien , B-W. Chen , Y-P. Lee , W-T. Chen , T-Y. Yang , 3 1 G-K. Ma , Y. Chiu 1University of Illinois, Urbana-Champaign, IL 2Jilin University, Changchun, China 3Industrial Technology Research Institute, Hsinchu, Taiwan A 600MS/s 10-way time-interleaved SAR ADC array is fabricated in 0.13μm CMOS. Digital background equalization adaptively corrects the gain, offset, and linearity mismatch in the array, assisted by an algorithmic ADC. The prototype achieves 47.3dB peak SNDR and 65.2dB peak SFDR, while dissipating 30mW from a 1.2V supply. 4.6 A 10b 500MHz 55mW 90nm CMOS ADC 4:15 PM A. Verma, B. Razavi University of California, Los Angeles, CA A pipelined ADC consisting of 14 stages calibrates capacitor mismatch, and nonlinearity and gain error of opamps using an RDAC with 11b linearity. Employing a 2-stage opamp with a BW of 10GHz and a gain of 25, the 90nm digital CMOS ADC achieves a DNL of 0.4 LSB, an INL of 1 LSB and an SNDR of 53dB for a 233MHz input, while drawing 55mW from a 1.2V supply. The FOM is 0.3pJ/conversion-step. 4.7 A 16b 125MS/s 385mW 78.7dB SNR CMOS Pipelined ADC 4:45 PM S. Devarajan, L. Singer, D. Kelly, S. Decker, A. Kamath, P. Wilkins Analog Devices, Wilmington, MA A 16b 125MS/s pipelined ADC implemented in a 0.18μm CMOS process achieves an SNR of 78.7dB, an SNDR of 78.6dB and an SFDR of 96dB with a 30MHz input, while maintaining SNR >76dB and SFDR >80dB up to 150MHz with a clock jitter of 65fs. The ADC has a SHA-less 4b front-end and includes digital calibration and dither to improve small-signal linearity. The ADC consumes 385mW from a 1.8V supply. Conclusion 5:15 PM 23

- Page 1 and 2: IEEE SOLID-STATE CIRCUITS SOCIETY A

- Page 3 and 4: CONFERENCE INFORMATION Tutorials ..

- Page 5 and 6: Sunday, February 8th T1: Continuous

- Page 7 and 8: Sunday, February 8th Instructor: An

- Page 9 and 10: F1: SSD Memory Subsystem Innovation

- Page 11 and 12: F2: Medical Image Sensors Organizer

- Page 13 and 14: Time Topic 8:00 Breakfast Forum Age

- Page 15 and 16: Time Topic 8:00 Breakfast Forum Age

- Page 17 and 18: Monday, February 9th 8:15 AM PLENAR

- Page 19 and 20: Monday, February 9th 8:15 AM Adapti

- Page 21 and 22: Monday, February 9th 1:30 PM 2.4 A

- Page 23: Monday, February 9th 1:30 PM 3.5 Se

- Page 27 and 28: Monday, February 9th 1:30 PM 5.6 A

- Page 29 and 30: Monday, February 9th 1:30 PM 6.4 Si

- Page 31 and 32: SE4: Highlights of IEDM 2008 Organi

- Page 33 and 34: SE5: Things All RFIC Designers Shou

- Page 35 and 36: Tuesday, February 10th 8:30 AM 7.5

- Page 37 and 38: Tuesday, February 10th 8:30 AM 8.4

- Page 39 and 40: 9.5 A 0.13μm CMOS 78dB SNDR 87mW 2

- Page 41 and 42: Tuesday, February 10th 8:30 AM 10.5

- Page 43 and 44: Tuesday, February 10th 8:30 AM 11.5

- Page 45 and 46: Tuesday, February 10th 8:30 AM 12.6

- Page 47 and 48: Tuesday, February 10th 1:30 PM 13.4

- Page 49 and 50: Tuesday, February 10th 1:30 PM 14.4

- Page 51 and 52: Tuesday, February 10th 1:30 PM HIGH

- Page 53 and 54: Tuesday, February 10th 1:30 PM 17.5

- Page 55 and 56: RANGING AND Gb/s COMMUNICATION Sess

- Page 57 and 58: SESSION 19 ANALOG TECHNIQUES Sessio

- Page 59 and 60: SE6: Interleaving ADCs - Exploiting

- Page 61 and 62: SESSION 20 SENSORS AND MEMS Session

- Page 63 and 64: SESSION 21 10Gb/s-to-40Gb/s TRANSMI

- Page 65 and 66: PA AND ANTENNA INTERFACE Session Ch

- Page 67 and 68: SESSION 23 PLLs AND CLOCKs Session

- Page 69 and 70: SESSION 24 WIRELESS CONNECTIVITY Se

- Page 71 and 72: SESSION 25 MEDICAL Session Chair: A

- Page 73 and 74: SWITCHED-MODE TECHNIQUES Session Ch

- Page 75 and 76:

SESSION 27 SRAM AND EMERGING MEMORY

- Page 77 and 78:

SESSION 28 TD: DIRECTIONS IN COMPUT

- Page 79 and 80:

mm-WAVE CIRCUITS Session Chair: Fra

- Page 81 and 82:

SHORT COURSE Low-Voltage Analog and

- Page 83 and 84:

SHORT COURSE The Effect of Technolo

- Page 85 and 86:

Time Topic 8:00 Breakfast Forum Age

- Page 87 and 88:

Time Topic 8:00 Breakfast Forum Age

- Page 89 and 90:

Time Topic 8:00 Breakfast Forum Age

- Page 91 and 92:

This all-day forum encourages open

- Page 93 and 94:

INFORMATION • Local Chapter meeti

- Page 95 and 96:

INFORMATION other women in the prof

- Page 97 and 98:

COMMITTEES INTERNATIONAL TECHNICAL

- Page 99 and 100:

COMMITTEES MEMORY SUBCOMMITTEE (con

- Page 101 and 102:

EUROPEAN REGIONAL COMMITTEE ITPC EU

- Page 103 and 104:

FAR-EAST REGIONAL COMMITTEE (contin

- Page 105 and 106:

CONFERENCE SPACE LAYOUT The Confere

- Page 107:

Printed on Recycled Paper ISSCC 200