Download PDF - International Solid-State Circuits Conference

Download PDF - International Solid-State Circuits Conference

Download PDF - International Solid-State Circuits Conference

You also want an ePaper? Increase the reach of your titles

YUMPU automatically turns print PDFs into web optimized ePapers that Google loves.

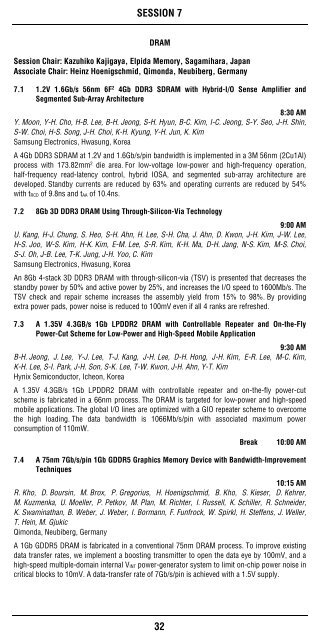

SESSION 7<br />

DRAM<br />

Session Chair: Kazuhiko Kajigaya, Elpida Memory, Sagamihara, Japan<br />

Associate Chair: Heinz Hoenigschmid, Qimonda, Neubiberg, Germany<br />

7.1 1.2V 1.6Gb/s 56nm 6F 2 4Gb DDR3 SDRAM with Hybrid-I/O Sense Amplifier and<br />

Segmented Sub-Array Architecture<br />

8:30 AM<br />

Y. Moon, Y-H. Cho, H-B. Lee, B-H. Jeong, S-H. Hyun, B-C. Kim, I-C. Jeong, S-Y. Seo, J-H. Shin,<br />

S-W. Choi, H-S. Song, J-H. Choi, K-H. Kyung, Y-H. Jun, K. Kim<br />

Samsung Electronics, Hwasung, Korea<br />

A 4Gb DDR3 SDRAM at 1.2V and 1.6Gb/s/pin bandwidth is implemented in a 3M 56nm (2Cu1Al)<br />

process with 173.82mm2 die area. For low-voltage low-power and high-frequency operation,<br />

half-frequency read-latency control, hybrid IOSA, and segmented sub-array architecture are<br />

developed. Standby currents are reduced by 63% and operating currents are reduced by 54%<br />

with tRCD of 9.8ns and tAA of 10.4ns.<br />

7.2 8Gb 3D DDR3 DRAM Using Through-Silicon-Via Technology<br />

9:00 AM<br />

U. Kang, H-J. Chung, S. Heo, S-H. Ahn, H. Lee, S-H. Cha, J. Ahn, D. Kwon, J-H. Kim, J-W. Lee,<br />

H-S. Joo, W-S. Kim, H-K. Kim, E-M. Lee, S-R. Kim, K-H. Ma, D-H. Jang, N-S. Kim, M-S. Choi,<br />

S-J. Oh, J-B. Lee, T-K. Jung, J-H. Yoo, C. Kim<br />

Samsung Electronics, Hwasung, Korea<br />

An 8Gb 4-stack 3D DDR3 DRAM with through-silicon-via (TSV) is presented that decreases the<br />

standby power by 50% and active power by 25%, and increases the I/O speed to 1600Mb/s. The<br />

TSV check and repair scheme increases the assembly yield from 15% to 98%. By providing<br />

extra power pads, power noise is reduced to 100mV even if all 4 ranks are refreshed.<br />

7.3 A 1.35V 4.3GB/s 1Gb LPDDR2 DRAM with Controllable Repeater and On-the-Fly<br />

Power-Cut Scheme for Low-Power and High-Speed Mobile Application<br />

9:30 AM<br />

B-H. Jeong, J. Lee, Y-J. Lee, T-J. Kang, J-H. Lee, D-H. Hong, J-H. Kim, E-R. Lee, M-C. Kim,<br />

K-H. Lee, S-I. Park, J-H. Son, S-K. Lee, T-W. Kwon, J-H. Ahn, Y-T. Kim<br />

Hynix Semiconductor, Icheon, Korea<br />

A 1.35V 4.3GB/s 1Gb LPDDR2 DRAM with controllable repeater and on-the-fly power-cut<br />

scheme is fabricated in a 66nm process. The DRAM is targeted for low-power and high-speed<br />

mobile applications. The global I/O lines are optimized with a GIO repeater scheme to overcome<br />

the high loading. The data bandwidth is 1066Mb/s/pin with associated maximum power<br />

consumption of 110mW.<br />

Break 10:00 AM<br />

7.4 A 75nm 7Gb/s/pin 1Gb GDDR5 Graphics Memory Device with Bandwidth-Improvement<br />

Techniques<br />

10:15 AM<br />

R. Kho, D. Boursin, M. Brox, P. Gregorius, H. Hoenigschmid, B. Kho, S. Kieser, D. Kehrer,<br />

M. Kuzmenka, U. Moeller, P. Petkov, M. Plan, M. Richter, I. Russell, K. Schiller, R. Schneider,<br />

K. Swaminathan, B. Weber, J. Weber, I. Bormann, F. Funfrock, W. Spirkl, H. Steffens, J. Weller,<br />

T. Hein, M. Gjukic<br />

Qimonda, Neubiberg, Germany<br />

A 1Gb GDDR5 DRAM is fabricated in a conventional 75nm DRAM process. To improve existing<br />

data transfer rates, we implement a boosting transmitter to open the data eye by 100mV, and a<br />

high-speed multiple-domain internal VINT power-generator system to limit on-chip power noise in<br />

critical blocks to 10mV. A data-transfer rate of 7Gb/s/pin is achieved with a 1.5V supply.<br />

32