MicroBlaze Processor Reference Guide (UG081) - Xilinx

MicroBlaze Processor Reference Guide (UG081) - Xilinx

MicroBlaze Processor Reference Guide (UG081) - Xilinx

You also want an ePaper? Increase the reach of your titles

YUMPU automatically turns print PDFs into web optimized ePapers that Google loves.

Chapter 2: <strong>MicroBlaze</strong> Architecture<br />

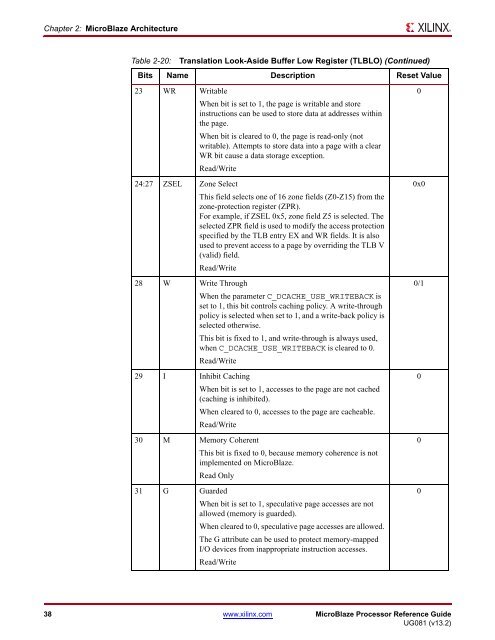

Table 2-20: Translation Look-Aside Buffer Low Register (TLBLO) (Continued)<br />

Bits Name Description Reset Value<br />

23 WR Writable<br />

When bit is set to 1, the page is writable and store<br />

instructions can be used to store data at addresses within<br />

the page.<br />

When bit is cleared to 0, the page is read-only (not<br />

writable). Attempts to store data into a page with a clear<br />

WR bit cause a data storage exception.<br />

Read/Write<br />

24:27 ZSEL Zone Select<br />

This field selects one of 16 zone fields (Z0-Z15) from the<br />

zone-protection register (ZPR). <br />

For example, if ZSEL 0x5, zone field Z5 is selected. The<br />

selected ZPR field is used to modify the access protection<br />

specified by the TLB entry EX and WR fields. It is also<br />

used to prevent access to a page by overriding the TLB V<br />

(valid) field.<br />

Read/Write<br />

28 W Write Through<br />

When the parameter C_DCACHE_USE_WRITEBACK is<br />

set to 1, this bit controls caching policy. A write-through<br />

policy is selected when set to 1, and a write-back policy is<br />

selected otherwise.<br />

This bit is fixed to 1, and write-through is always used,<br />

when C_DCACHE_USE_WRITEBACK is cleared to 0.<br />

Read/Write<br />

29 I Inhibit Caching<br />

When bit is set to 1, accesses to the page are not cached<br />

(caching is inhibited).<br />

When cleared to 0, accesses to the page are cacheable.<br />

Read/Write<br />

30 M Memory Coherent<br />

This bit is fixed to 0, because memory coherence is not<br />

implemented on <strong>MicroBlaze</strong>.<br />

Read Only<br />

31 G Guarded<br />

When bit is set to 1, speculative page accesses are not<br />

allowed (memory is guarded).<br />

When cleared to 0, speculative page accesses are allowed.<br />

The G attribute can be used to protect memory-mapped<br />

I/O devices from inappropriate instruction accesses.<br />

Read/Write<br />

38 www.xilinx.com <strong>MicroBlaze</strong> <strong>Processor</strong> <strong>Reference</strong> <strong>Guide</strong><br />

<strong>UG081</strong> (v13.2)<br />

0<br />

0x0<br />

0/1<br />

0<br />

0<br />

0